1.1 uart协议

uart(universal asynchronous reciver and transmitter):通用异步收发器,是一种通用串行数据总线,用于异步通信,将数据的二进制位一位一位的进行传输。该总线双向通信,可以实现全双工传输(rxd txd可同时工作)和接受。

在学习uart之前有必要了解几个基础的数字通信概念

同步通信和异步通信

1:发送方和接收方按照同一个时钟节拍工作就叫同步;发送方和接收方按照自己的节拍工作就叫异步。

2:同步通信中,通信双方按照统一节拍工作,所以配合很好;一般需要发送方给接收方发送信息同时发送时钟信号,接收方根据发送方给它的时钟信号来安排自己的节奏。同步通信用在通信双方信息交换频率固定,或者经常通信时。

3:异步通信又叫异步通知。在双方通信的频率不固定时(有时3ms收发一次,有时3天才收发一次)不适合使用同步通信,而适合异步通信。异步通信时接收方不必一直在意发送方,发送方需要发送信息时会首先给接收方一个信息开始的起始信号,接收方接收到起始信号后就认为后面紧跟着的就是有效信息,才会开始注意接收信息,直到收到发送方发过来的结束标志。。

电平信号和差分信号

1、电平信号和差分信号是用来描述通信线路传输方式的,即如何在通信线路上表达1和0。

2、电平信号的传输线中有一个参考电平线(一般是GND),然后信号线上的信号值是由信号线电平和参考电平线的电压差决定。

3、差分信号的传输线中没有参考电平,所有都是信号线,1和0的表达依靠信号线之间的电压差。

4、电平信号的2根通信线之间的电平差异容易受到干扰,传输容易失败;差分信号不容易受到干扰因此传输质量比较稳定,现代通信一般都使用差分信号。

并行接口和串行接口

1、串行、并行主要是考虑通信线的根数,就是发送方和接收方同时可以传递的信息量的多少 ;2、譬如在电平信号下,1根参考电平线+1根信号线可以传递1位二进制;如果我们有3根线(2根信号线+1根参考线)就可以同时发送2位二进制;如果想同时发送8位二进制就需要9根线。在差分信号下,2根线(彼此差分)可以同时发送1位二进制;如果需要同时发送8位二进制,需要16根线。

3、似乎并行接口比串行接口要快(串行接口一次只能发送1位二进制,而并行接口一次可以发送多位二进制)要更优秀;但是实际上串行接口才是王道,用的比较广。因为更省信号线,而且对传输线的要求更低、成本更低;而且串行时可以通过提高通信速度来提高总体通信性能,不一定非得要并行。经过这么多年发展,最终胜出的是:异步、串行、差分,譬如USB和网络通信。

4、串口通信时因为是异步通信,所以通信双方必须事先约定好通信参数,这些通信参数包括:波特率、数据位、奇偶校验位、停止位(串口通信中起始位定义是唯一的,所以一般不用选择)

波特率

(1)波特率(bandrate),指的是串口通信的速率,也就是串口通信时每秒钟可以传输多少个二进制位。

譬如每秒种可以传输9600个二进制位(传输一个二进制位需要的时间是1/9600秒,也就是104us),波特率就是9600。

(2)串口通信的波特率不能随意设定,而应该在一些值中去选择。

一般最常见的波特率是9600或者115200(低端单片机如51常用9600,高端单片机和嵌入式SoC一般用115200)。

为什么波特率不可以随便指定?第一,通信双方必须事先设定相同的波特率这样才能成功通信,如果发送方和接收方按照不同的波特率通信则根本收不到,因此波特率最好是大家熟知的而不是随意指定的。第二,常用的波特率经过长久发展,就形成了共识,大家常用就是9600或者115200。

1.1.1 uart协议要点

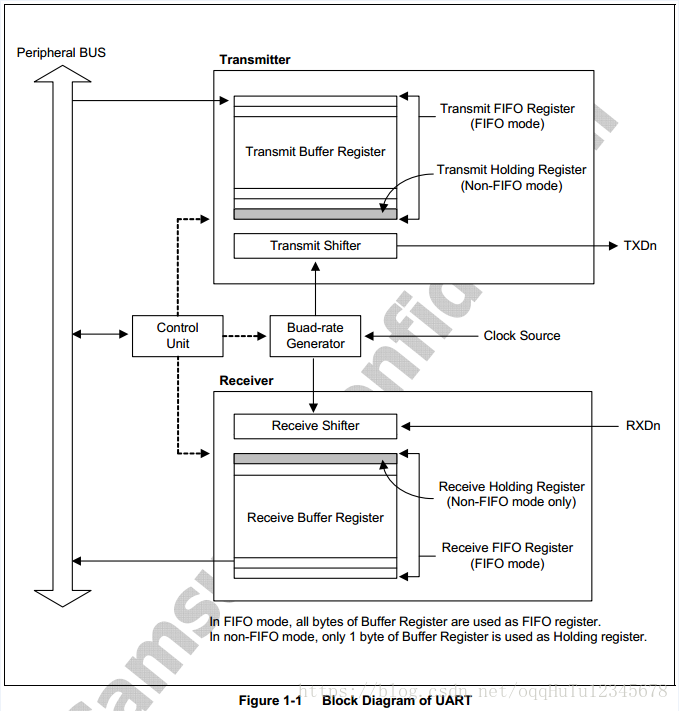

(1)UART由波特率产生器、UART接收器、UART发送器组成。

(2)由三条信号线组成:RX、TX、GND

(3)UART包括RS232、RS499、RS423、RS422和RS485等接口标准规范和总线标准规范。它们的主要区别在于其各自的电平范围不相同。 嵌入式设备中常常使用到的是TTL、TTL转RS232的这种方式。

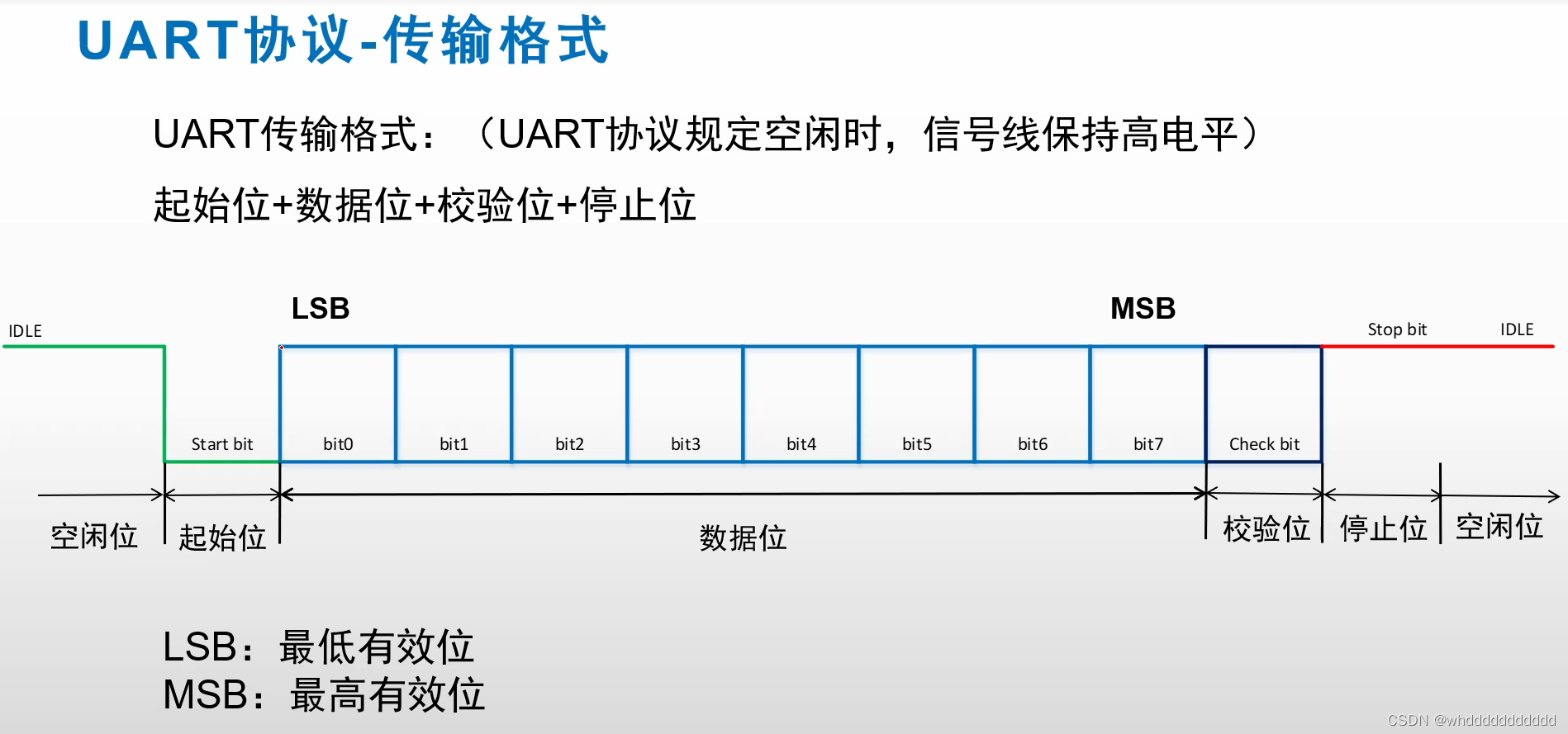

1.1.2 uart通信协议

(1)起始位:先发出一个逻辑”0”的信号,表示传输字符的开始。

(2)数据位:紧接着起始位之后。数据位的个数可以是4、5、6、7、8等,构成一个字符。通常采用ASCII码。

(3)奇偶校验位:数据位加上这一位后,使得“1”的位数应为偶数(偶校验)或奇数(奇校验),以此来校验资料传送的正确性。

(4)停止位:它是一个字符数据的结束标志。可以是1位、1.5位、2位的高电平。

(5)空闲位:处于逻辑“1”状态,表示当前线路上没有资料传送。

(6)波特率:数据传输的速率。有以下几个档位:300、600、1200、2400、4800、9600、19200、38400、43000、56000、57600、115200。在数据传输和接收双方,需要预先统一波特率,以便正确的传输数据。

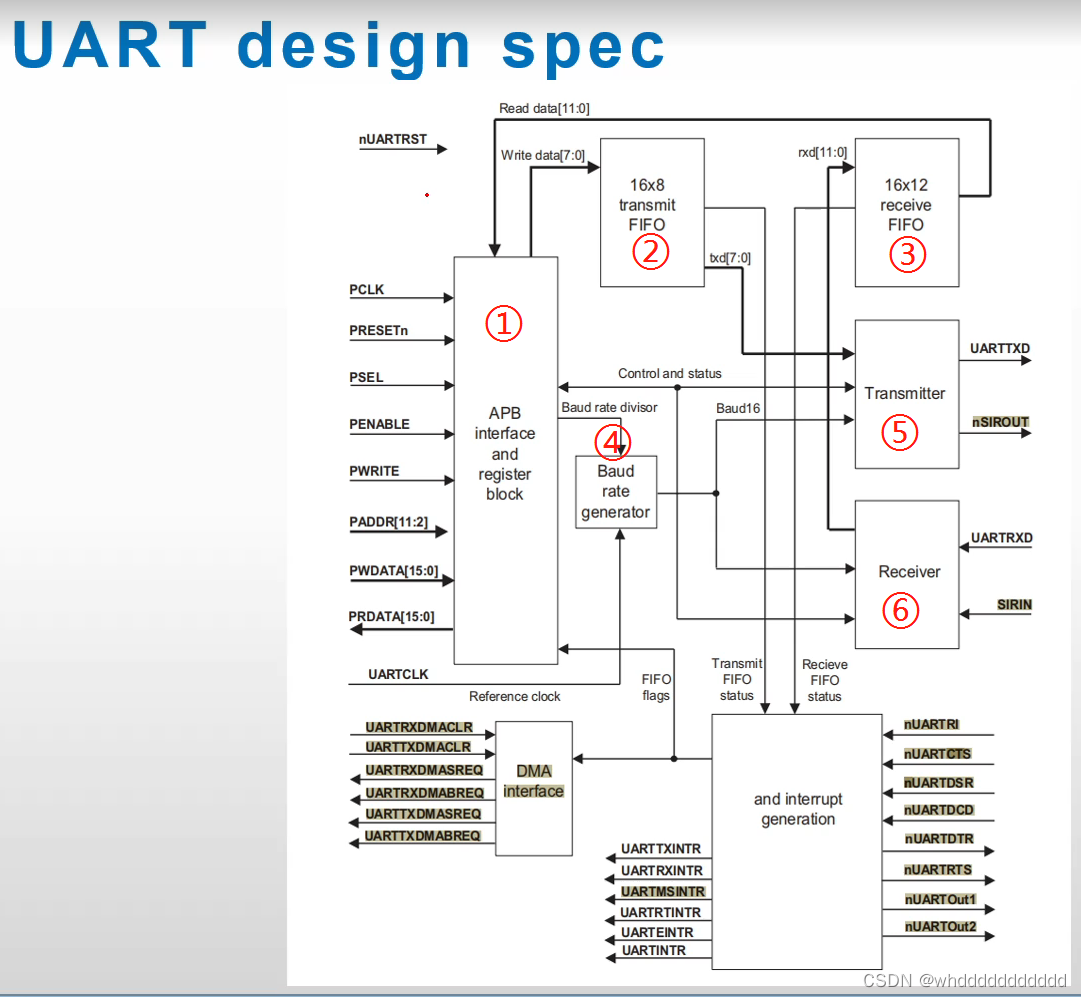

1.2 uart design spec

1.2.1 模块介绍

①apb interface and register block是一个interface外部通信模块和寄存器模块,interface外部通信模块与一个apb uvc连接,将apb产生的并行数据写入②fifo中,寄存器模块进行内部的各种设置,包括④波特率产生设置,⑤transmitter ⑥receiver具体的uart协议中控制信号,状态信号的设置

②transmit fifo是一个8位宽,16位深度的内存缓冲区,存贮从①apb interface and register block写入的数据,放进16×8的transmit fifo,

⑤transmitter 具有将数据并行转串行并将写入数据按照uart协议中规定的起始位,数据位,奇偶校验位,停止位输出的一个功能

③receive fifo是一个12位宽,16位深度的内存缓冲区,存储从①apb interface and register block中读出的⑥receiver写入的数据,放进16×8的receive fifo

④波特率产生根据参考时钟与寄存器中对波特率的设置来规定系统波特率,参考时钟波特率一般比较大,类似于分频

⑥receiver具有将数据并行转串行并将写入数据按照uart协议中规定的起始位,数据位,奇偶校验位,停止位输出的一个功能

⑤transmitter ⑥receiver与uart uvc连接,⑤transmitter 连接uart模块的passive agent,⑥receiver连接uart模块的active agent

系统分为写入数据方向rx与读数据tx方向,rx方向为cpu通过①apb interface and register block写入并行数据,存入②transmit fifo中,在⑤transmitter中经过并行转串行uart协议,加上起始位,校验位,停止位后输出串行数据流; tx方向从⑥receiver收到串行数据,检查对比收到数据与寄存器设置的数据之后将起始位,校验位,停止位剥离,转换为并行数据流,将数据位存储到③receive fifo中,通过①apb interface and register block将③receive fifo中储存的数据按先进先出的原则读走。

1.2.2 接口信号

其中需要注意,paddr 地址低两位force为0,默认为0,即地址以0.4.8.12 4bit进行变化

pwdata 与prdata都为16位,数据存入小端,支持扩展到32bit

上述为uart待测模块的接口信号

版权声明:本文为CSDN博主「whddddddddddd」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/whddddddddddd/article/details/125091050

77

77

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?