一、需求

1.通过AXI STREAM完成一个PS->PL->PS的传输链路,其中PL端自定义的IP核是流水线处理的,因此需要输入到IP核中的数据是连续的有效数据。

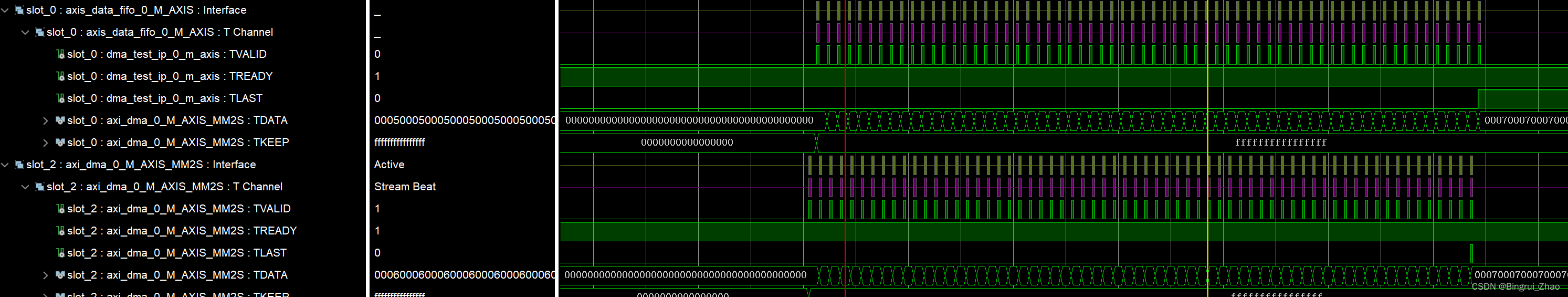

2.我们平时常用的传输位宽是32或64这种较小的位宽。而此次输入到IP核的数据是512位的,即AXI STREAM的传输位宽是512。这就会导致AXI的Burst Size变小(位宽越大,Burst Size越小,反之一样),进一步的,Burst Size变小,导致DMA在传输过程时出现传一些数据后,停顿一段时间,再继续传输一部分数据,再停顿,再传输一部分数据,再停顿……这样的不连续传输情况,如下图所示。

在上图中,在TLAST拉高前,TVALID间断性的拉低和拉高。在TVALID为高时才有数据在传输,TVALID为低时没有数据传输。这表示在一次DMA中传输中,分了几十次传输过程(是否可以理解为发生了几十次的Burst过程?),数据传输过程是不连续的。

在上图中,在TLAST拉高前,TVALID间断性的拉低和拉高。在TVALID为高时才有数据在传输,TVALID为低时没有数据传输。这表示在一次DMA中传输中,分了几十次传输过程(是否可以理解为发生了几十次的Burst过程?),数据传输过程是不连续的。

二、解决方案

首先想到的是在AXI DMA和自定义IP核间插入AXI STREAM DATA FIFO。PS端不连续的数据进入FIFO后,经过缓存再将连续数据流入到自定义IP核中,这样IP核收到的数据就是连续的。但是经过实验发现几乎没有变化,因为FIFO存一个数就发一个数,这与未插入FIFO时的情况一致。

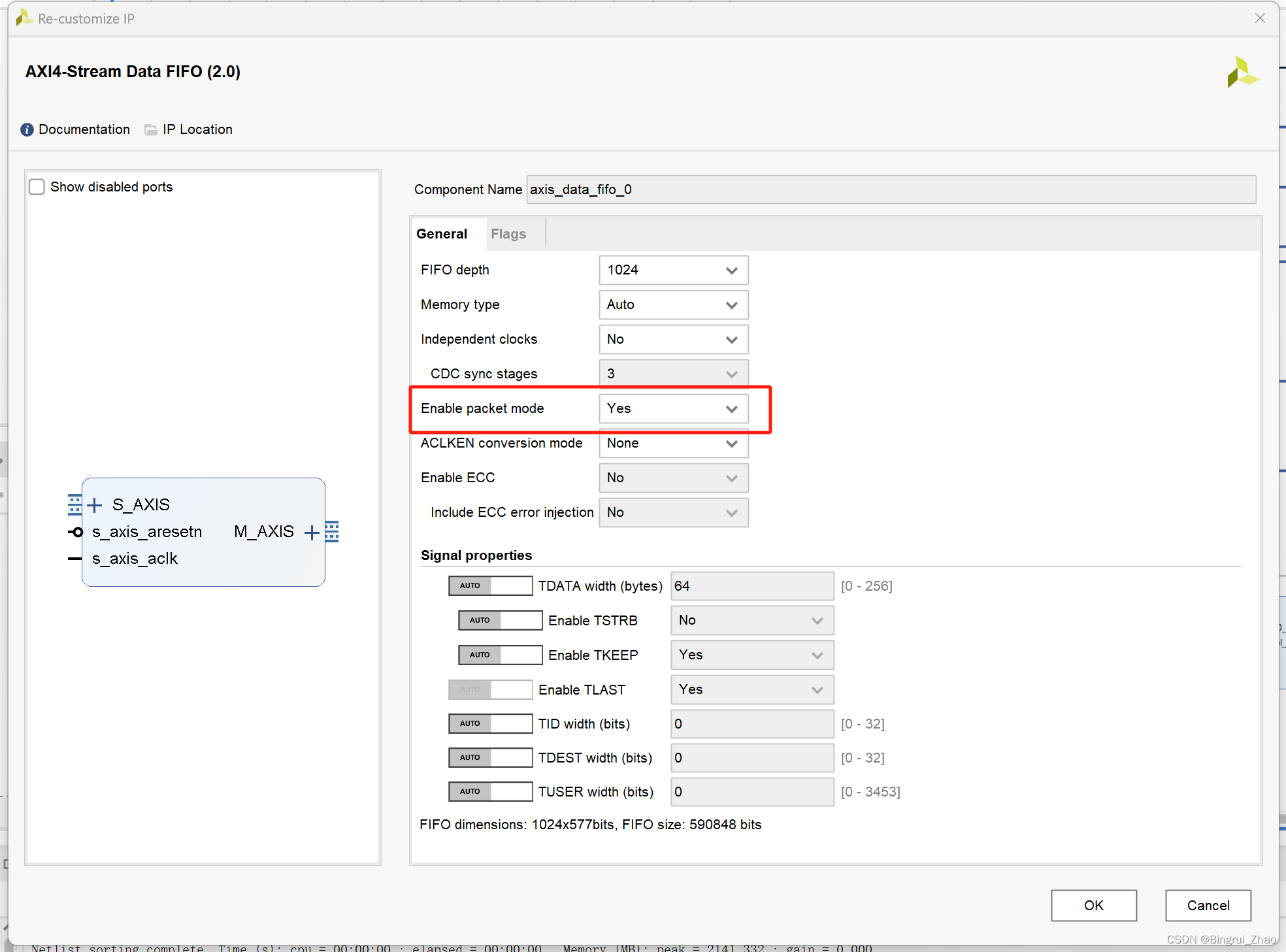

进一步查阅资料,发现AXI STREAM DATA FIFO这个IP核中有一个Enable Packet Mode选项,使能该选项后,输入到FIFO的数据会先缓存,等待TLAST信号到达后,才从FIFO输出。这样,FIFO在输出数据前,缓存了一个完整的数据包,再输入到自定义IP核中就是连续的了。

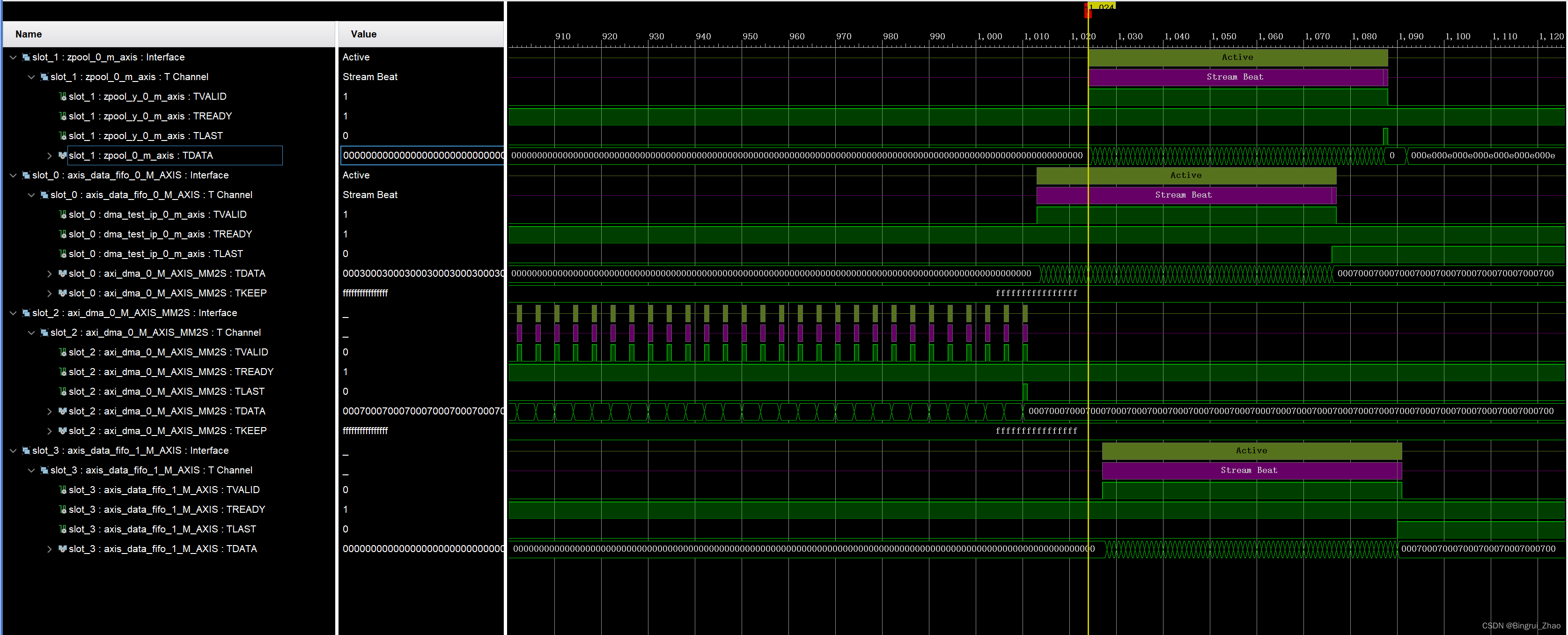

时序如下图所示。

此时,完整传输过程中的逻辑如下:

1.PS->AXIS_FIFO_0 不连续

2.AXIS_FIFO_0 ->自定义IP核 连续

3.自定义IP核 ->AXIS_FIFO_1 连续

4.AXIS_FIFO_1 -> PS 连续

可以看出,与自定义IP核相关的传输过程都是连续的,这就能够满足需求了。

此外,使能Enable Packet Mode后由于等待TLAST信号的原因,整体的传输速度会被牺牲一些,具体传输速度的下降还未测试。

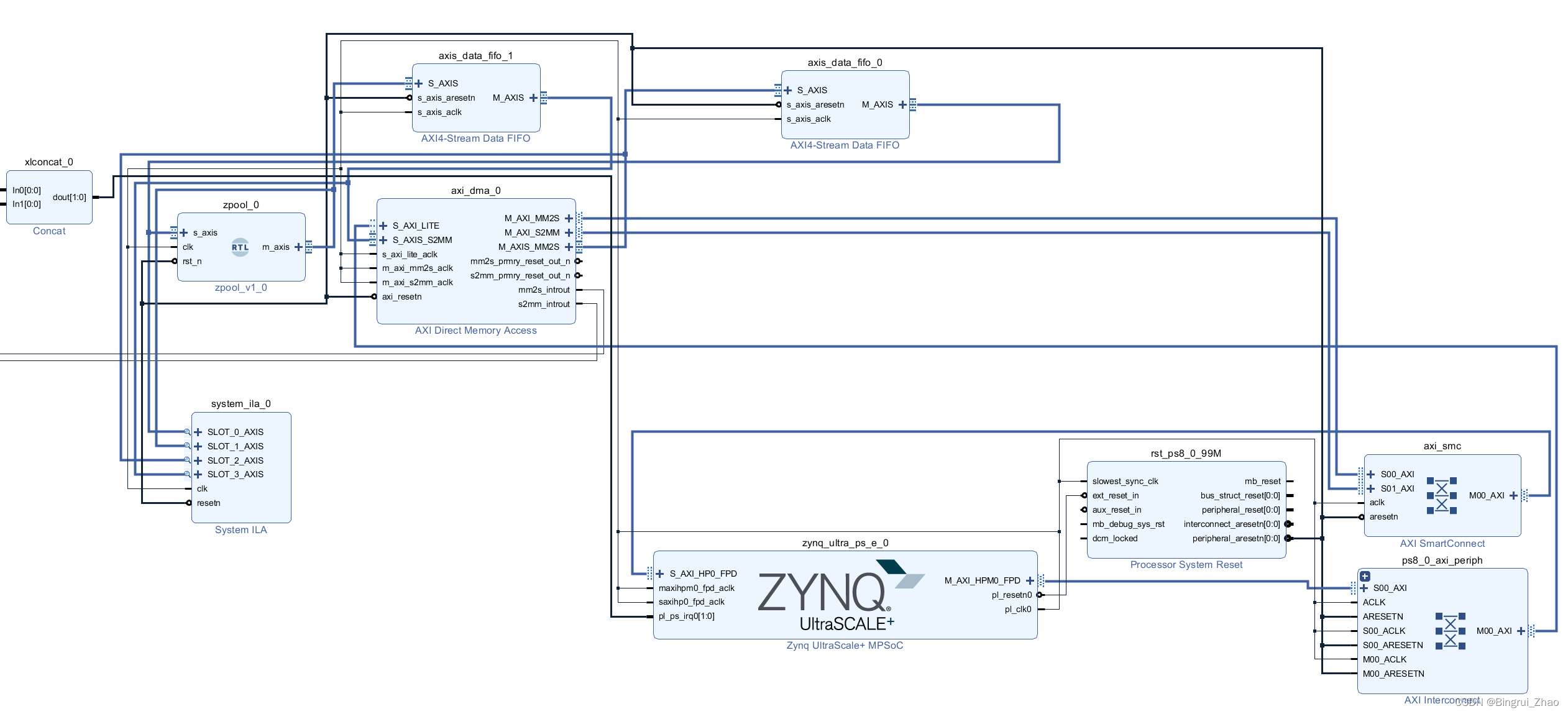

整体Block Design如下图所示,zpool是自定义的IP核。

三、总结

大位宽时AXI STREAM的传输不连续问题,可以通过插入FIFO并使能Enable Packet Mode进行解决。上面的讨论不一定准确,仅供参考。

文章讲述了在大位宽(512位)AXISTREAM传输中遇到的不连续问题,通过在AXIDMA和自定义IP核间插入AXISTREAMDATAFIFO并启用PacketMode,实现连续数据传输。虽然牺牲了部分传输速度,但能满足连续输入需求。

文章讲述了在大位宽(512位)AXISTREAM传输中遇到的不连续问题,通过在AXIDMA和自定义IP核间插入AXISTREAMDATAFIFO并启用PacketMode,实现连续数据传输。虽然牺牲了部分传输速度,但能满足连续输入需求。

3891

3891

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?