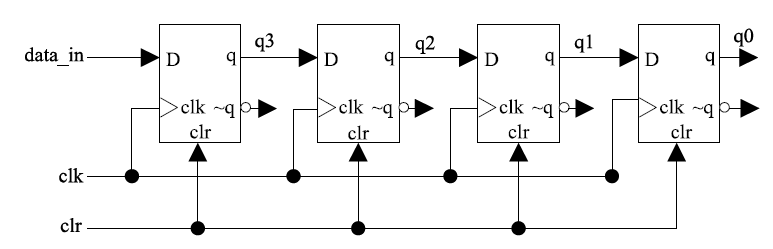

verilog HDL在硬件描述方面具有非常显著的优点,它效率高,灵活性强,可以直观的把电路原理图转化为RTL代码,下面举一个移位寄存器的例子:

从图中可以看到clr信号(其实大多数时候我们是叫它reset信号)与clk信号“分而治之”,不管clk信号边沿是否到来,只要来了有效clr信号,寄存器就会进入复位状态。从图中可知,clr信号在低电平时触发复位,代码实现如下:

module ShiftRegister4(q3,data_in,clk,clr);

output[3:0] qout;

input data_in;

input clk;

input clr;

reg[3:0] qout; //

always@(posedge clk or negedge clr)

if (!clr)

begin

qout <= 4'b0000;

end

else

begin

qout[3:0] <= {qout[3:1], data_in};

//右移寄存器,取寄存器前三位拼接上刚进来的data_in就可以啦

end

endmodule如果我们想实现8位移位寄存器或者别的位数怎么办呢?很简单,把代码里qout[3:0]改成[7:0](or any number u want~)就可以啦

另外推荐一个网站,在HDLBits上就可以刷题,移位寄存器也是在滴,来瞅瞅

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

9324

9324

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?