AMBA(Advanced Microcontroller Bus Architecture,高级微控制器总线结构)定义了嵌入式微处理器的通信标准,可以将RISC系列处理器集成在FPGA,ASIC的集成环境当中用于构建SOC系统,是ARM公司提出的开放性的片上总线标准,它是用来连接芯片内核和集成环境当中其他元件的连接线,并非芯片或者SOC与外部连接的接口,其具有高速度低功耗等特点。

根据AMBA总线的发展主要分为以下总线协议:

| AHB | ASB | APB | AXI |

AHB高级高性能总线,通常用于CPU和高性能设备之间的交互,其可以连接微处理器,芯片上或芯片外的内存模块和DMA等高效率模块;

ASB常用于高性能系统模块间的交互,在实际使用中和其他的总线协议相比,并不是太常用;

APB高级外设总线,通常用于外挂低速外设,比如UART,SPI,TIMER,KEY,BOTTLE等低速外设;

AXI高级可拓展总线是一种面向高性能、高带宽、低延迟的片内总线,现在常用来在FPGA中当作高性能总线,支持突发传输,具有双向握手协议,读写地址分离,能够支持初始延迟较高的外设,连线较多;

| 总线 | AXI | AHB | APB |

| 总线宽度 | 8、16、32、64、128、256、512、1024 | 32、64、128、256 | 8、16、32 |

| 地址宽度 | 32 | 32 | 32 |

| 通道特性 | 读写地址通道,读写数据通道均独立 | 读写地址通道共用,读写数据通道分离 | 读写地址通道公用,读写数据通道分离 |

| 体系结构 | 多主/从设备,含仲裁机制 | 多主/从设备,含仲裁机制 | 单主设备/多从设备,无仲裁机制 |

| 数据协议 | 支持流水/分裂传输 支持猝发传输 支持乱序访问 字节/半字/字 大小端对齐 非对其操作 | 支持流水/分裂传输 支持猝发传输 支持乱序访问 字节/半字/字 大小端对齐 不支持非对其操作 | 一次读/写传输占两个时钟周期 不支持突发传输 |

| 传输方式 | 支持读写并行操作 | 不支持读写并行操作 | 不支持读写并行操作 |

| 时序 | 同步 | 同步 | 同步 |

| 互联 | 多路 | 多路 | 无定义 |

AHB总线的组成:

Master:能够发起读写操作,提供地址和控制信号,同一时间只有一个master被激活。

Slave:给定的范围内对读写操作作相应,并对Master返回成功,失败或者等待状态。

Arbiter:仲裁,在多个Master要响应时进行仲裁,保证只有一个Master在工作,仲裁协议是规定的,但是仲裁算法可以根据应用决定。

Decoder:负责对地址进行译码,提供片选信号到各Slave。

所有的AHB都需要一个仲裁其一个中央解码器。

AHB的传输分为两个阶段:地址周期,只有一个cycle,数据周期,由HREADY信号决定需要几个cycle,采用流水线传送:先是地址周期,然后是数据周期;

AHB和AXI都支持Burst突发传输,但两者存在差异,在AHB总线的突发传输协议中,AHB需要一次突发传输的所有地址,地址和数据需要对应,后一次传输需要在前一次传输完成后才能进行。

但AXI线只需要一次突发的首地址,一个首地址后面跟着多个数据,后面多个数据的地址自动在首地址后面递增,而且在传输过程中,可以连续发好几个首地址,然后所有数据交错传递,利用该特征可以大大提供总线利用率。

AHB总线和AXI总线都适用与高性能,高带宽的SOC系统,但AXI线更加灵活,AXI支持乱序传输,提高SOC系统的灵活性,读写通道可以并行传输,多个数据可以交错传递,所以在目前的SOC系统中大多以AXI线为主。

APB总线主要应用在低带宽的外设上,比如UART,SPI,I2C,KEY,BOTTLE等,APB的架构没有多主设备一说,总线的唯一主设备就是APB桥,有AHB2APB的桥,也有AXI2APB的桥,也有AXI2AHB的桥,具体使用时可以根据所需具体使用,APB总线架构不需要仲裁器和,在读写上不遵从流水的形式,读和写只需要2个周期,其控制逻辑较为简单用一个状态机即可说明;

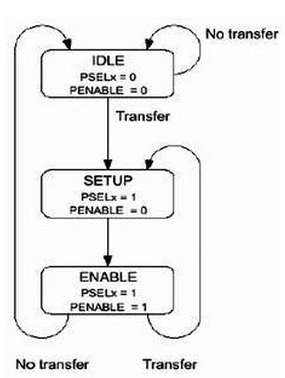

系统初始化位IDLE状态,没有任何传输操作,也没有选中任何从模块。

传输进行时,PSELx=1,PENABLE=0,系统进入SETUP,并只会停留一个周期,PCLK上升沿到来系统进入ENABLE状态。

系统进入ENABLE状态,维持SETUP,PSEL,PWRITE不变,并将PENABLE置1,传输只会在ENABLE状态维持一个周期,经过SETUP与ENABLE状态之后就已经完成传输,如果没有传输要进行,就进入IDLE状态等待,如果有连续的传输,则会进入SETUP状态。

1、APB:高级外围设备总线(APB)用于连接低带宽的外围设备。它是一个简单的非流水线协议。读写操作共享同一组信号,不支持burst数据传输。最新的规范(APB2.0)可以在ARM网站上找到,是最容易学习的AMBA 协议。

2、AHB:高级高性能总线(AHB)用于连接共享总线上需要更高带宽的组件。这些slave组件可以是内部内存或外部内存接口、DMA、DSP等。AHB可以通过burst数据传输来获得更高的带宽。

3、AHB-lite协议是AHB的一个简化版本。简化后只支持一个主设计,这消除了对任何仲裁、重试、分割事务等的需求。

4、高级可扩展接口(AXI)适合于高带宽和低延迟互连。这是一个点对点的互连,并克服了AHB、APB等共享总线协议在可连接的代理数量方面的限制性。该协议支持多个outstanding 的数据传输、burst数据传输、单独的读写通道和支持不同的总线宽度。

5、AXI-lite协议是AXI的简化版本,简化后不支持突发数据传输。

6、AXI-stream 协议是AXI协议的另一种风格,它只支持数据流从master 流到slave。与完整的AXI或AXI-lite不同,AXI-stream 协议中没有单独的读/写通道,因为其目的是只在一个方向上流。

7、ACE-AXI协议是AXI4协议的扩展,应用于在一个芯片上集成多个CPU核心与一致性cache的场景。ACE协议扩展了AXI读写数据通道,同时引入了单独的snoop 地址、snoop 数据和snoop 响应通道。这些额外的通道提供了实现基于snoop 的一致性协议的机制。

8、ACE-Lite—对于没有自己cache的agents ,但仍属于可共享一致性域的一部分,如DMA或网络接口agent,使用ACE-lite协议实现这种“单向”一致性。

9、CHI—ACE协议作为AXI的扩展而开发,以支持一致性互连。ACE协议使用了master/slave之间的信号电平通信,因此互连需要大量的线和增加的通道来进行snoops 和响应。这对于具有2/4核移动SOC 的小一致性clusters非常有效。随着SOC上集成越来越多的一致性clusters ——AMBA5修订版引入了CHI协议。CHI协议使用基于分层分组的通信协议,具有协议、链路层和物理层实现,还支持基于QoS的流控制和重试机制。

概述是我们深入地了解这些协议的开始,进一步了解的最好方法是阅读规范,以了解每个协议的细节。APB和AHB相对简单,而且很容易学习。AXI和ACE/CHI相对复杂,需要详细阅读,以及了解缓存一致性和一般通信协议的基本知识。

1756

1756

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?