通常在一个SOC设计当中,或者任何一个工程项目当中,一般是很少用到单频时钟的,经常会用到分频时钟处理,经典的面试题中也有占比50%的三分频时钟设计;

奇数分频时钟,50%占空比时钟处理方法:

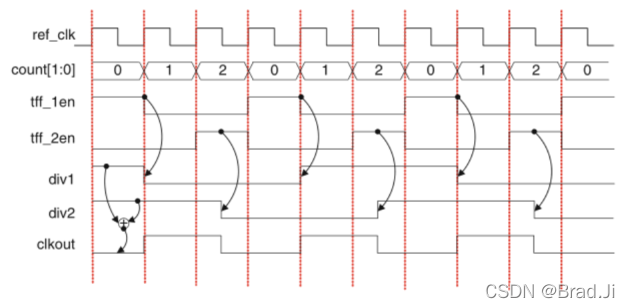

对使用奇数分频整除得到50%占空比的波形图如下图所示:

其步骤就是:1.创建一个计数器,计数器从0到N-1,并且时钟在时钟的上升沿计时。

2.采用两个切换触发器,按如下方式启动:

tff_1en:使能在当计数器为0时;

tff_2en:使能在当计数器为(N+1)/2,比如在3的时候就是2,在5的时候就是3;

3.生成以下两个始终正交的两个信号:

div1:当tff_1en使能为高,并且在参考时钟的上升沿触发;

div2:当tff_2en使能为高,并且在参考时钟的下降沿触发;

此时生成的两个分频时钟波形是对于参考时钟的频率除以2N的;

4.对生成的始终正交的两个分频时钟做异或运算,最终生成目的时钟,目的时钟的频率是clk/N;

非50%占空比时钟处理方法:

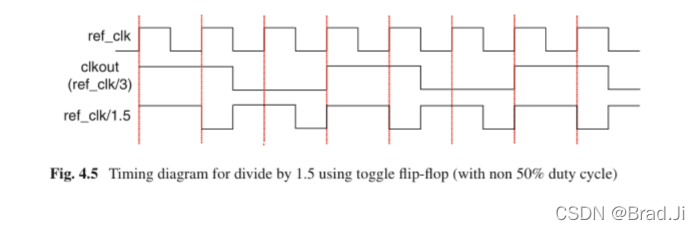

不是一半占空比就是指多个参考时钟有一半以上高低电平时间不对称的波形,比如下图的1.5

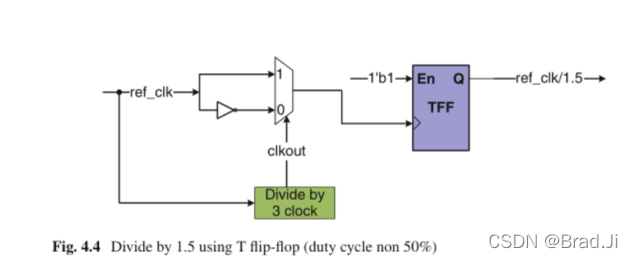

这个1.5中就是每3个参考时钟中包含两个对称脉冲,其对应到电路图就是这个

利用clkout的一个三倍分频的时钟去做SEL,但是这种情况也会出现问题具体在电路实现中,试想Clk_out是一个频率变换较快的分频时钟,那么走线和组合逻辑会带来很大的延时导致出现亚稳态。

对于实现一个时钟除以4.5的时钟实现(非50%的占空比)

除以4.5意味着每九个参考时钟里面将包含两个对称脉冲时钟;

以下就是按非整数除法列出的顺序步骤:

1.取一个九位的移位寄存器,该移位寄存器在复位后的初始化为9’b000000001,该移位寄存器在每当时钟上升沿的时候左移。

2.要产生第一个脉冲序列,该脉冲序列针对移位寄存器的第1bit和第2bit,该脉冲的翻转在移位寄存器的第一个Bit翻转后的半个时钟周期后,也就是在第一个下降沿和第二个席间沿翻转,同时对以上三个bit量进行OR运算,得到的就是分频器的第一个高电平。

3.产生第二个和第三个脉冲序列,该脉冲序列针对移位寄存器的第5bit和第6Bit,第二个脉冲序列在移位寄存器的第五位反转后的半个周期后变换,第三个脉冲序列在移位寄存器的第六位翻转后的半个周期变换,用组合逻辑将第二个和第三个脉冲序列与移位寄存器的第六bit做OR运算,得到的就是分频器分频后的第二个高电平。

1290

1290

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?