原文标题:An ultralow loss 4H-SiC double trenches MOSFET with integrated heterojunction diodes and split gate

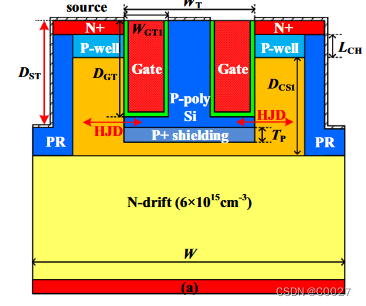

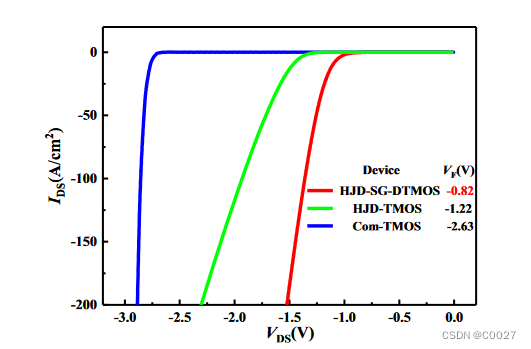

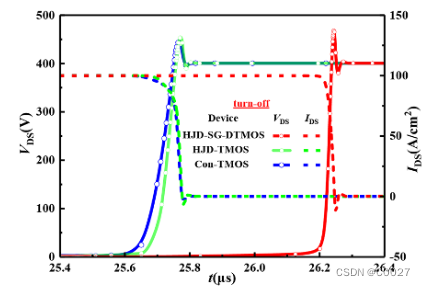

****摘要:****介绍了一种新型超低损耗 4H-SiC 双沟槽 MOSFET,并对其机理进行了仿真研究。该器件具有两个集成异质结二极管(HJD),由 P 型多晶硅和碳化硅、沟道分离栅极(SG)和源极沟道下的 P+ 区(PR)组成。SG 和 PR 可降低栅极和漏极之间的耦合效应,并将部分栅-漏电容 (CGD) 转化为栅-源电容 (CGS) 和漏-源电容 (CDS)。与传统沟槽 MOSFET(Con-TMOS)和 HJD 沟槽 MOSFET(HJD-TMOS)相比,所提出的集成了 HJDs 和 SG 的双沟槽 MOSFET(HJD-SG-DTMOS)可将 CGD 分别降低 83% 和 89%。此外,集成的 HJD 取代了寄生体二极管作为续流二极管,从而降低了反向导通电压。因此,与 Con-TMOS 和 HJD-TMOS 相比,拟议器件的反向导通电压不仅分别降低了 69% 和 33%,而且开关损耗也分别降低了 64% 和 49%。

研究背景:SiC MOSFET器件与Si基器件相比,存在体二级关开启电压高的问题,现有解决方案为在器件中集成反向并联的SBD作为续流二极管。但该结构仍然存在一定的问题,表现在:SBD 受镜像力效应和隧道效应的影响较大,会产生较大的反向漏电流;此外,SBD 的制造可能会对栅极氧化物造成金属化污染,导致阈值电压不稳定和 BV 性能下降等一系列问题 。

创新点:集成异质结二极管的分离栅DTMOSFET

HJD 具有类似于 SBD 的单极工作特性,能有效降低体二极管的空穴注入效率,因此该器件具有良好的反向恢复特性。双屏蔽区域改善了 N-drift 区域的电场分布,保护了栅极氧化物和 HJD,防止过早击穿。p+屏蔽区及PR的共同作用使得CSL有望实现更高的掺杂浓度,进一步减小器件的比导通电阻。

此外PR提供了更强的耗尽效应,从而使Cgd得以进一步降低,也可以认为在PR与SG结构共同作用下,部分栅漏电容被转化为栅源电容,这体现在开关特性测试中延迟时间的增长,见下图。

HJD-SG-MOSFET并联了两个异质结二极管,因此其反向导通电压低于HJD-MOSFET(why)

本文中,总的来看器件设计的出发点还是对器件可靠性等静态问题出发,并没有去专门针对器件的开关特性进行特殊的设计。

5172

5172

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?