原题目:A split-gate SiC trench MOSFET with embedded unipolar diode for improved performances

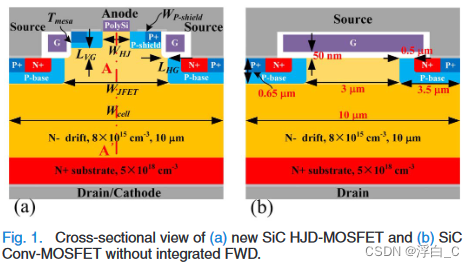

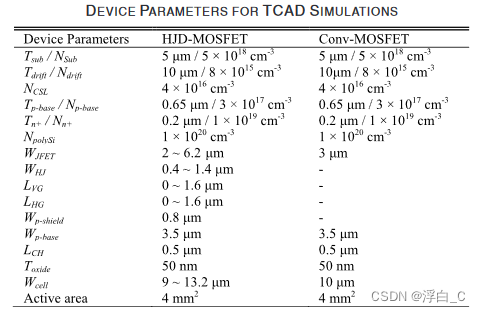

Numerical Study of SiC MOSFET With Integrated n-/n-Type Poly-Si/SiC Heterojunction Freewheeling Diode

摘要:两篇文章出发点都是为避免SiC MOSFET器件的体二极管导通电压较大从而导致的双击退化等问题而提出的新的SiC MOSFET器件结构。其一为SiC JBS-MOSFET结构的进一步改进,其二为集成“单极管”的SiC MOSFET结构,可以视为在SGT与DT结构基础上的改进。

器件结构:

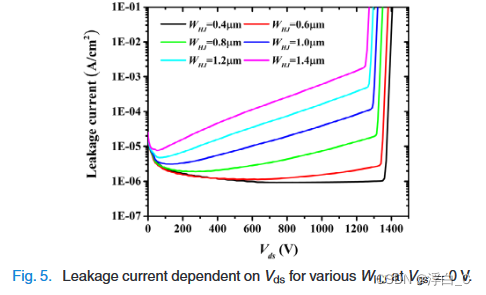

该结构存在问题:漏电流大,这是因为相邻 p-屏蔽之间的通道越宽,其掐断效应就越弱,异质结界面上的电场就越高,从而加速了热电场发射,导致漏电流增加。

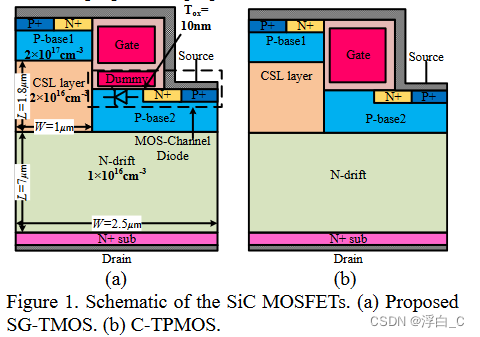

结构二:

优势:栅电荷减小,栅漏电容减小,第三象限性能改进。

结构分析不再赘述,可自行查看原文。

本文探讨了两种新型SiCMOSFET结构,旨在解决体二极管导通电压高引发的问题。一种是SiCJBS-MOSFET的改进,通过减小漏电流;另一种集成单极管设计,能降低栅电荷和漏电容,改善第三象限性能。

本文探讨了两种新型SiCMOSFET结构,旨在解决体二极管导通电压高引发的问题。一种是SiCJBS-MOSFET的改进,通过减小漏电流;另一种集成单极管设计,能降低栅电荷和漏电容,改善第三象限性能。

1254

1254

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?