问题描述:i代表按键值,通过for循环获得当前被按下的按键值,高值优先,临时存在temp中,最后赋给dina,但是仿真结果显示不论按键值是多少,dina始终为0

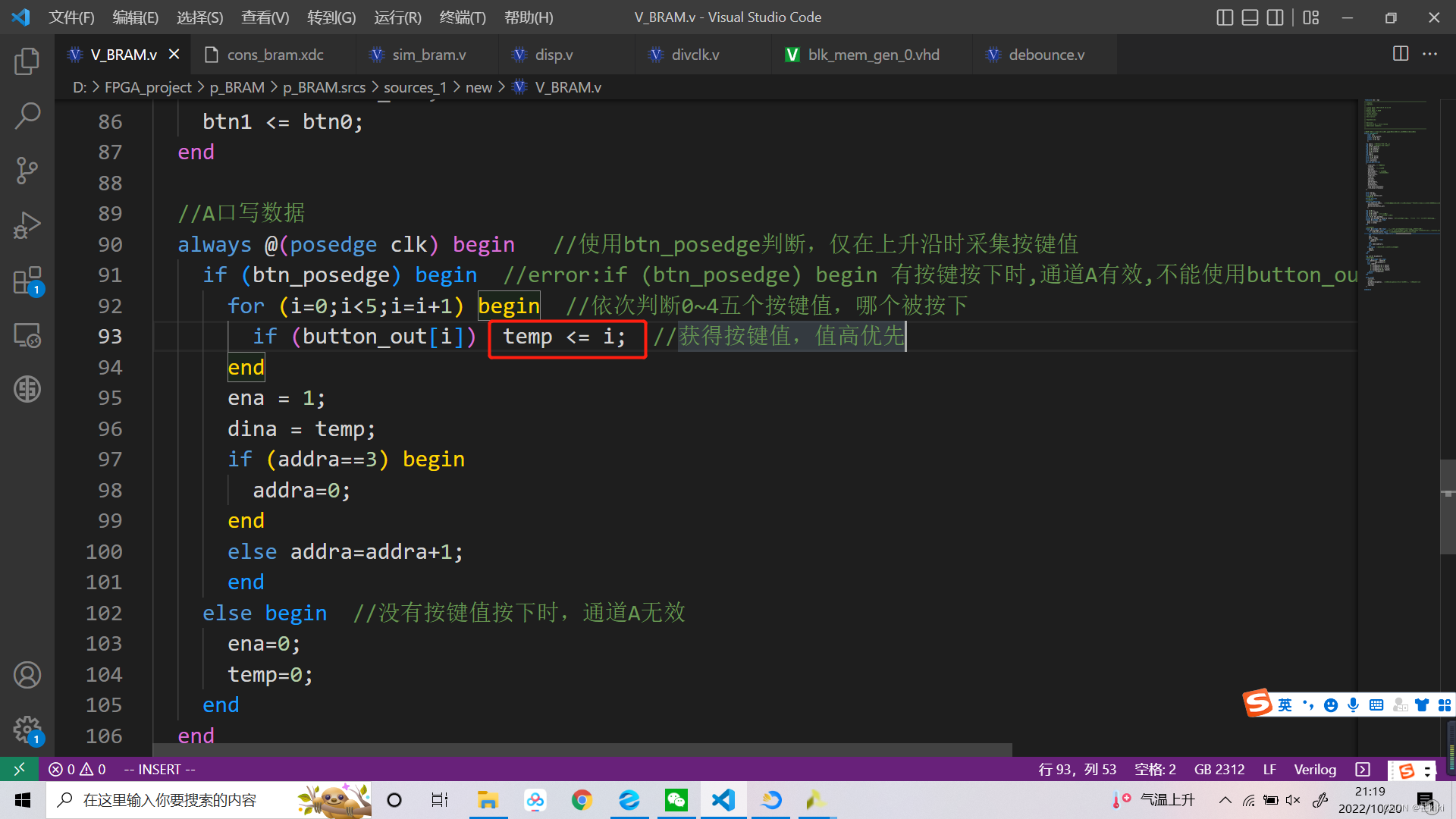

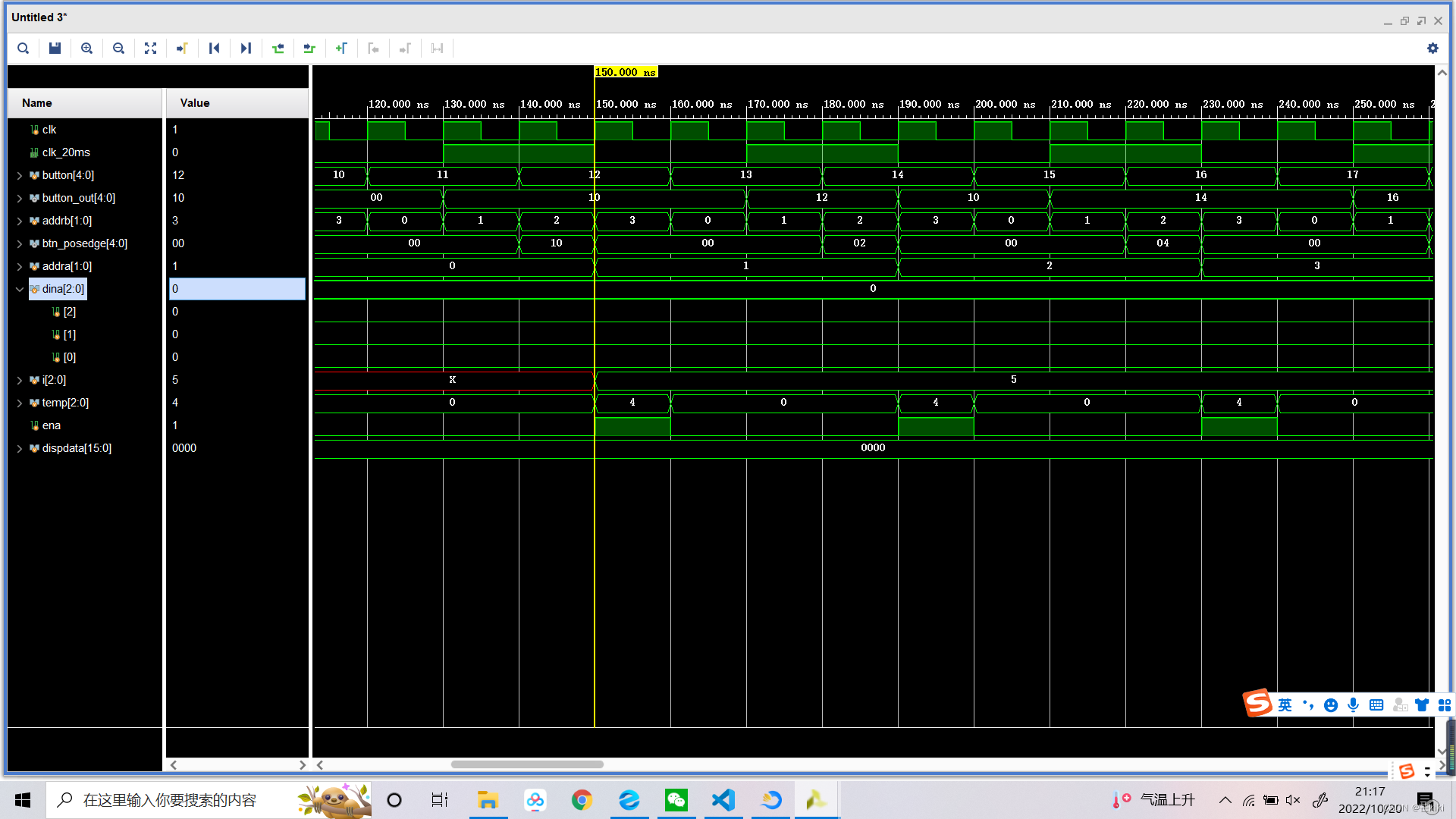

错误原因在于for循环中采用的非阻塞赋值语句:temp<=i,

该赋值语句会计算等式右边i的值,并在整个always语句结束时才将i的值赋给temp,因此dina得到的temp值一直未初值0,这也是为什么波形中temp值为4,但是dina值为0的原因,也就是说由于非阻塞语句不会阻断其后的语句,使得dina赋值时temp尚未得到新值。

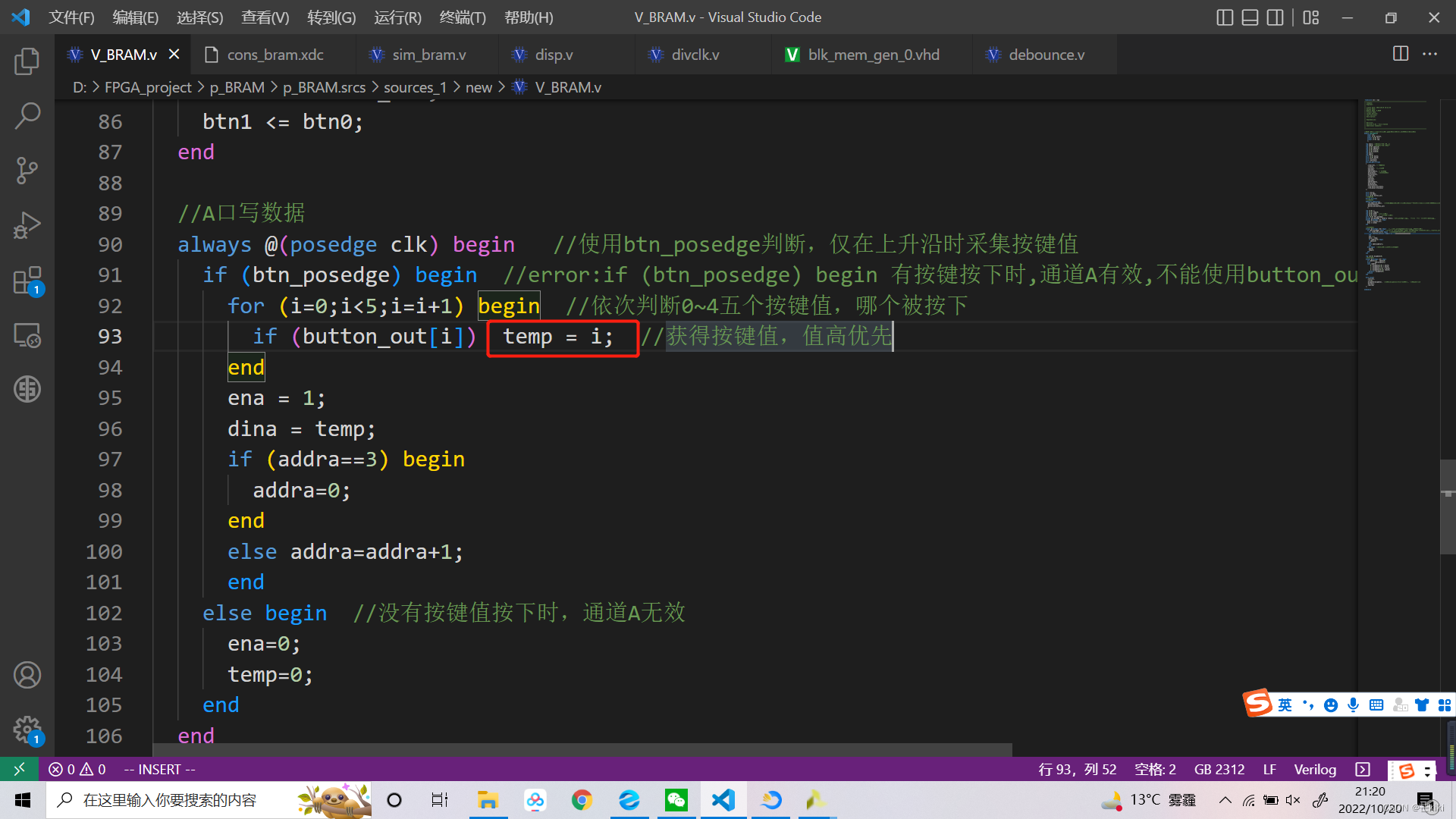

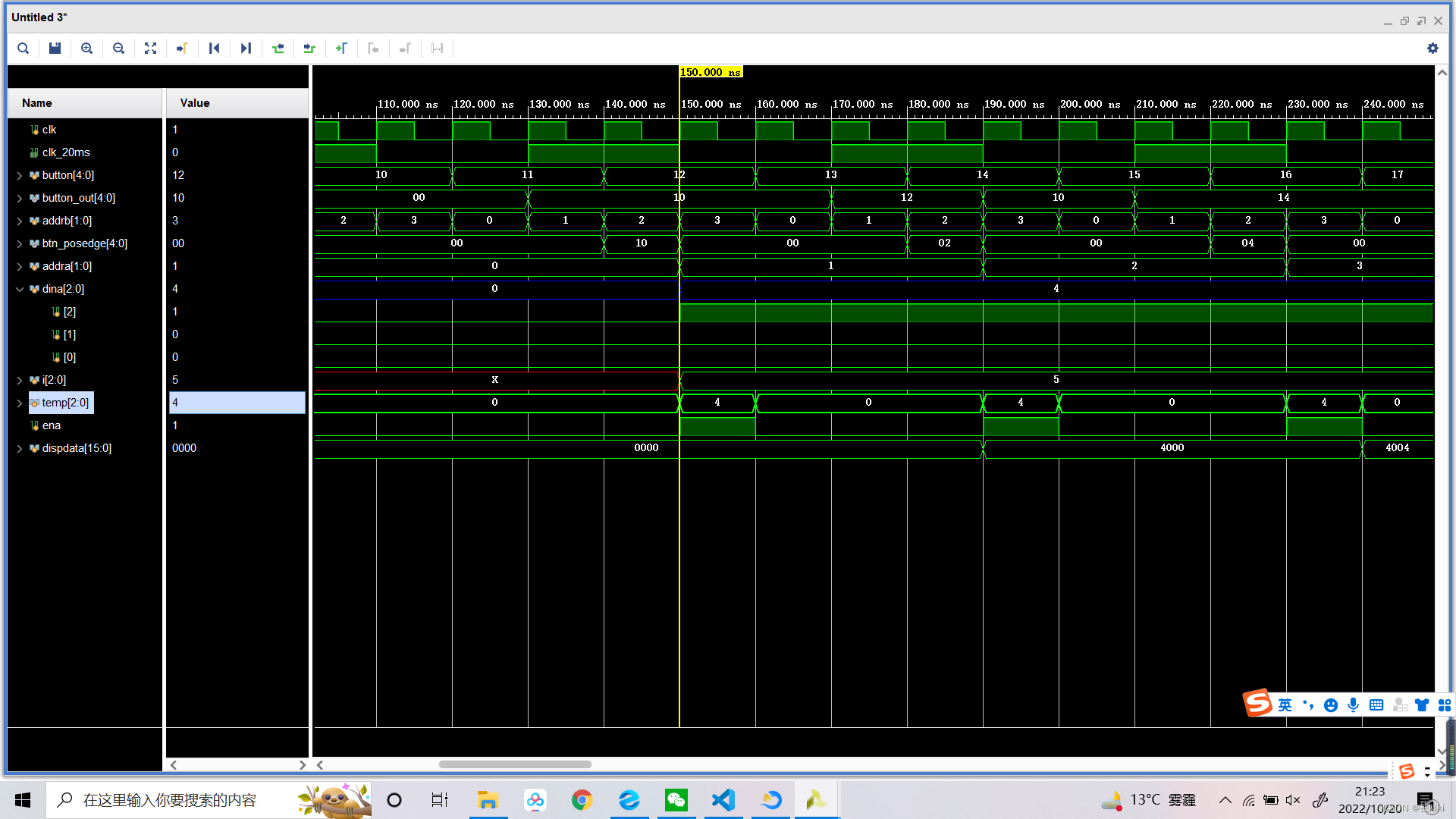

解决方法:将temp<=i,改为阻塞赋值:temp=i,修改完成后的波形如下:

总结:在for循环语句的时序逻辑中必须使用阻塞赋值

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?