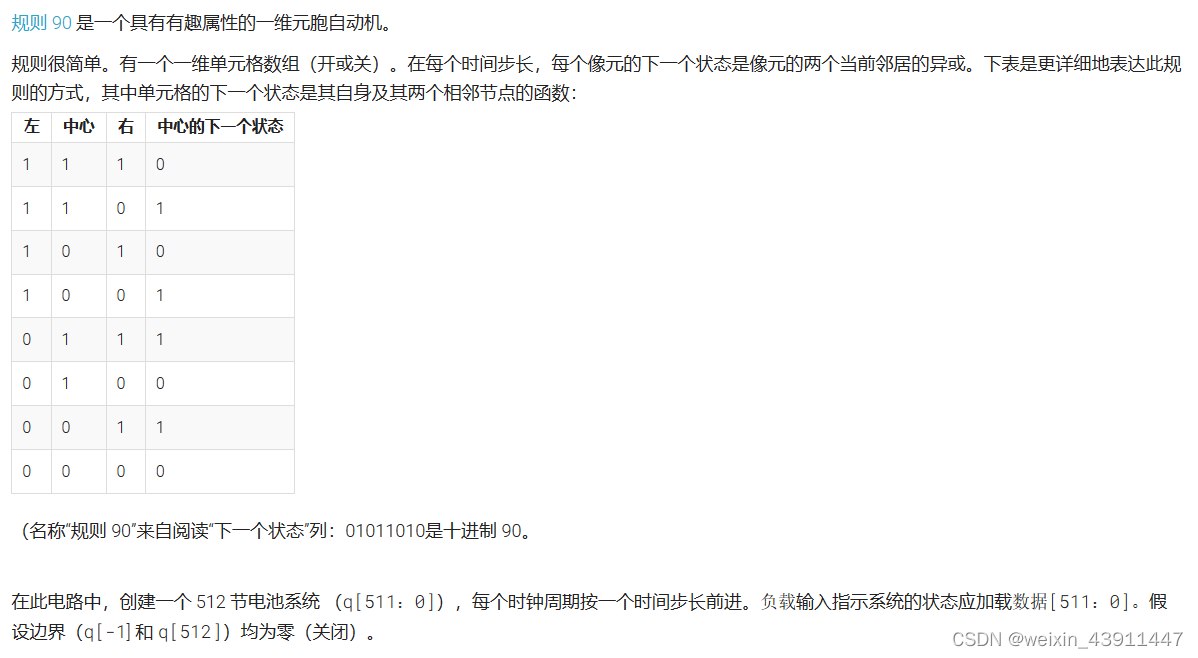

1. Rule 90

module top_module(

input clk,

input load,

input [511:0] data,

output [511:0] q );

int i;

always@(posedge clk)

begin

if(load)

q<=data;

else

begin //首尾需要特别对待

q[0]<= q[1]^1'b0;

q[511]<=q[510]^1'b0;

for(i=1;i<511;i++)

begin

q[i]<=q[i-1]^q[i+1];

end

end

end

endmodulemodule top_module(

input clk,

input load,

input [511:0] data,

output reg [511:0] q);

always @(posedge clk) begin

if (load)

q <= data; // Load the DFFs with a value.

else begin

// At each clock, the DFF storing each bit position becomes the XOR of its left neighbour

// and its right neighbour. Since the operation is the same for every

// bit position, it can be written as a single operation on vectors.

// The shifts are accomplished using part select and concatenation operators.

// left right

// neighbour neighbour

q <={1'b0, q[511:1]} ^ {q[510:0], 1'b0} ;

end

end

endmodule

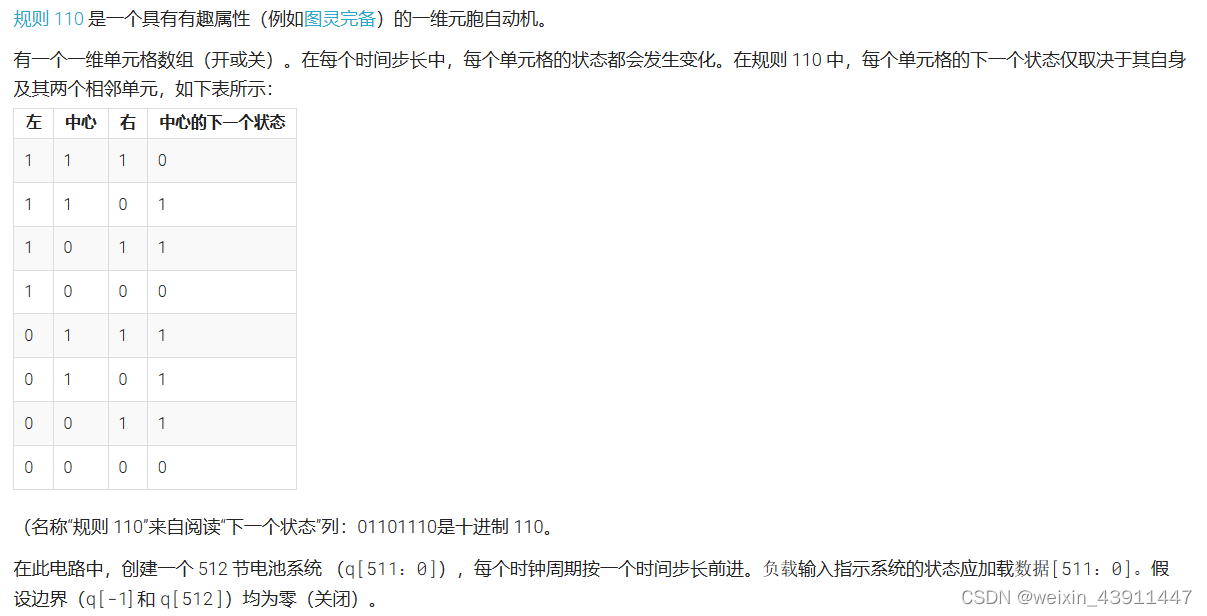

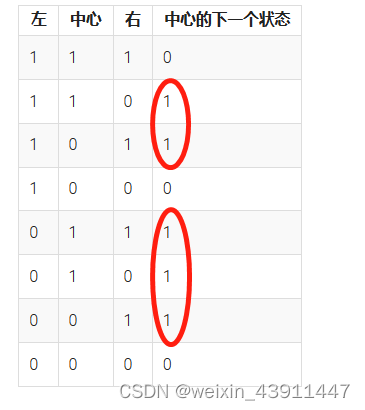

2. rule 110

可以根据真值表推一下

中心下一个

= 左&(中心^右) + ~左&(中心^右) + ~左&中心&右

= (中心^右) || (~左&中心)这道题有个bug,借助Logisim的组合逻辑分析,根据真值表得到的输出表达式为q<=(q^r)|((~l)&q),但网页仿真结果出错,猜测应该是真值表的 Left 和 Right 部分写反。

module top_module(

input clk,

input load,

input [511:0] data,

output [511:0] q

);

wire [511:0]right;

wire [511:0]left;

assign right={q[510:0],1'b0};

assign left={1'b0,q[511:1]};

always@(posedge clk)

begin

if(load)

begin

q<=data;

end

else begin

q[511:0]<=(q[511:0]^right)|(q[511:0]&(~left));

end

end

endmodulemodule top_module(

input clk,

input load,

input [511:0] data,

output [511:0] q

);

wire [511:0] l,r;

assign l=q<<1;

assign r=q>>1;

always@(posedge clk)begin

if(load) q<=data;

else begin

q<=(q^l)|((~r)&q);

end

end

endmodule

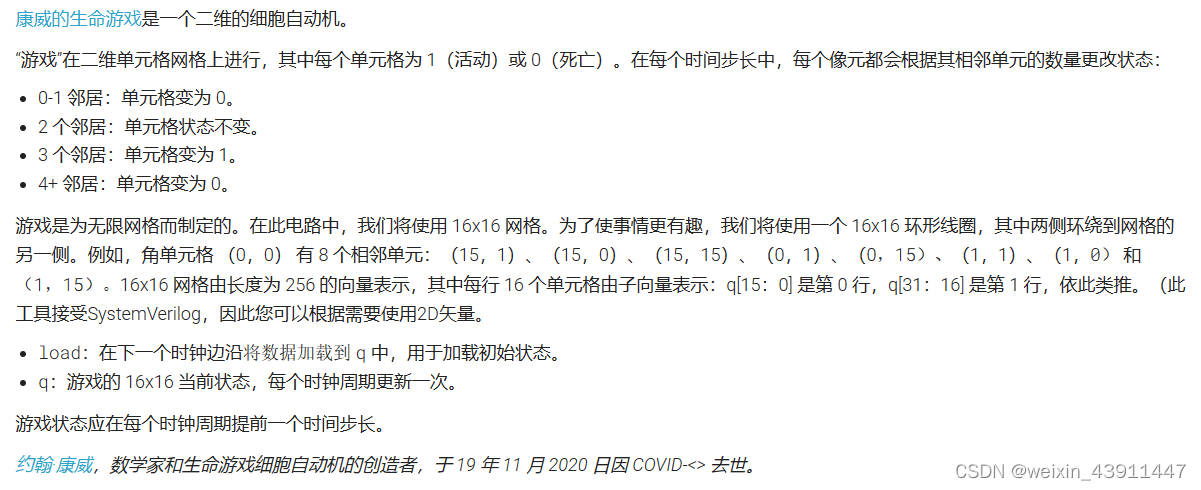

3. Conway’s Game of Life 16*16

在一个二维的棋盘上,每个格子有存活(1)和死亡(0)两种状态。在每个时间周期,每个格子会根据他的8个邻居来决定自己下一个周期的状态:

0-1个邻居:人口稀少,死亡(0);

2个邻居:保持原状态;

3个邻居:繁衍(1);

4+个邻居:人口过多,死亡(0);

这个游戏原来是设计在一个无限的网格里,但是在这个电路中,我们设计为16*16的网格,为了让这次练习更有趣,我们把网格边界拓扑环绕到对立的另一边。举个例子,(0,0)的8个邻居分别是(15,1), (15,0), (15,15), (0,1), (0,15), (1,1), (1,0), 和 (1,15).

我们把16*16的网格设置为一个256位的向量,每一行表示为q[15:0]、q[31:16]等等。

load:加载数据到q中作为初始状态。

q:16*16网格的当前状态,在每个时钟周期更新。

设计要点:

需要两个棋盘,一个存储现态,另一存储次态。

不能立即更新,需要现态中每个格子的8个邻居,不能将次态立即赋值给每个格子的现态。

设计思路:通过for循环语句遍历每一个格子,计算出每个格子的邻居数量,然后得到下一状态q_next。在每个边界应该分情况考虑,四个角和四个边的格子都有特殊的8个邻居。在遍历完256个格子之后将q_next的值赋给q,我们注意到在always过程块中,我们一律使用了阻塞赋值,因为不需要产生触发器,我们要在计算后立即赋值,才能做到没有一个周期的延迟。在Verilog中关系运算符不能这样使用:0<i<15,而应该0<i & i<15.

module top_module(

input clk,

input load,

input [255:0] data,

output [255:0] q ); //现态

reg [255:0] q_next; //次态

reg [3:0] sum; //邻居状态之和

always@(posedge clk) begin

if(load)

q<=data;

else begin

for(int i = 0 ; i<256 ; i++)

begin:bianli

if(i==0)//左上角

sum = q[1]+q[16]+q[17]+q[240]+q[241]+q[15]+q[31]+q[255];

else if(i==15)//右上角

sum = q[14]+q[16]+q[0]+q[240]+q[254]+q[30]+q[31]+q[255];

else if(i==240)//左下角

sum = q[0]+q[15]+q[239]+q[241]+q[1]+q[224]+q[225]+q[255];

else if(i==255)//右下角

sum = q[0]+q[15]+q[14]+q[224]+q[238]+q[240]+q[239]+q[254];

else if(0<i & i<15)//上边界

sum = q[i-1]+q[i+1]+q[i+15]+q[i+16]+q[i+17]+q[i+239]+q[i+240]+q[i+241];

else if(i%16==0)//左边界

sum = q[i-1]+q[i+1]+q[i+15]+q[i+16]+q[i+17]+q[i-16]+q[i-15]+q[i+31];

else if(i%16==15)//右边界

sum = q[i-1]+q[i+1]+q[i+15]+q[i+16]+q[i-17]+q[i-16]+q[i-15]+q[i-31];

else if(240<i & i<255)//下边界

sum = q[i-1]+q[i+1]+q[i-17]+q[i-16]+q[i-15]+q[i-239]+q[i-240]+q[i-241];

else //非边界

sum = q[i-1]+q[i+1]+q[i-17]+q[i-16]+q[i-15]+q[i+15]+q[i+16]+q[i+17];

case(sum) // 根据邻居之和 的 状态判断 次态 的状态

4'd2:q_next[i] = q[i] ;

4'd3:q_next[i] = 1;

default:q_next[i] = 0;

endcase

end

q = q_next;

end

end

endmodule

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?