今天这篇文章想分享一下从零开始,使用Verilog写一个状态机,并用Modelsim软件仿真状态机的效果。文章的框架如下所示:

-

前言

-

什么是状态机

-

状态机的分类

-

定义一个场景

-

Verilog代码实现

-

Modelsim仿真

-

总结

整篇文章阅读大概需要8分钟。

1.前言

去年在接触USB接口时,看到手册中描述要控制这个USB3.0的PHY,需要使用状态机,如下图所示。当时感觉这个玩意挺有意思,但是由于这是软件开发的内容,所以就没太在意具体细节是怎么实现的。

于是,从那时起状态机这个名字就一直停留在我的脑海里,但是也一直搁置,没有去尝试着自己做做看。最近打算自己写一个,因此就有了这篇文章,用Verilog写个状态机。

2.什么是状态机

逻辑电路根据是否包含记忆元件分为组合逻辑和时序逻辑。组合逻辑电路不包含记忆元件,因此组合逻辑的特点是当前的输出等于输入。时序逻辑电路含有记忆元件,因此时序逻辑电路的输出并不完全取决于当前的输入,还和过去的状态有关。时序逻辑电路的输出受到输入和记忆元件值的共同影响。

这里和我们以前学习的自动控制系统类似,对开环系统来说,输出和输入相对应。而对于闭环系统来说,会把过去的输出反馈到当前的输入上,所以当前的输出其实会受到过去输出的影响。

组合逻辑的输出和输入直接相关,直接用NOT-AND-OR就能描述清楚。而时序电路则可以使用有限状态机(FSM)来描述。

3.状态机的分类

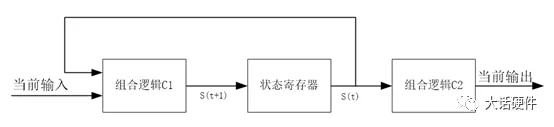

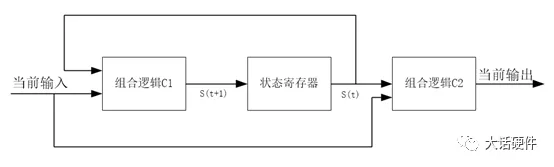

状态机分类两种类型米勒Mealy型和摩尔Moore型。米勒型的状态机输出由内部状态和输入共同决定。摩尔型的输出仅由内部状态确定。

摩尔型

米勒型

从上面的结构图可以看出,摩尔型的输出,是直接和当前状态S(t)相同,但是米勒型的输出,不仅和当前的S(t)相关,与当前的状态也有关。

4.定义一个场景

状态机在我们生活中用的比较多,最常见的就是在寝室门口,地铁进站口的自动售货机,使用状态机就可以描述出来。比喻,售货机里面的烤面包2.5元一个,机器的投币口只接受硬币,假设我们去购买时,只有0.5元和1元的硬币,那么在购买面包的过程中,就可以用状态机来实现。

网络协议由三个要素组成,语义,语法,时序,采用类比的思想,状态机也有三个要素组成,分别是输入,输出,和状态。在设计状态机时,可以从这三个状态入手,一步一步完成状态机的建立。

以买烤面包的场景为例,输入为投入的硬币,可能是0.5元可能是1元,输入有两种可能性,而且输入会立刻影响状态机的跳转;输出是我们最终想要的结果,出面包或者找零钱;在买面包的过程中,不同的状态受到上一个状态和当前输入的影响。

以上的分析结果为:

输入:0.5元,1元

输出:出面包但是不找零;出面包而且找零

状态:初始状态,投入0.5元,投入0.5元,投入1.5元,投入2元,投入2.5元,投入3元

考虑状态在2.5元和状态在3元时,都会输出结果,因此将2.5元和3元的状态直接和初始的状态合并。出完面包或者找完零以后,机器会立马回到最初状态。画出整个系统的状态图如下:

其中:01/00:代表投入0.5元,没有输出;10/00:代表投入1元,没有输出;10/11:代表投入1元,出面包且找零,其他的可以类推。

5. Verilog代码实现

定义接口和状态

描述状态机的跳转,状态机只有在输入了硬币的条件下才转移,这也是触发状态机变化的条件。

描述输出面包和输出找零的结果。

从上面的代码可以看出来,状态机的描写可以看成是两个部分。第一个部分是只管状态的转移,仅仅是在有输入的情况下影响了状态,此时不管输出。这部分代码完成了状态机三要素中的两个要素,输入和状态。第二部分只管描述输出,这部分的输出是采用了米勒型来描述,不仅和当前的状态有关,还和输入有关。这部分代码完成了状态机三要素的另一个要素,输出。

6. Modelsim仿真

编写Testbench文件来仿真上面的状态机功能,看看在不同输入条件下,状态机是否能正常跳转。使用Modelsim软件查看波形。

定义接口列表

例化

仿真结果

从上面的仿真的结果来看,状态机的功能正常。截图所示是连续5次0.5元,此时出面包,但是没有找零。2次0.5元,2次1元,出面包,并且找零。仿真的结果和我们最初的设计吻合。

7.总结

当把这个状态机写完才发现,使用Verilog写状态机也不是很难。好像学习都是这样,没有做过的东西都感觉有难度,等自己学会了以后,就会发现并没有想象中的那么复杂。

学习状态机不难的原因是它和我们之前学过的EMC三要素差不多。在EMC设计中抓住三个要素,就能设计较好性能的单板,同样,写状态机时只要抓住了它的输入,输出,状态这三个要素,其实也可以搞定。

参考文献:

《FPGA原理和结构》日 田野英晴

《Xilinx Artix-7 FPGA 快速入门,技巧及实例》吴厚航 尤恺元 杨亮

《FPGA Verilog 开发实战指南》刘火良 杨森 张硕

更多内容关注大话硬件

483

483

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?