基于等精度测量的数字频率计仿真工程

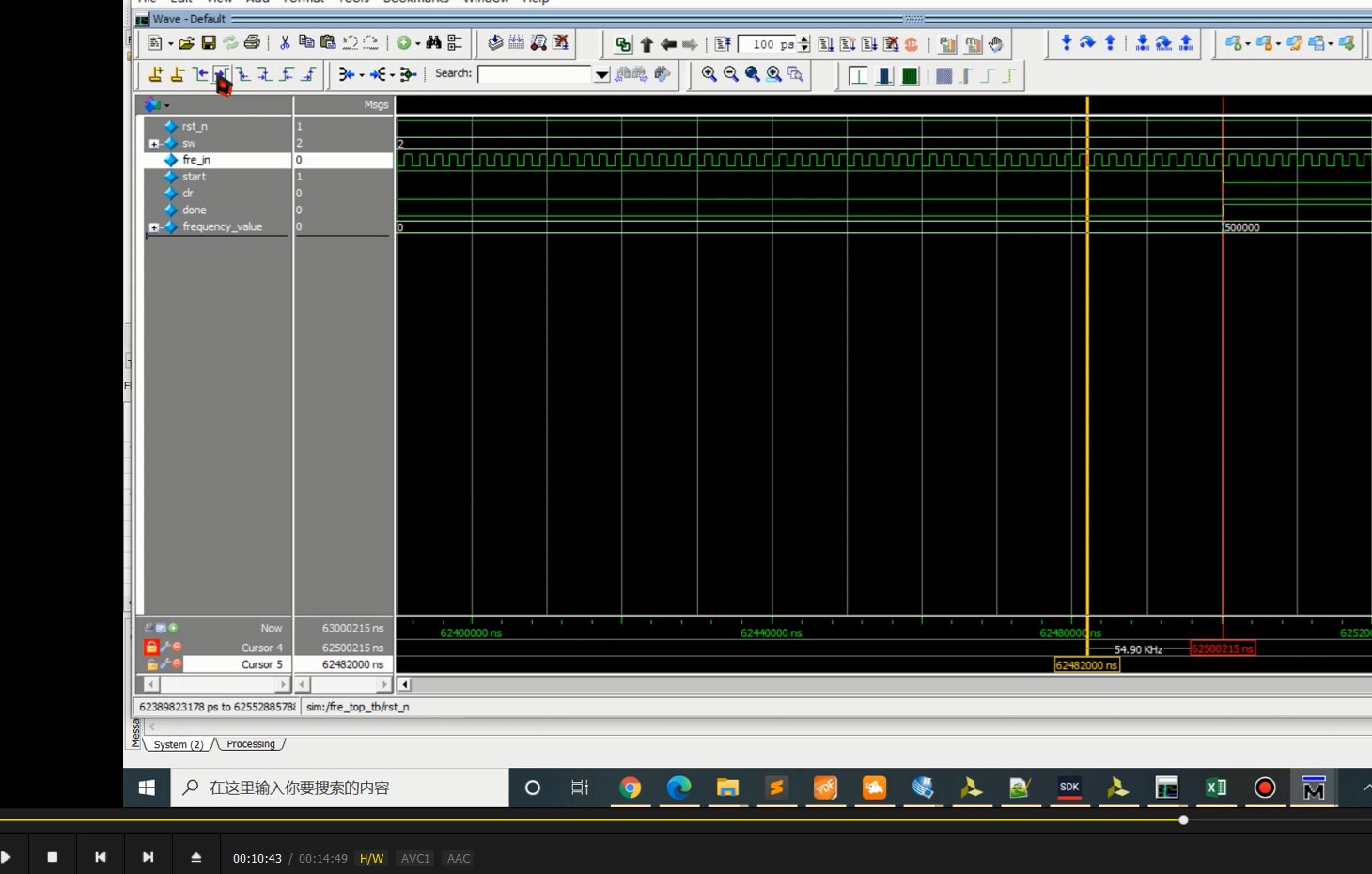

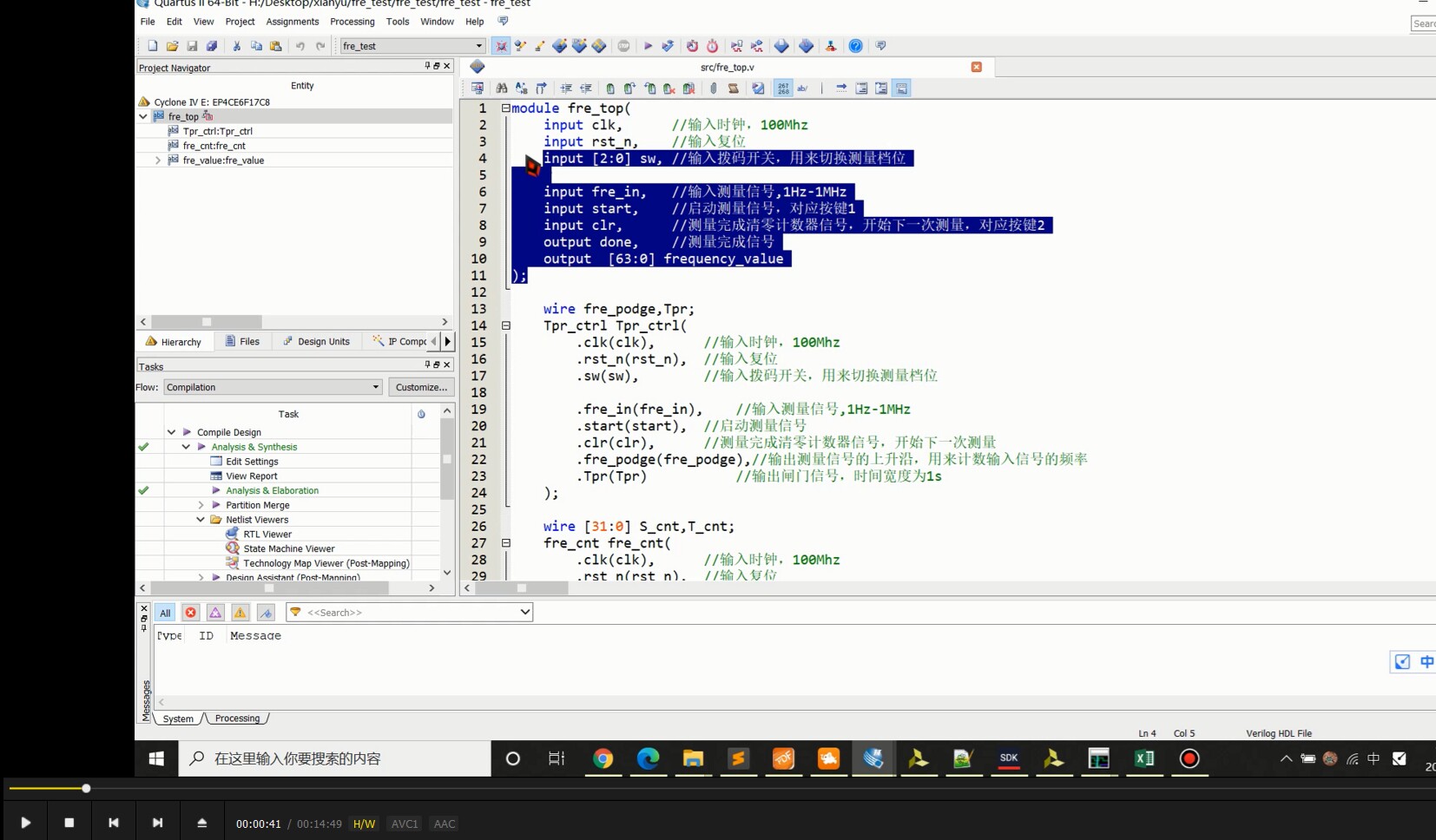

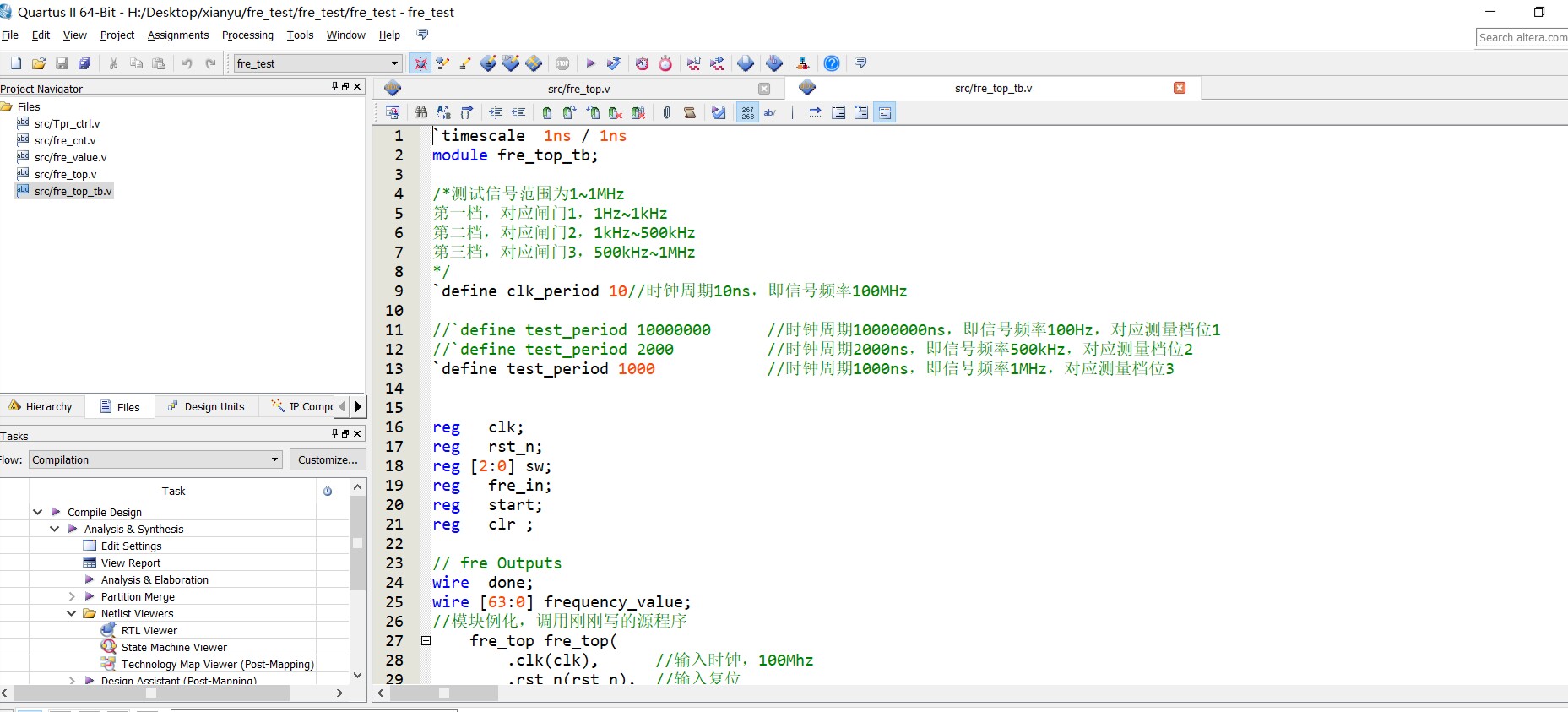

本设计按照等精度测量原理,设计三个模块,分别是闸门时间模块,计数器模块,测量结果模块,最后用顶层文件封装起来,编写测试文件在quartus+modelsim联合仿真完整结果,还有专门录制的视频对工程讲解,手把手教你对这个工程仿真,可看图片

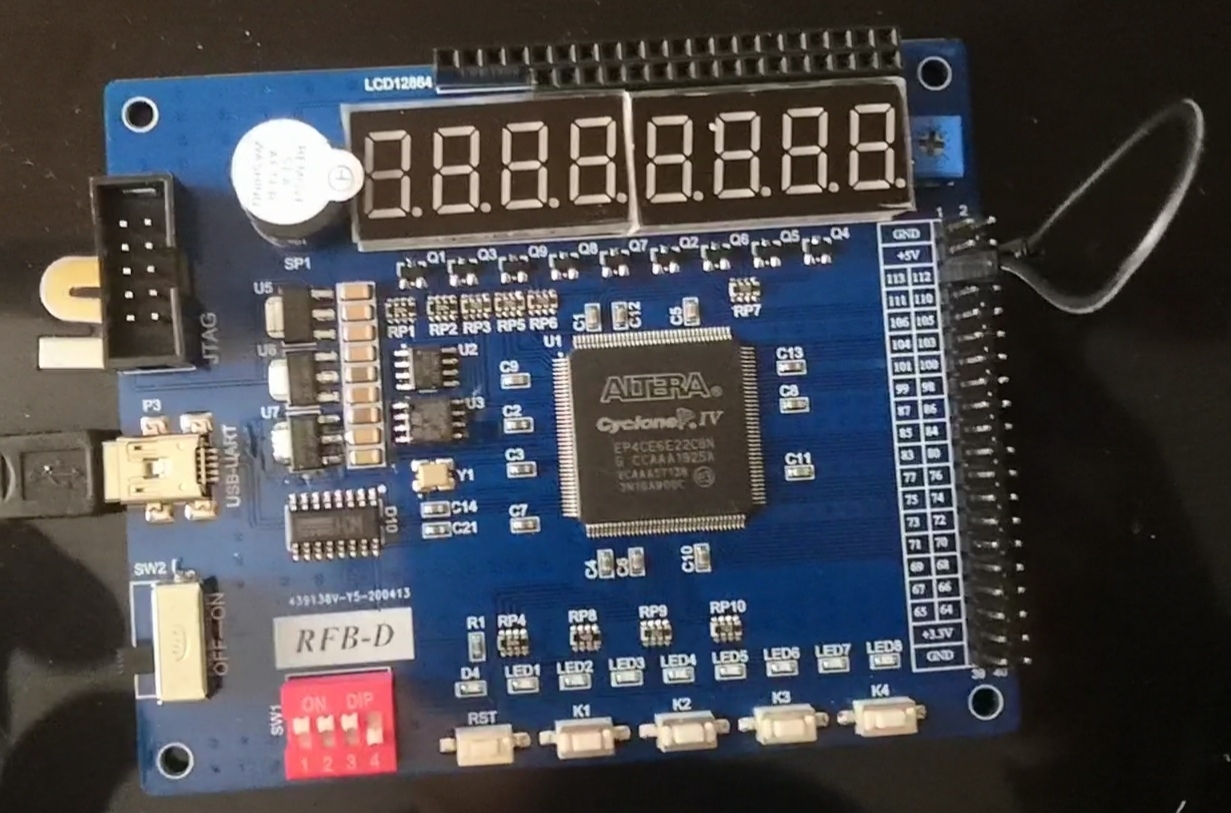

这个频率计的功能可以测量频率1Hz-50MHz,只要最高系统时钟频率是测量频率的2倍就行,可以按照不同的频率范围使用不同的闸门时间宽度,也就是量程切换,具体的代码都会有注释,适合有fpga基础的人联系来学习,如何仿真验证一个工程,同时也可以仿真占空比,相位差,脉冲宽度的工程,需要的话可以聊,做成硬件的也可以,也有现成做好的硬件,关键是做成的对学习和研究有帮助就都可以帮忙!

包括完整的quartus工程和视频(15分钟左右)

ID:93199620255055769

義小周Angel

基于等精度测量的数字频率计仿真工程

引言

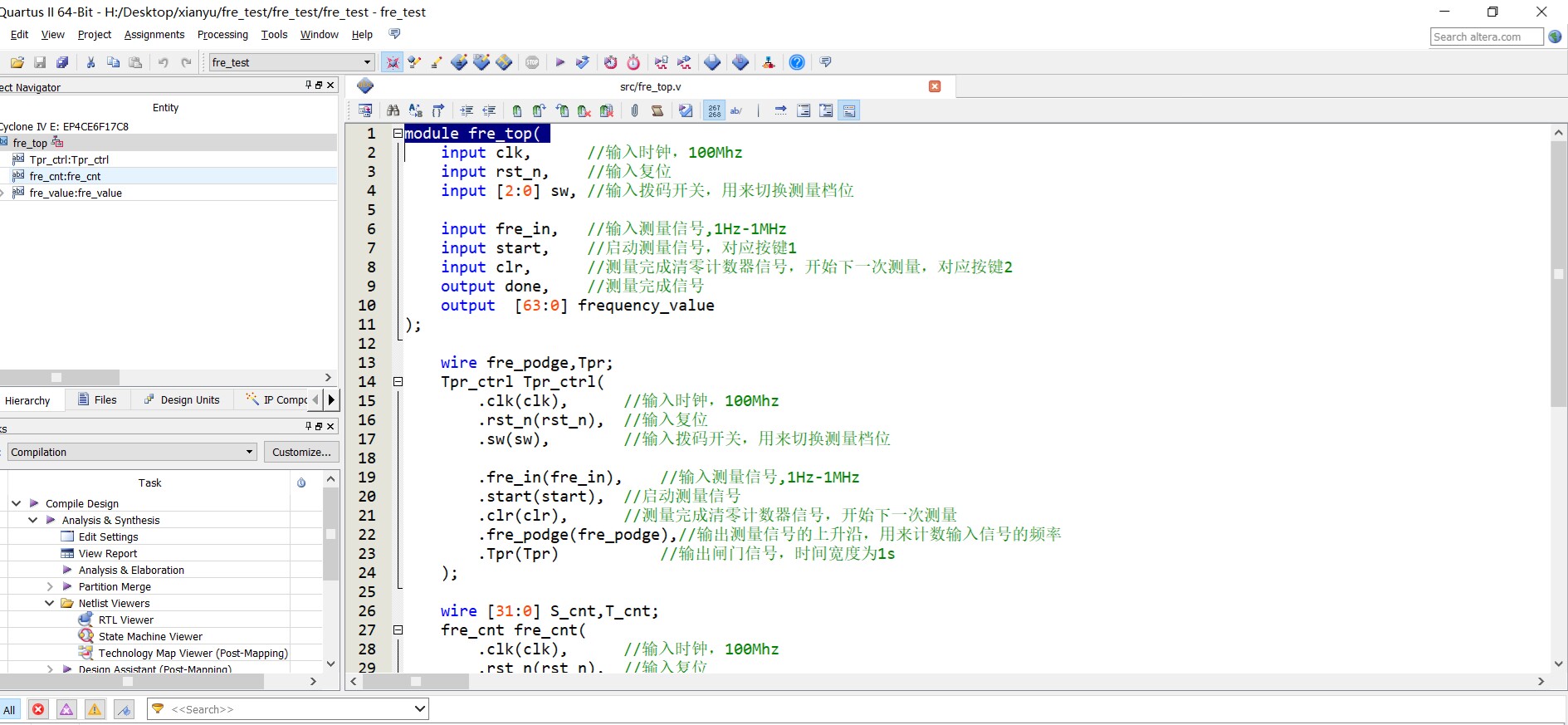

在现代科技领域中,频率计是非常重要的测量工具之一。本文将介绍一种基于等精度测量原理的数字频率计仿真工程。该工程设计了三个模块,分别是闸门时间模块、计数器模块和测量结果模块,并通过顶层文件封装起来。我们还编写了测试文件,通过在quartus+modelsim联合仿真来验证整个工程的正确性。此外,我们还录制了专门的视频,详细讲解了这个工程的仿真过程,为您提供了一种手把手教学的方式。

设计模块

-

闸门时间模块

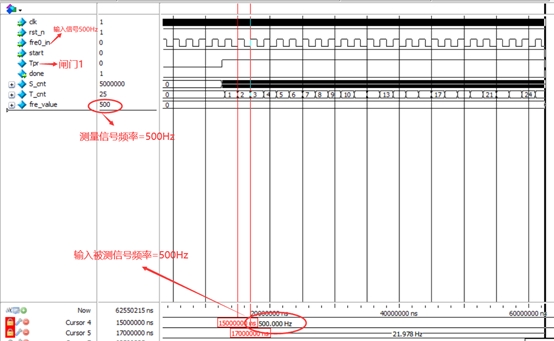

闸门时间模块是实现等精度测量原理的核心模块之一。它通过设定一个特定的时间窗口(即闸门时间宽度),在该时间窗口内对输入信号进行采样和计数。可以根据不同的频率范围,选择不同的闸门时间宽度,实现量程的切换。具体的代码实现在工程中都有详细的注释,以方便用户理解和修改。 -

计数器模块

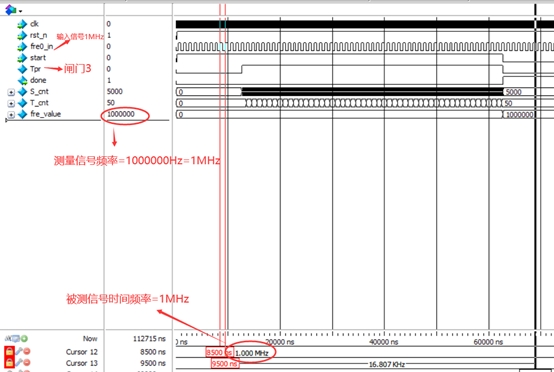

计数器模块是对输入信号进行计数的模块。在闸门时间内,计数器对输入信号的脉冲个数进行累加,从而得到频率的测量结果。计数器模块需要根据所需测量的最高频率来确定其最大计数值。在设计中,我们将支持测量频率在1Hz-50MHz范围内的计数器模块作为示例。 -

测量结果模块

测量结果模块用于将计数器模块得到的计数值转换为频率值。根据频率计的测量原理,我们可以通过计数值与闸门时间宽度的比值来得到频率的估计值。在工程中,我们使用了合适的算法和查找表来实现这个转换过程,并将最终的测量结果输出。

仿真验证

为了验证该工程的正确性,我们使用quartus+modelsim进行了联合仿真。我们编写了测试文件,并通过模拟输入信号来触发频率计的测量过程。通过对比仿真结果和已知的输入信号频率,可以验证频率计的准确性。在仿真过程中,我们还录制了专门的视频,详细讲解了仿真过程的每个步骤。这为学习者提供了一种更直观、更容易理解的方式。

扩展功能

除了基本的频率测量功能外,该工程还支持其他功能的仿真验证。例如,您可以通过调整仿真输入信号的占空比来验证频率计对占空比的测量能力。同样地,您还可以通过引入相位差或脉冲宽度来验证频率计在这些方面的性能。如果您需要进一步了解这些功能的实现方法,我们也非常愿意详细讨论和提供帮助。

结论

本文介绍了一种基于等精度测量原理的数字频率计仿真工程。通过设计闸门时间模块、计数器模块和测量结果模块,我们实现了频率的准确测量。我们提供了完整的quartus工程和详细的仿真视频,可供学习者进行学习和研究。同时,我们还强调了该工程的灵活性,使其可以支持多种扩展功能的仿真验证。希望本文能为对FPGA有基础的学习者提供实用的学习工具,并为科研工作者提供有价值的研究资源。

【注】本文所述工程中提供的完整quartus工程和仿真视频请与作者联系获取。

相关的代码,程序地址如下:http://imgcs.cn/620255055769.html

1460

1460

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?