仿真概述:

由于在FPGA 设计的过程中,不可避免的会出现各种 BUG。

但如果在编写好代码、综合成电路、烧写到FPGA 后才发现问题,此时再去定位问题就会非常地困难。

而在综合前,设计师可以在电脑里通过仿真软件对代码进行仿真测试,检测出 BUG 并将其解决,最后再将程序烧写进 FPGA。一般情况下可以认为没有经过仿真验证的代码,一定是存在 BUG 的。

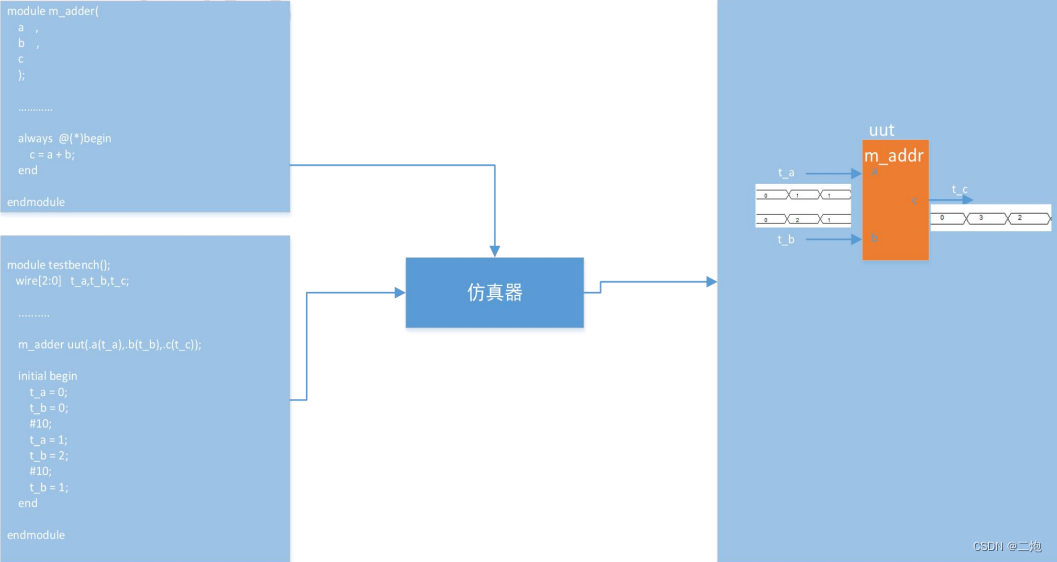

为了模拟真实的情况,需要编写测试文件。该文件是用 Verilog 编写的,其描述了仿真对象的输入激励情况。该激励力求模仿最真实的情况,产生最接近的激励信号,将该信号的波形输入给仿真对象,查看仿真对象的输出是否与预期一致。需要注意的是:在仿真过程中没有将代码转成电路,仿真器只是对代码进行仿真验证。至于该代码是否可转成电路,仿真器并不关心。

由此可见,Verilog 的代码不仅可以描述电路,还可以用于测试。事实上,Verilog 定义的语法非常之多,但绝大部分都是为了仿真测试来使用的,只有少部分才是用于电路设计。Verilog 中用于设计的语法是学习的重点,掌握好设计的语法并熟练应用于各种复杂的项目是技能的核心。而其他测试用的语法,在需要时查找和参考就已经足够了。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?