目录

2.1、单个外部参考时钟驱动单个QUAD中的多个transceiver

2.2、单个外部参考时钟驱动多个QUAD中的多个transceiver

2.3、同一个Quad中,多个GTX Transceiver使用多个参考时钟

2.4、不同Quad中,多个GTX Transceiver 使用多个参考时钟

文章总目录点这里:《FPGA接口与协议》专栏的说明与导航

1、参考时钟

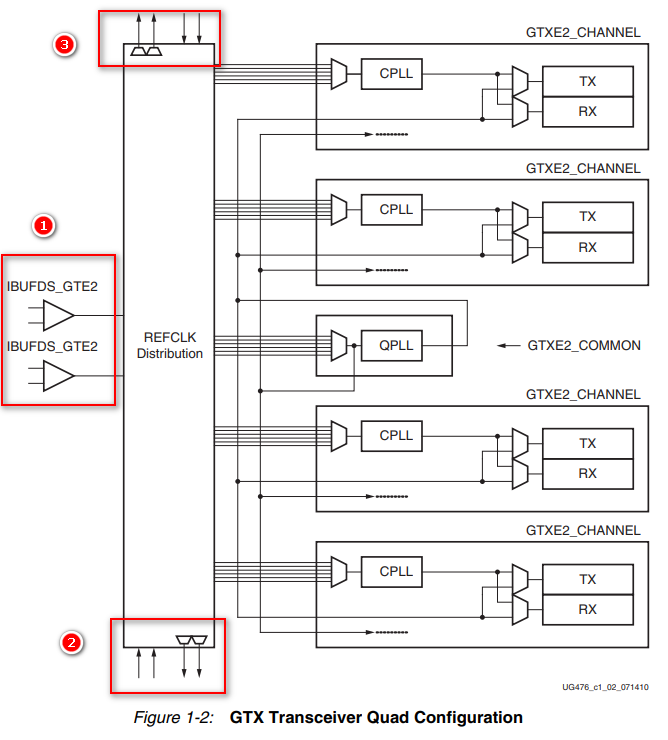

GTX的时钟架构如下:

对于QPLL来说,它的时钟来源有3个:

-

外部差分差分时钟,通过IBUFDS_GTE2原语后变成单端时钟,然后给到QPLL。这种时钟有两个,分别叫做GTREFCLK0和GTREFCLK1

-

来自北边(GT Quad的排布是南北

订阅专栏 解锁全文

订阅专栏 解锁全文

1733

1733

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?