VHDL全名Very-High-Speed Integrated Circuit Hardware Description Language ,是一种标准硬件描述语言。下面通过60进制计数器来分析VHDL的语法,以及一些硬件设计的理解。

60进制计数器,顾名思义,是每60个时间单位输出一个脉冲信号。60进制可以利用小于60进制的计数器的累加来达成相应的功能。主要有以下两种思路:

一种是直接其中的一个计数器通过时钟型号累加,另一个则是接受第一个计数器的进位信号,而进行加法计数。他们共用一个时钟信号,为并行进位。

一种是高位计数器的时钟连着低位计数器的进位信号,从而进行增加。

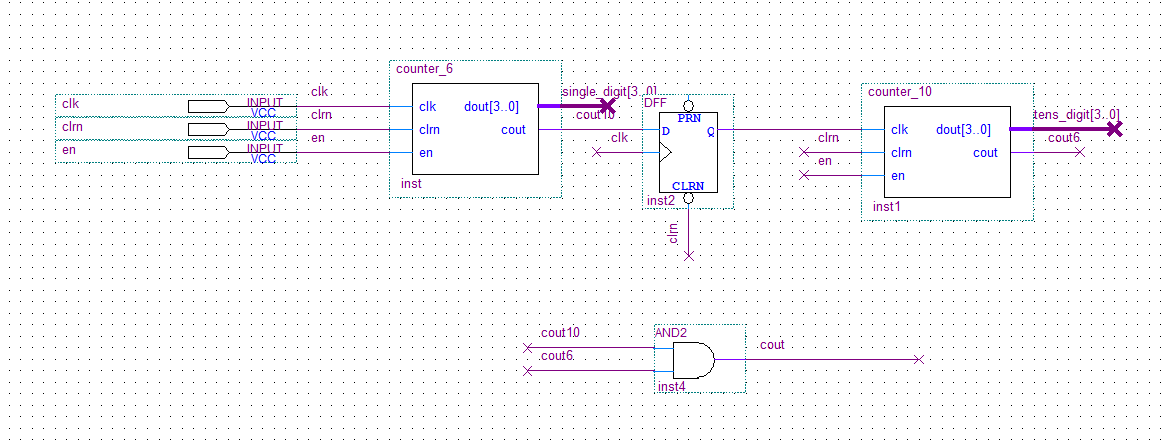

这里取第二种思路,通过一个10进制的计数器和一个6进制的计数器来实现60进制计数器。

顶层图如下

下面我们用VHDL语言来实现。

首先是6进制计数器。

注意!!器件最好不要以数字作为开头

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;这部分是库的声明。1164库中包括了大部分标准的类型,器件。

而unsigned中则包括了如加法等器件。

entity counter_6 is

port(

clk,clrn,en:in std_logic;

dout:out std_logic_vector (3 downto 0);

cout:out std_logic);

end counter_6;这部分为这个文件所描述的总器件端口的声明,类似编程中主函数的声明。

architecture counter_6_arch of counter_6 is这下面就是器件内部的描述内容、类似编程中的主函数实现。

signal douti:std_logic_vector (3 downto 0);

begin

process(en,clk,clrn,en)

begin

if clrn = '0' then

这篇博客介绍了如何使用VHDL语言设计60进制计数器,通过解析60进制计数器的工作原理,提出了两种实现思路,并选择了其中一个(高位计数器的时钟连着低位计数器的进位信号)进行详细讲解。作者使用10进制和6进制计数器组合实现,展示了VHDL代码,并强调了VHDL在硬件描述语言中的优势和不同实现方式。

这篇博客介绍了如何使用VHDL语言设计60进制计数器,通过解析60进制计数器的工作原理,提出了两种实现思路,并选择了其中一个(高位计数器的时钟连着低位计数器的进位信号)进行详细讲解。作者使用10进制和6进制计数器组合实现,展示了VHDL代码,并强调了VHDL在硬件描述语言中的优势和不同实现方式。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?