本实验为某公司校招问题:本人在2021/1/17日完成. 分享给大家.

使用FPGA设计一个简单的流水灯程序,红绿蓝三个LED闪烁即可。本文章提供Verilog的源代码,验证代码,以及简单的外围电路。

Verilog代码:

`timescale 1ns / 1ps

module led_flowing(

input rst_n,

input clk,

output reg[2:0] led

);

reg [12:0] counter; //编写Tb时采用1us的时钟信号。若0.2s 闪烁间隔 则需要计数300

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

counter <= 12'b0;

else if (counter <12'd299)

counter <= counter + 12'd1;

else

counter <= 12'd0;

end //300循环计数

always@(posedge clk or negedge rst_n)//实现流水灯

begin

if(!rst_n)

led <= 3'b000;

else if (counter ==12'd0)

led <= 3'b001;

else if (counter == 12'd99)

led <= 3'b010;

else if (counter == 12'd199)

led <= 3'b100;

else

led <=led;

end

endmodule

Tb代码:

module led_tb();

reg clk;

reg rst_n;

wire [2:0] led;

integer case_num;

led_flowing led_flowing_01

(

.clk(clk),

.rst_n(rst_n),

.led(led)

);

always

begin

#1 clk <= ~clk; //时钟周期为2us

end

initial

begin

clk=1'b0;

case_num =1;

rst_n = 1;

#10;

if(led == 3'b001)

$display ("[simulation INFO] %2d LED pass.", case_num);

else

$display("[simulation ERROR] %2d fall.",case_num);

#200; //验证前0.2s 是否为001输出,并打印结果。

case_num =2;

#10;

if(led == 3'b010)

$display ("[simulation INFO] %2d LED pass.", case_num);

else

$display("[simulation ERROR] %2d fall.",case_num);

#200; //验证前0.2s-0.4s 是否为010输出,并打印结果。

case_num =3;

if(led == 3'b100)

$display ("[simulation INFO] %2d LED pass.", case_num);

else

$display("[simulation ERROR] %2d fall.",case_num);

#200; //验证前0.4s-0.6s 是否为100输出,并打印结果。

$finish;

end

endmodule

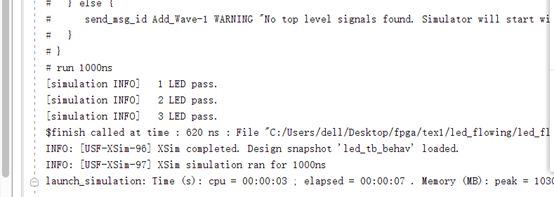

实验结果:

1694

1694

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?