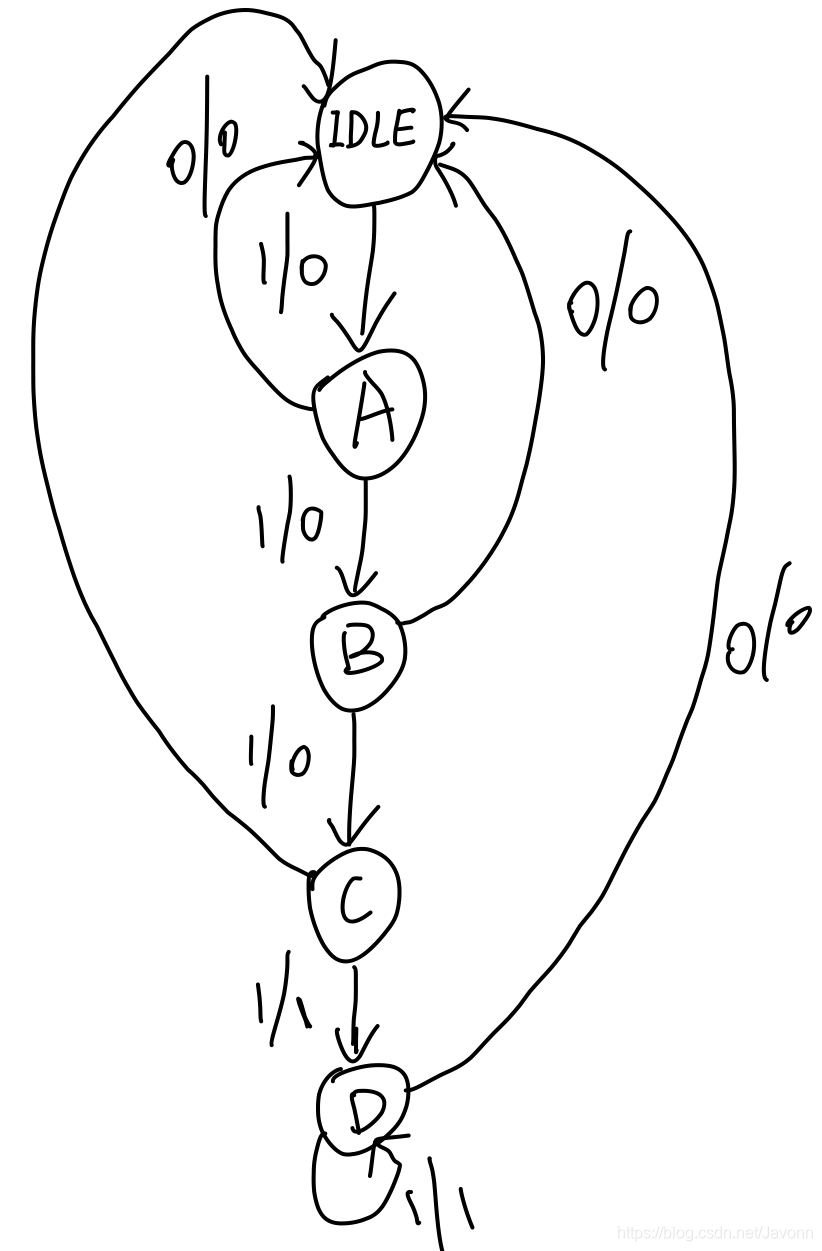

状态转换图如下:

//******************************seqdet.v**************************************

module seqdet(x,z,clk,rst,state);

input x,clk,rst;

output z;

output[2:0] state;

reg[2:0] state;

wire z;

parameter IDLE=3'd0,A=3'd1,B=3'd2,C=3'd3,D=3'd4;

assign z = ((state==C && x==1)||(state==D && x==1))?1:0 ;

always @(posedge clk)

begin

if(!rst) state<=IDLE;

else

casex(state)

IDLE: if(x==1) state<=A;

else state<=IDLE;

A: if(x==1) state<=B;

else state<=IDLE;

B: if(x==1) state<=C;

else state<=IDLE;

C: if(x==1) state<=D;

else state<=IDLE;

D: if(x==1) state<=D;

else state<=IDLE;

default: state<=IDLE;

endcase

end

endmodule

//******************************seqdet_TB.v**************************************

`timescale 1ns / 1ns

module seqdet_TB;

reg clk, rst,x;

wire[2:0] state;

wire z;

always #10 clk=~clk;

always @(posedge clk)

begin

x<={$random}%2;

end

initial

begin

clk=0;

rst=1;

#2 rst=0;

#10 rst=1;

#1000 $stop;

end

seqdet m(x,z,clk,rst,state);

endmodule

本文详细介绍了使用Verilog语言实现状态机的过程,包括模块定义、参数设置、状态转换逻辑及输出信号处理。通过具体代码示例,展示了如何根据输入信号进行状态转换,并输出相应的结果。

本文详细介绍了使用Verilog语言实现状态机的过程,包括模块定义、参数设置、状态转换逻辑及输出信号处理。通过具体代码示例,展示了如何根据输入信号进行状态转换,并输出相应的结果。

1261

1261

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?