题目: 设计一个串行数据检测电路. 当连续出现4个和4个以上的1时, 检测输出信号为1, 其余情况下的输出信号为0.

分析:

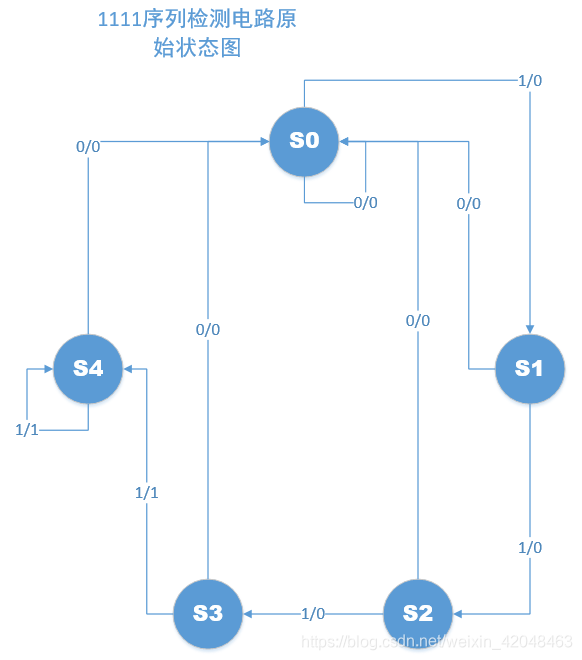

从题目的表述中, 我们获取到信息, 连续出现4个或4个以上的1时, 输出信号为1, 否则为0: 实际上是让我们设计一个1111序列检测电路. 对于问题的转换十分重要, 若此处不能将问题转换为设计1111序列检测电路, 那电路的设计难度将会很大.

既然已经将问题转化为1111序列检测电路的设计, 那我们进入到设计序列检测电路的设计模板中来:

①确定状态个数:

1111序列检测电路至少需要5个状态, 我们先将这5个状态设为S0、S1、S2、S3、S4.

②根据1111序列检测的特性, 绘制原始状态图(此处读者不要过多思虑, 只需要按照感觉设计即可).

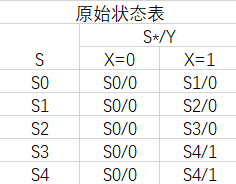

③将原始状态图转换为原始状态表.

④从原始状态表中寻找等价状态, 并化简原始状态表.

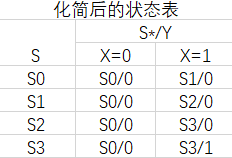

从原始状态表中, 我们可以看出, S3、S4为等价状态, 则将S4行删除, 并将剩下部分出现S4的地方用S3代替.

⑤根据化简后的状态表, 绘制状态图:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1298

1298

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?