1.什么是玻纤效应,影响,解决

玻纤效应:信号在玻璃纤维和树脂中的传播速度不同;

影响:传输线阻抗波动和差分歪曲;

解决:1.避免水平或垂直走线,采用Z字型或10度;2.选择选择玻纤窗口更小的PP/CORE;3.采用扁平E-玻纤布或更好NE-玻纤布,玻纤扁平化处理;4.旋转PCB板生产

2.源端匹配和终端匹配优缺点,使用场景

源端:终端没有匹配,终端反射到源端消除反射,消除二次多次反射;

终端:到终端消除,都不会反射;接收器阻抗比较高

源端:驱动器阻抗低,例如高速线信号,串联合适几十欧电阻匹配;串口串联22Ω

终端:接收器阻抗高,例如485,CAN终端并联120欧

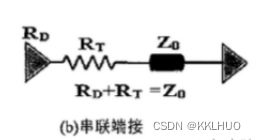

源端串联端接:

RD:发送端(源端)输出阻抗(比如推挽输出MOS管内阻等)

RT:发送端串联电阻

Z0:传输线特性阻抗

该匹配方式要求RD与RT的和近似等于传输线阻抗

优点:

只要一个电阻

没有多余直流功耗

消除驱动端二次反射

不受接收端负载变化影响

缺点:

接收端一次反射依然存在

信号边沿会有一些变化

电阻靠近驱动端,不适合双向传输

线上传输电压是驱动端一半,不适合菊花链多型负载结构

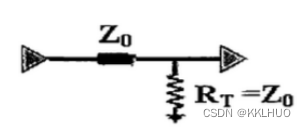

远端并联端接:

优点:

适用多个负载

只要一个电阻,阻值容易选取

缺点:

增加直流功耗

上拉或下拉,使得低电平升高或高电平降低,减小噪声容限

3.蛇形走线主要作用,哪些情况下使用

作用:补偿“同一组相关”信号线中延时较小的部分;

场景:等长时序匹配,阻抗匹配,滤波,接收天线,电感,保险丝

4.DDR过冲和下冲如何解决

过冲:第一个峰值或谷值超过设定电压

下冲:第二个峰值或谷值超过设定电压

反射会导致过冲,下冲,振铃,边沿迟缓

对于双向IO信号,例如DQ,串行端接电阻Rs放置在走线的中间,用来抑制振铃,过冲和下冲。

5.阻抗,等长,等距影响

阻抗--->反射(差分阻抗一致,减少反射)

等距--->串扰(差分信号时刻保持相反极性,减少共模分量)

SI--->信号反射,串扰,信号延迟,时序误差

反射--->信号波形过冲,下冲--->振铃现象(下冲:噪声容限减小,振铃:增大信号稳定所需时间,影响时序)

串扰:相邻传输线电磁能量通过互容与互感耦合产生噪声干扰(兼容性串扰:互相容许触发耦合电流;感受性串扰:互感触发耦合电压)

信号延迟和时序错误:时序错误和逻辑器件功能絮乱

高频信号总是沿着电感最小的回路进行回流

电磁场能量随距离呈平方递减,超过4倍线宽,干扰微弱,可以忽略

不同层产生阻抗,过孔差别破坏差模传输,引入共模噪声,相邻2层耦合密度不够,降低差分走线抵抗噪声能力,相距500mil差分走线,3m外辐射能量衰减60dB,满足FCC电磁辐射标准

6.一段导线串联电阻阻抗怎么计算

容抗:Xc=1/(2πfC);

感抗:XL=2πfL;

X=XL-Xc

阻抗:Z=(R^2+X^2)^(1/2)

阻抗:Z=f*XL+Xc/f+R

单位:XL/XL(omh),频率(Hz),容值(F),电感值(H)

7.阻抗匹配用什么软件

Polar SI9000V7.1

8.SI仿真用什么软件

PCB仿真软件:Sigrity(Cadence),Hyperlynx(Mentor)

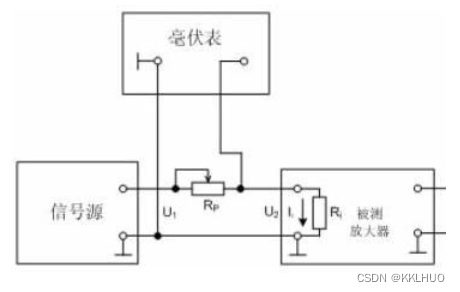

9.测量阻抗方法

低频:半电压法

测输入阻抗,串电位器Rp,电位器两端的电压为信号源输出电压一半,近似认为电位器电阻为输入阻抗(欧姆定律,芯片内阻Ri和Rp相同时,电压和内阻两端电压相同)

高频:扫频测试,网络分析

4969

4969

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?