封装类型:

贴片元器件封装形式是半导体器件的一种封装形式。表面贴片技术(SMT) 所涉及的零件种类繁多,有许多已形成业界通用标准,这主要是一些芯片电容电阻等;有许多仍在不断的变化,尤其是 IC 类零件,其封装形式层出不穷,传统的引脚封装正在经受着新一代封装形式(BGA、FLIP CHIP等等)的冲击。

SOP/SOIC封装

SOP是英文SmallOutlinePackage的缩写,即小外形封装。SOP封装技术由1968~1969年菲利浦公司开发成功,以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等。

DIP封装

DIP是英文DoubleIn-linePackage的缩写,即双列直插式封装。插装型封装之一,引脚从封装两侧引出,封装材料有塑料和陶瓷两种。DIP是最普及的插装型封装,应用范围包括标准逻辑IC,存贮器LSI,微机电路等。

PLCC封装

PLCC是英文PlasticLeadedChipCarrier的缩写,即塑封J引线芯片封装。PLCC封装方式,外形呈正方形,32脚封装,四周都有管脚,外形尺寸比DIP封装小得多。PLCC封装适合用SMT表面安装技术在PCB上安装布线,具有外形尺寸小、可靠性高的优点。

TQFP封装

TQFP是英文thinquadflatpackage的缩写,即薄塑封四角扁平封装。四边扁平封装(TQFP)工艺能有效利用空间,从而降低对印刷电路板空间大小的要求。由于缩小了高度和体积,这种封装工艺非常适合对空间要求较高的应用,如PCMCIA卡和网络器件。几乎所有ALTERA的CPLD/FPGA都有TQFP封装。

PQFP封装

PQFP是英文PlasticQuadFlatPackage的缩写,即塑封四角扁平封装。PQFP封装的芯片引脚之间距离很小,管脚很细,一般大规模或超大规模集成电路采用这种封装形式,其引脚数一般都在100以上。

TSOP封装

TSOP是ThinSmallOutlinePackage的缩写,即薄型小尺寸封装。TSOP内存封装技术的一个典型特征就是在封装芯片的周围做出引脚,TSOP适合用SMT技术(表面安装技术)在PCB(印制电路板)上安装布线。TSOP封装外形尺寸时,寄生参数(电流大幅度变化时,引起输出电压扰动)减小,适合高频应用,操作比较方便,可靠性也比较高。

BGA封装

BGA是英文BallGridArrayPackage的缩写,即球栅阵列封装。90年代随着技术的进步,芯片集成度不断提高,I/O引脚数急剧增加,功耗也随之增大,对集成电路封装的要求也更加严格。为了满足发展的需要,BGA封装开始被应用于生产。

元器件尺寸

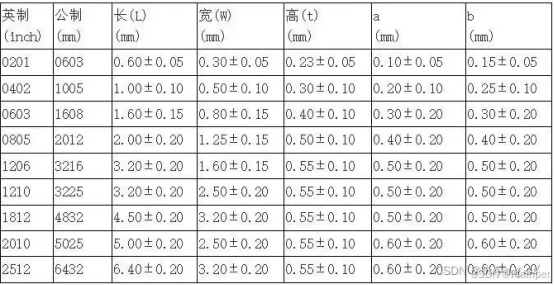

贴片电阻常见封装有9种,用两种尺寸代码来表示。一种尺寸代码是由4位数字表示的EIA(美国电子工业协会)代码,前两位与后两位分别表示电阻的长与宽,以英寸为单位,我们常说的0603封装就是指英制代码。另一种是米制代码,也由4位数字表示,其单位为毫米。下表列出贴片电阻封装英制和公制的关系及详细的尺寸。

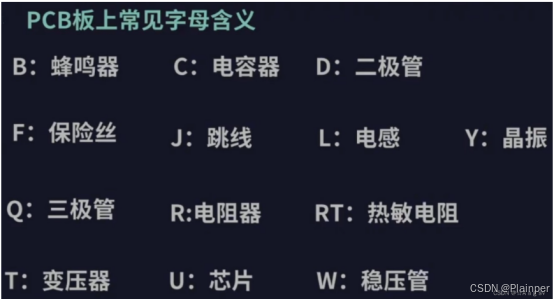

常见电子元器件

想知道常用的电子元器件用什么字母表示?Y又代表什么元件?以下就是电子元器件的这方面的知识清单。

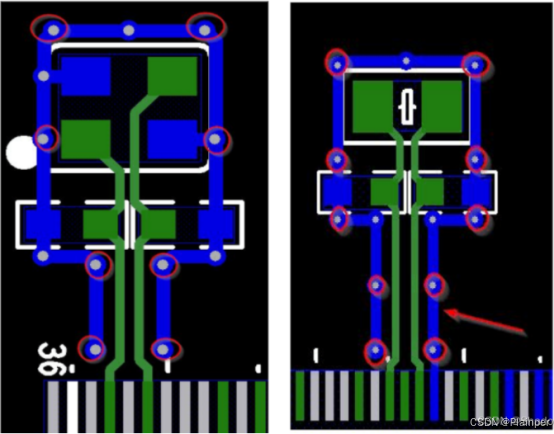

晶振电路PCB设计规则

1.整体电路尽量靠近MCU

2.走线间距大于等于3倍线宽

3.晶体的一对线要走成类差分的形式,线尽量短、且要加粗并进行包地处理,且包地线或者铜皮要打屏蔽地孔,防信号干扰

4.π形走线

5.电路下面不能布信号线

6.和 IC 布在同一层面,这样可以少打孔

7.走线要加粗,通常 8~12mil

8.晶振不能距离板边太近,晶振的外壳必须接地

PCB设计当中重要的3W原则你知道吗?

一、前言

在PCB设计中,对于强干扰信号线和对干扰很敏感的信号线产生的串扰,会存在于走线之间,这种不良影响不仅与时钟或周期信号有关,而且也会对系统中其他的重要走线,数据线、地址线、控制线和IO产生影响。问题的大多数来自时钟和周期信号,它们间的串扰将引起其他部分的功能性问题。

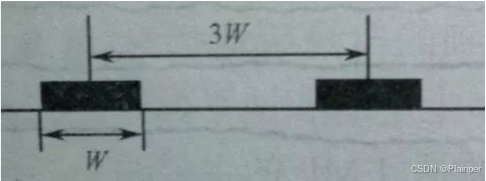

二、3W原则的概念

所以在时钟走线、差分线、视频、音频,复位线,以及其他系统关键电路等,多个高速信号线长距离走线的时,为了减少线与线之间的串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持大部分电场不互相干扰,这就是3W规则。如下图所示。

满足3W原则能使信号间的串扰减少70%,而满足10W则能使信号间的串扰减少近98%.

三、3W原则成立条件

3W原则虽然易记,但要强调一点,这个原则成立是有先前条件的。

从串扰成因的物理意义考量,要有效防止串扰,该间距与叠层高度、导线线宽相关。

对于四层板,走线与参考平面高度距离(5~10mils),3W是够了;

但兩层板,走线与参考层高度距离(45~55mils),3W对高速信号走线可能不够。

3W原则一般是在50欧姆特征阻抗传输线条件下成立。

3W原则是指多个高速信号线长距离走线的时候,其间距应该遵循3W原则,例如时钟线,差分线,视频、音频信号线,复位信号线及其他系统关键电路需要遵循3W原则,而并不是板上所有的布线都要强制符合3W原则

【解析】为什么要进行阻抗匹配?

一、什么是阻抗

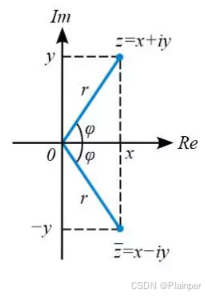

在电学中,常把对电路中电流所起的阻碍作用叫做阻抗。阻抗单位为欧姆,常用Z表示,是一个复数Z= R+i( ωL–1/(ωC))。具体说来阻抗可分为两个部分,电阻(实部)和电抗(虚部)。其中电抗又包括容抗和感抗,由电容引起的电流阻碍称为容抗,由电感引起的电流阻碍称为感抗。

图1 复数表示方法

二、阻抗匹配的重要性

阻抗匹配是指信号源或者传输线跟负载之间达到一种适合的搭配。阻抗匹配主要有两点作用,调整负载功率和抑制信号反射。

1、调整负载功率

假定激励源已定,那么负载的功率由两者的阻抗匹配度决定。对于一个理想化的纯电阻电路或者低频电路,由电感、电容引起的电抗值基本可以忽略,此时电路的阻抗来源主要为电阻。如图2所示,电路中电流I=U/(r+R),负载功率P=I*I*R。由以上两个方程可得当R=r时P取得最大值,Pmax=U*U/(4*r)。

2、抑制信号反射

当一束光从空气射向水中时会发生反射,这是因为光和水的光导特性不同。同样,当信号传输中如果传输线上发生特性阻抗突变也会发生反射。波长与频率成反比,低频信号的波长远远大于传输线的长度,因此一般不用考虑反射问题。高频领域,当信号的波长与传输线长出于相同量级时反射的信号易与原信号混叠,影响信号质量。通过阻抗匹配可有效减少、消除高频信号反射。

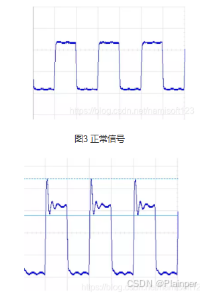

图3 正常信号

图3 正常信号

图4 异常信号(反射引起超调)

三、阻抗匹配的方法

阻抗匹配的方法主要有两个,一是改变组抗力,二是调整传输线。

改变阻抗力就是通过电容、电感与负载的串并联调整负载阻抗值,以达到源和负载阻抗匹配。

调整传输线是加长源和负载间的距离,配合电容和电感把阻抗力调整为零。此时信号不会发生发射,能量都能被负载吸收。高速PCB布线中,一般把数字信号的走线阻抗设计为50欧姆。一般规定同轴电缆基带50欧姆,频带75欧姆,对绞线(差分)为85-100欧姆。

四、阻抗匹配的应用

1、功放与音箱

无论是定阻抗式还是定电压式输出的功放,只有喇叭的总功率和功放的总功率相等时才能得到最佳的工作状态。音箱系统若要完全达到匹配是非常困难的,它的音频成分总是在不停的变化,好在音箱系统对阻抗匹配度要求并不高。最常见到的喇叭阻抗的标示值是8欧姆,它表示当输入1KHz的正弦波信号,它呈现的阻抗值是八欧姆;或者是在喇叭的工作频率响应范围内,平均阻抗为8欧姆。

2、PCB走线

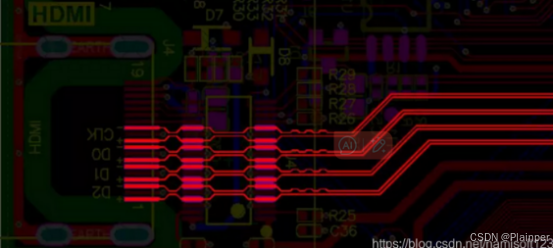

高频领域中,信号频率对PCB走线的阻抗值影响非常大。一般来说当数字信号边沿时间小于1ns或者模拟信号频率超过300M时就要考虑阻抗问题。PCB走线阻抗主要来自寄生的电容、电阻、电感系数,主要因素有材料介电常数、线宽、线厚乃至焊盘的厚度等。PCB 阻抗的范围是 25 至120 欧姆,USB、 LVDS、 HDMI、 SATA等一般要做85-100欧姆阻抗控制。

图6 走线匹配阻抗

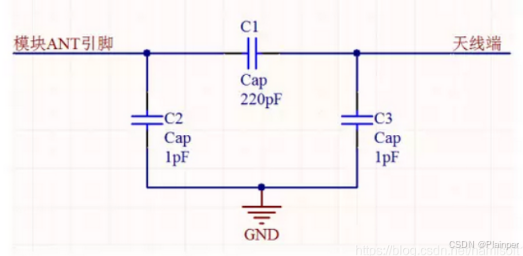

3、天线设计

研究天线阻抗的主要目的是为实现天线和馈线间的匹配。发射信号时应使发射天线与馈线的特性阻抗相等,以获得最好的信号增益。接收信号时天线与负载应做共轭匹配,接收机(负载)阻抗一般认为只有实数部分,因此需要用匹配网络来除去天线的电抗部分并使它们的电阻部分相等。图7为天线阻抗匹配时常用的π型网络,使用网络分析仪测量阻抗以确定 C1、C2、C3 的取值,完成阻抗匹配。

图7 π型电路

4、终端匹配电阻

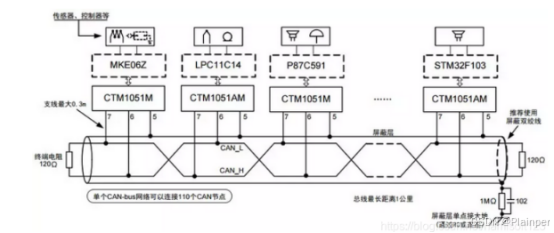

Namisoft在设计CAN总线、485总线时常需要在差分线两端加终端电阻(匹配电阻),以减少由特性阻抗突变造成的信号反射。如下图CAN总线网络,双绞线特性阻抗为120欧姆,若不加终端电阻两端直接悬空,空气的特性阻抗为无穷大。此时,极易出现图4所示的信号反射。

图8 CAN总线网络

对于CAN总线来说,由于收发器对信号电平判断的采样点位置普遍靠后,因此信号反射一般不会影响通信错误率。反射会影响产品的EMI特性,最直接的表现就是眼图实验效果差,存在两个异常凸起。

图9 CAN总线眼图

M6G2C-256LI 核心板,主要器件由 MPU、 DDR、 Flash、 power 四部分构成,看似简单的架构又是如何保证核心板的稳定性呢?差分蛇形走线、等长控制、阻抗匹配、 PCB 分层设计、高速信号参考地等设计来保证产品的设计合理性,再配合信号完整性、信号眼图、信号脉冲等等仪器测试为产品稳定性保驾护航。

2191

2191

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?