网站是这个 HDLBits.

0 不会吧看不懂英文?

这是翻译过来的 .

非常感谢这位博主!!!!!!

然后挨着翻看,都有翻译的👍

1 简介

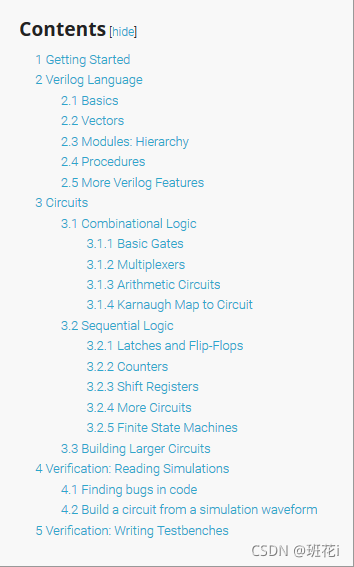

1.1 刷题目录

这是HDLBits整理的刷题内容的目录

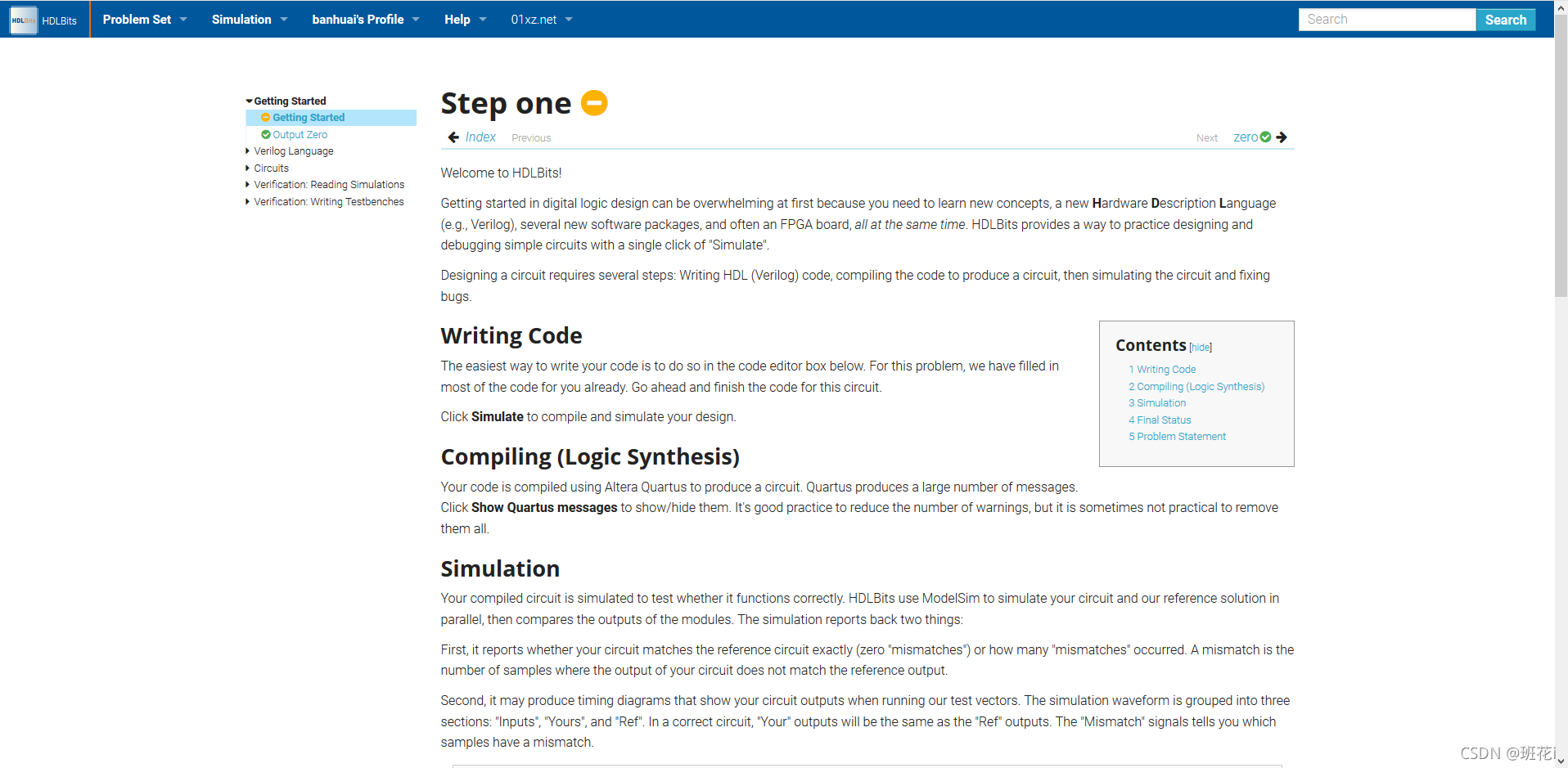

1.2 简介摘要(以官方给的讲解为例)

HDLBits提供了一种方法来练习设计和调试简单的电路,只需单击“Simulate”即可。

设计一个电路需要几个步骤:编写HDL (Verilog)代码,编译代码生成电路,然后仿真电路并修复bug。

2 使用

以下直接以一个例子来讲解,建议开着HDLBits的

Getting Started.

一起操作

2.1 界面

部分内容的讲解会融合在例子的步骤里面

因为这是第一篇引入的文章,所以说前面这是一些介绍,每个功能板块的

Problem Statement 是问题的描述

我们将从少量的HDL开始,以熟悉HDLBits使用的接口。这里这个练习是你需要完成的电路描述:

建立一个没有输入只有输出的电路。输出应该总是驱动1(或逻辑高)。

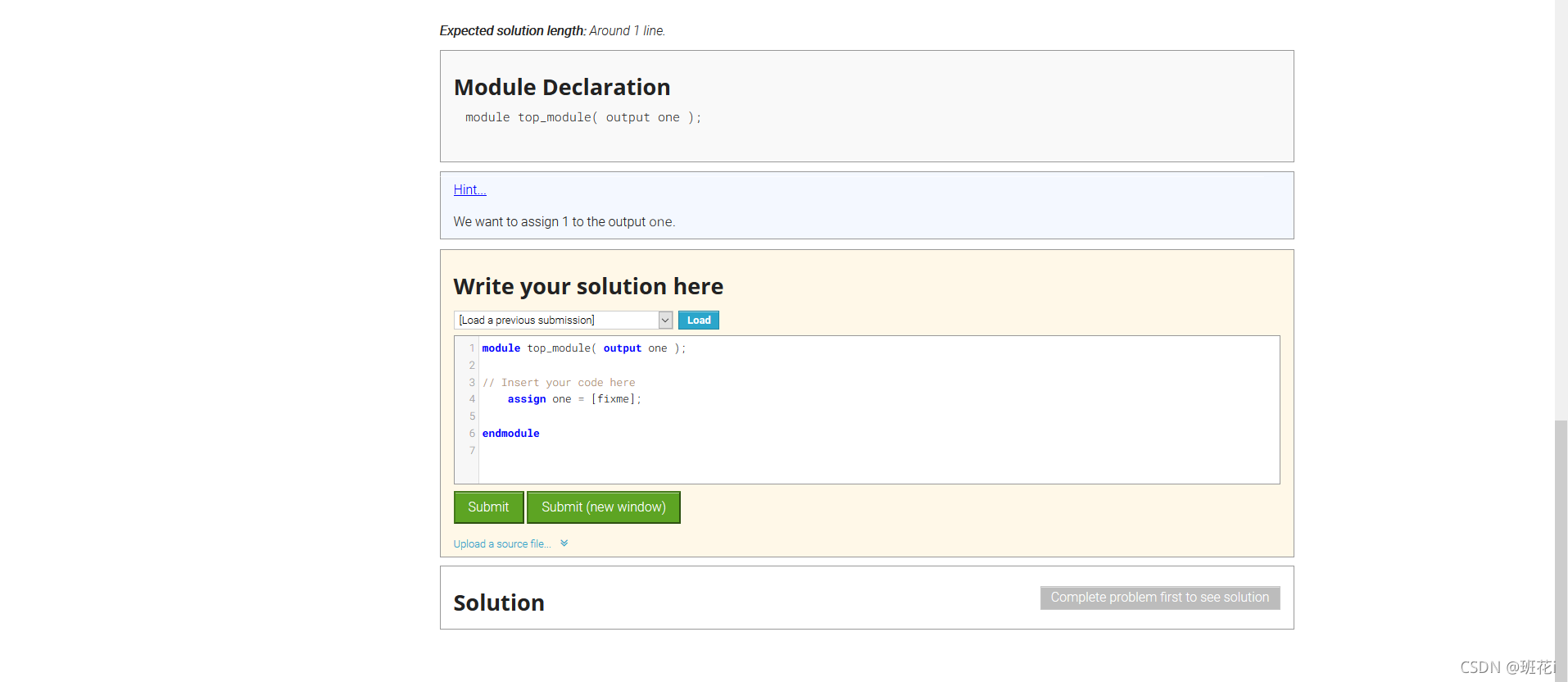

从下一张图开始就是以后刷题的基本界面了

Module Declaration是你要编写的代码的模板

Module Declaration是你要编写的代码的模板

Hint是提示

这儿就是官方给出的模板,你只需要在这个基础上去填充即可

module top_module( output one );

// Insert your code here

assign one = [fixme];

endmodule

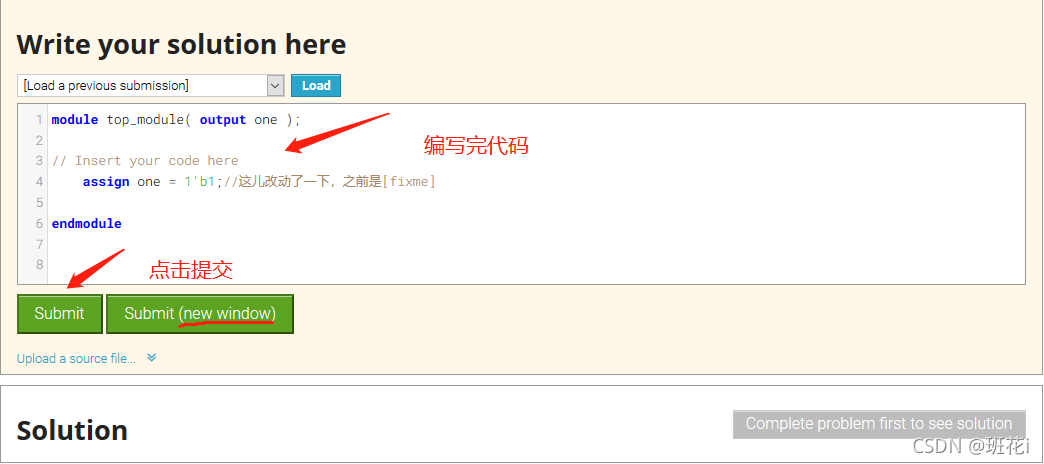

2.2 开始刷题

从Problem Statement可以知道题目:建立一个没有输入只有输出的电路。输出应该总是驱动1(或逻辑高)。

根据Module Declaration给出的代码的模板

我写出了这样的程序

比如我这是我现在的

module top_module( output one );

// Insert your code here

assign one = 1'b1;//这儿改动了一下,之前是[fixme]

endmodule

2.3 提交

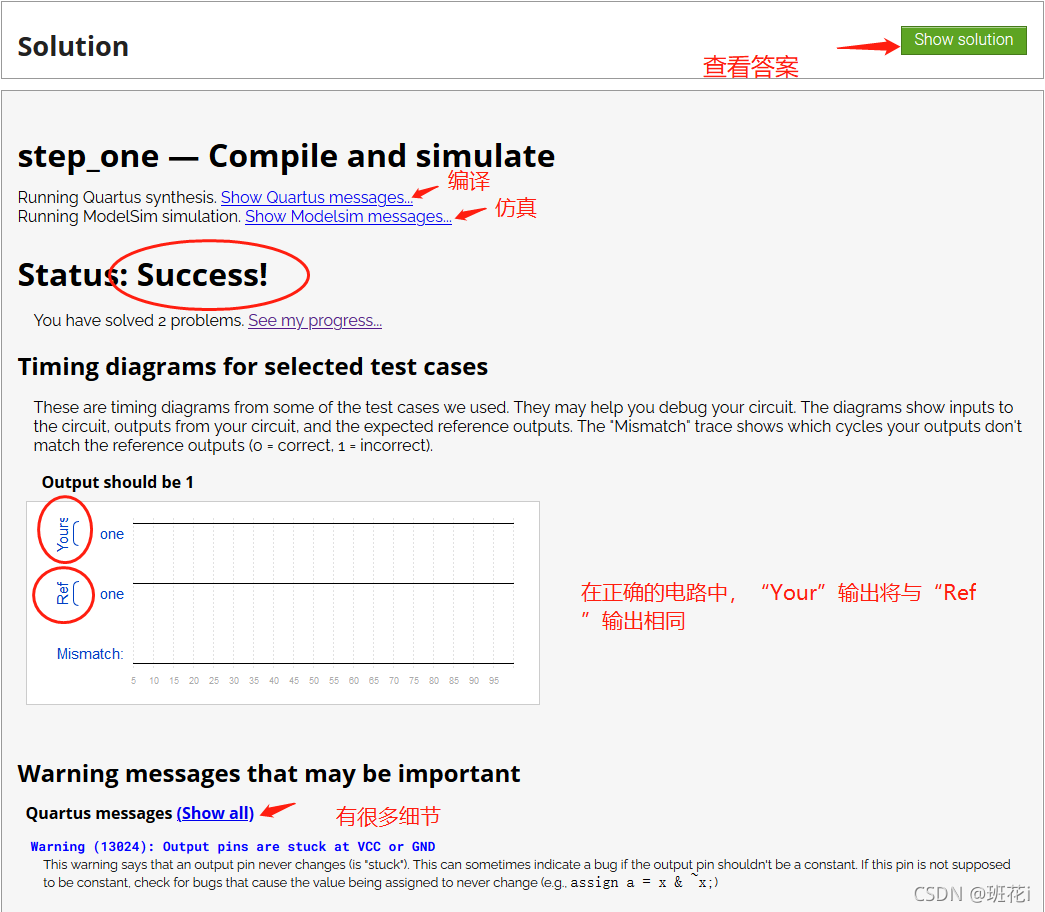

2.4 提交之后

提交代码之后,你能及时的看到编译结果和仿真结果,如果不会,还能够查到参考答案

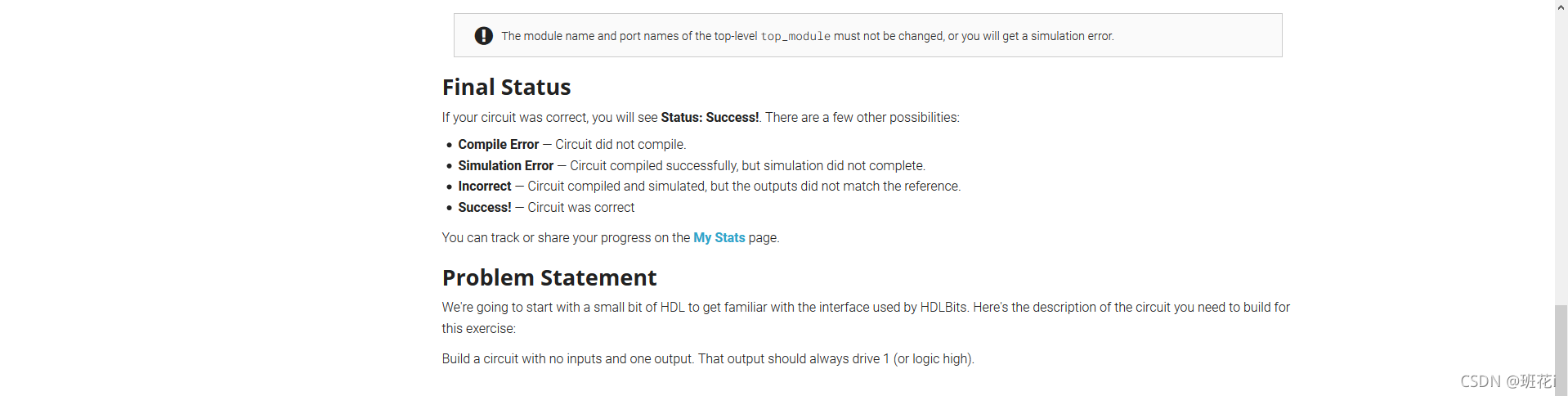

如果你的电路是正确的,你将看到的状态:Success! 还有一些其他的可能:

· Compile Error——电路没有编译。

· Simulation Error——电路编译成功,但仿真没有完成。

· Incorrect ——电路编译和仿真成功,但输出与参考不匹配。

· Success!——电路是正确的。

你可以在My Stats页面上跟踪或分享你的进度。

Quartus产生大量的信息。单击“Show Quartus messages”以显示/隐藏它们。

Simulation

模拟编译后的电路,以测试其功能是否正确。HDLBits使用ModelSim并行仿真你的电路和我们的参考解决方法,然后比较模块的输出。模拟报告了两件事情:

首先,它报告您的电路是否与参考电路完全匹配(零“mismatches”)或发生了多少“mismatches。不匹配是指电路的输出与参考的输出不匹配的样本数量。

其次,它可能产生时序图,显示你的电路输出时,运行我们的测试向量。仿真波形分为三个部分:“Inputs”, “Yours”, and “Ref”。在正确的电路中,“Your”输出将与“Ref”输出相同。“Mismatch”信号告诉你哪些样本不匹配。

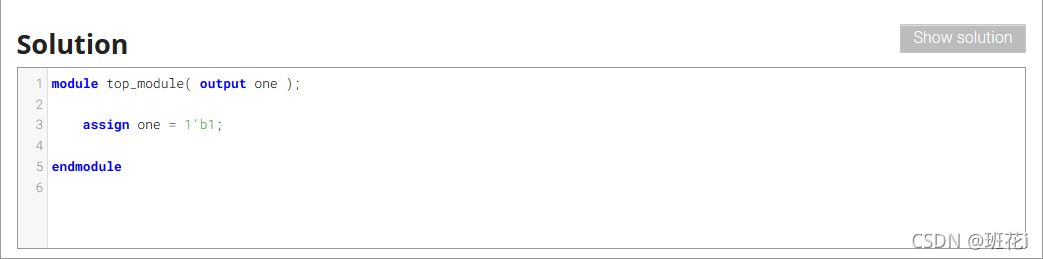

2.5 参考答案

还可以CSDN!!

994

994

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?