一、状态机

二、RTL模拟电路

得到RTL图如下:

assign是组合逻辑的语句;

always是时序逻辑的语句;

reg语句用于使用寄存器;

wire一般用于线网的连线用法

三、modelsim仿真全过程:

1)编写.v文件

2)配置EDA tool settings,点击 start 的 test bench 生成.vt文件

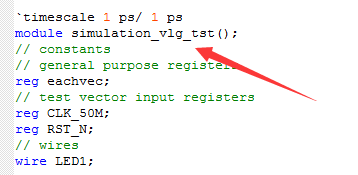

3)修改要测试的testbench的测试内容(搭建测试平台)

4)配置simulation的.vt文件

是这个模块名

5)进行仿真

四、任务和函数

根据Verilog DHL语言标准来看,task必须在always里面调用,task本身可以调用task,但不能调用module。module的调用是和always、assign语句并列的,所以在这些语句中均不能直接调用module,只能采用和module端口交互数据的方法达到调用的功能。

task语句是可综合的,但其中不能包含always语句,因此也只能实现组合逻辑。***顺序调用task对于电路设计来说,就是复制电路功能单元。***多次调用task语句就是多次复制电路,因此资源会成倍增加,不能达到电路复用的目的;同时用task封装的纯逻辑代码会使得电路的处理时间变长,最高频率降低,不能应用与高速场合。

综上所述,可以看出task语句的功能就是将代码中重复的组合逻辑封装起来简化程序结构,具备组合逻辑的所有有点和缺点,而对于时序设计,task语句无法处理,只能通过Verilog HDL语言中的层次化设计方法,将其封装成module,通过端口交换数据来达到简化程序结构的目的。

而function是可综合的,但由于function语句中不支持使用always语句,因此无法捕获先好跳变沿,所以不能实现时序逻辑。和task一样,function拥有组合逻辑电路的所有优点和缺点。(本段摘选CSDN博主「在路上的少年」https://blog.csdn.net/duhanting/java/article/details/10326405的总结)

即Function就是函数设计,和task一样具有封装组合逻辑代码作用,这两个在Testbench用的多一些,在module里面,请不要使用。

补充一个消抖的延时代码:

若发现reg的键值和按下不一致,即发生了抖动,此时延时20毫秒消抖;如果发现键值和按下的保持一致,则不用管它。

以下程序段实现拍了两拍的延迟输出,并输出一个上升沿。

可以看到将外界输入的电平转化成一个脉冲信号:

2111

2111

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?