目录

(二)DELAYLINE INTERPOLATION(典型的基于延迟链的插值技术)

(三)INTERPOLATION PRECISION(影响测量时间间隔精度的因素: 量化噪声、积分非线性、随机噪声)

4、时间间隔测量结果中INL误差随测量时间和时间间隔长度变化。

(四)HIGH-PRECISION INTERPOLATION(四种高精度TDC插值技术: 参考循环结构、多级插值技术、亚门级延迟链、INL查找表校验(码密度校验))

2、使用多级插值可以在延迟单元和存储器较少的情况下提高插值率。

(五)TWO-LEVEL RECYCLING REFERENCE TDC(本项目两级循环参考TDC结构)

(零)摘要

设计了一种高精度CMOS时间-数字转换器IC。时间间隔测量基于计数器和由稳定延迟线实现的两级插值。延迟线中的参考循环改善了插值器的积分非线性,并允许使用低频参考时钟。多级插值减少了延迟元件和寄存器的数量,并降低了功耗。延迟线中的负载电容器缩放并联结构允许非常高的分辨率。INL查找表减少了剩余非线性的影响。数字化电路以8.1 ps rms单次激发精度测量从0到204 s的时间间隔。5MHz外部参考时钟的分辨率为12.2 ps,仅通过20个延迟元件进行划分。

(一)INTRODUCTION(研究背景、项目创新点介绍)

一、TDC应用:

高精度时间间隔测量系统通常用于各种特殊的工业应用。例如,电信、核科学、频率合成、示波器和逻辑分析仪等测量设备,以及脉冲激光飞行时间测量,都利用了时间-数字转换器(TDC)或其他形式的时间间隔测量,所获得的性能在很大程度上取决于此类测量的精度。

二、研究现状:

1、许多模拟/数字插值方法可用于精确时间间隔测量。集成的基于延迟线的插值架构效果很好,通过稳定的延迟线将外部参考时钟周期划分为数百个等大小的时间间隙,可实现几十ps的单次触发精度

2、简单的直接计数参考时钟的周期数的分辨率取决于周期长度,如果提高精度就需要提高时钟频率(对振荡器要求高,功耗大),内插值的测量方法可以降低对参考时钟的要求,而且精度较高。

3、高精度时间间隔测量要求插值电路:高分辨率 良好线性度

(1)量化噪声:取决于LSB,限制单次测量结果精度

(2)INL积分非线性:由PVT引起,INL随延迟链增长而增加(数学模型),造成单次测量结果有误差

(3)随机噪声

4、异步测量使连续时间间隔的平均成为提高精度的有效方法。这种提高与平均结果的平方根呈反比。平均还减少了插值非线性对最终精度的影响。然而插值器的非线性表现在记录的单次结果分布的波动中,常用其sigma值表示测量精度。

三、本项目要做的工作:

1、目标:

高精度(量化噪声、INL小)TDC(CMOS)。

2、平衡:

采用低频(10MHz)参考时钟简化芯片使用和降低功耗;由于低参考频率的高分辨率插值会使插值比率很高,这可能导致延迟单元链很长,从而导致INL增加,精度有所下降,同时过长的延迟链也会增大芯片面积。

3、解决思路:

(1)参考回收循环降低延迟链长度;

(2)多级插值提高分辨率,减少延迟单元数量,降低功耗;

(3)基于并行缩放延迟单元的延迟线减小LSB;

(4)INL查找表校验剩余的非线性。

(二)DELAYLINE INTERPOLATION(典型的基于延迟链的插值技术)

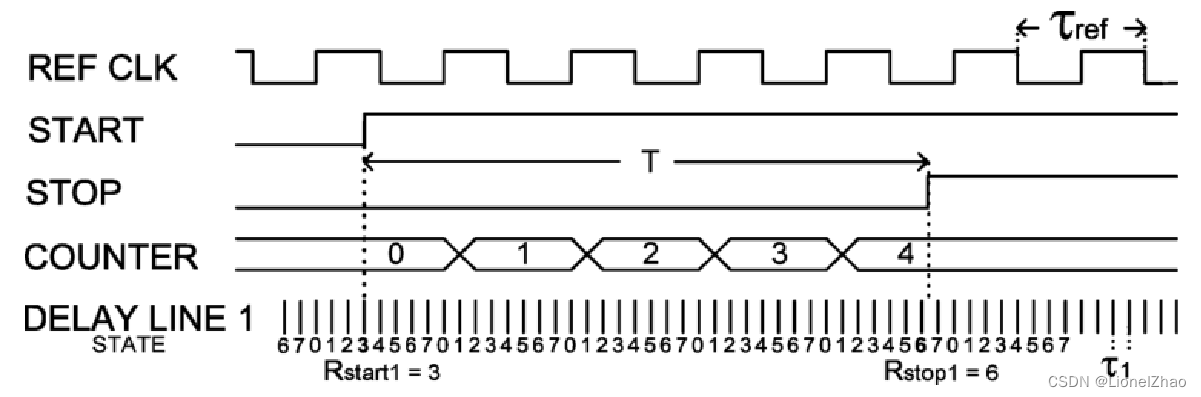

一、时间间隔的计算

1、延迟链将一个时钟周期![]() 分为8份(每一份的时间长度为

分为8份(每一份的时间长度为![]() 状态用0,1,……,7表示),表征细测量时间长度。

状态用0,1,……,7表示),表征细测量时间长度。

2、计数器由START信号启动、STOP信号终止,一个参考时钟周期递增一次,总共![]() 次,表征粗测量时间长度。

次,表征粗测量时间长度。

3、时间间隔计算公式: ![]()

![]() -----STOP信号到来时延迟链的状态

-----STOP信号到来时延迟链的状态

![]() -----START信号到来时延迟链的状态。

-----START信号到来时延迟链的状态。

二、实现原理

1、构成

(1)计数器:对START、STOP之间的参考时钟周期计数

(2)延时单元和D触发器链:将一个参考时钟周期分为若干份,通过温度计编码表征细测量时间的状态;延迟线的长度与参考时钟相匹配。

(3)延迟锁相环DLL和环路滤波器(包含鉴相器和电荷泵):延迟单元延迟时间受PVT影响,DLL与环路滤波器配合稳定延迟线中的延迟。DLL通过 调整延迟单元的延迟时间,直到鉴相器在其输入端检测到同步定时信号边缘,这意味着延时链总时长与参考时钟周期匹配。

结构示意如👆图, 此结构存在的问题:分辨率LSB取决于单个延迟单元的延迟时间(门级),但是我们要实现亚门级的分辨率。

(三)INTERPOLATION PRECISION(影响测量时间间隔精度的因素: 量化噪声、积分非线性、随机噪声)

一、影响插值器精度的因素

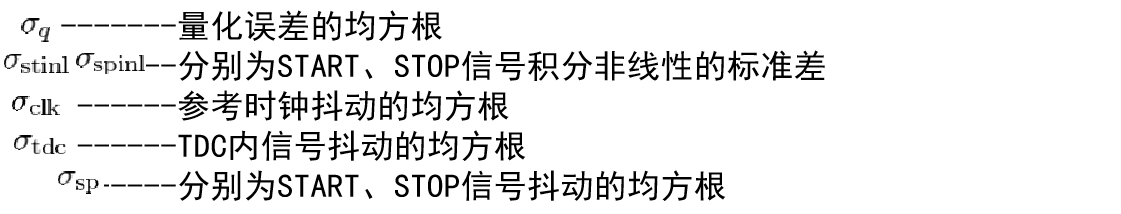

1、影响插值器精度的因素有:量化噪声、非线性、(以及设备的随机噪声)

2、测量时间间隔的异步信号(START、STOP)的两次插值均包含量化噪声和非线性

3、精度的数学模型:

(1)对同一个时间间隔的大量测量结果的标准差表征插值器的精度。由于该精度也取决于时间间隔的绝对长度,因此最好以平均值周围最小、最大、和均方根标准差来表示精度的波动。

(2)单次测量精度的均方根定义了整个插值区域内插值器精度的均方根,当使用计数器和基于DLL的稳定延迟链进行插值时有:

由上式可以得出:提高分辨率无法实现精度的显著提高 (例如:插值器的INL占主导地位,精度不随分辨率的提高而缩小)

二、量化误差/噪声

1、定义:

由有限的插值分辨率LSB引起的误差

2、影响因素:

(1)测量的时间间隔由START、STOP所界定,每次插值都有误差,因此量化误差在单个测量结果中表现为最大![]() 的不确定性,如下图所示:

的不确定性,如下图所示:

(2)由量化噪声引入的平均误差取决于时间间隔。时间间隔T可以用LSB表示,当每个延迟单元延迟时间为![]() ,整数部分为

,整数部分为![]() ,分数部分为

,分数部分为![]() 时,有时间间隔为:

时,有时间间隔为:![]() ;单次测量结果标准差也受F影响,用下式表征:

;单次测量结果标准差也受F影响,用下式表征:![]() 分数F对测量结果的影响如下图所示:当F接近0.5的时候(此时分数部分时间为LSB的一半),达到最差的精度,通过在一个周期内对

分数F对测量结果的影响如下图所示:当F接近0.5的时候(此时分数部分时间为LSB的一半),达到最差的精度,通过在一个周期内对![]() 积分可以得到均方误差为

积分可以得到均方误差为![]()

(3)量化噪声可通过提高插值分辨率来降低(减小延迟单元的延迟时间)但级联延迟线的分辨率取决于PVT,理论上最小时间为每一个延迟单元的延迟时间。在数字逻辑电路中,延迟单元可以由缓冲器(两个串联的非门)构成(再减小受限于PVT、成本)。 通过使用差分延迟链结构,可以实现几乎一半的单元延迟时间(分辨率、LSB)。同时对可调性的需求也增加了元件的延迟,这将时间分辨率限制再几百ps或几十ps(即使使用最先进的CMOS技术)。

三、积分非线性(INL)

1、定义:

由延迟单元延迟时间不同积累产生测量结果的非线性,其示意图如下:

(理想线性) (现实非线性)

2、影响因素:

导致微分非线性DNL的因素,DNL积累产生INL

(1)PVT:半导体工艺、电压波动、温度影响……

(2)布局布线

(3)噪声源的随机变化:如系统性干扰信号传播、系统电源电压噪声……

3、DLL对INL的作用:

DLL稳定系统将延迟线的总延迟与参考时钟周期匹配,并且INL从延迟链起始端开始积累。由于最后一个延迟与鉴相器的参考匹配,因此经过鉴相器匹配后INL清零(但是在后续传播还会继续产生)。由于DLL稳定,INL的期望在延迟链中间达到最大值,其标准差为:![]() ;

;![]() ---延迟单元延迟时间的标准差 n---延迟链中延迟单元的数量

---延迟单元延迟时间的标准差 n---延迟链中延迟单元的数量

由上式可以得出:INL取决于延迟单元延迟时间的方差和延迟链的长度。

4、时间间隔测量结果中INL误差随测量时间和时间间隔长度变化。

含有100个延迟单元的延迟链中INL随延迟单元的变化如下图所示: 相对100ps时间间隔平均值有2%误差,最大误差为23ps。

5、值得注意的是:

当时间间隔为插值时间周期的整数倍的时候,INL误差将从测量结果中消失,因为两次插值都包含了相同的INL误差,这将在总结果中抵消。 INL的标准差揭示了INL对插值器精度的平均影响。

四、随机噪声

1、定义:

测量时间间隔受到的随机非系统噪声而引起的误差。

2、影响因素:

(1)参考时钟的相位噪声

(2)延迟单元延迟受到延迟链控制和电源电压噪声的影响……

3、DLL延迟链架构:

(1)随机噪声引起的延迟误差随着延迟链信号传播而积累

(2)鉴相器同步参考时钟信号可以使“新的干净的”(没有随机噪声、脉冲边沿陡峭无倾斜和陡峭)边沿进入延迟链从而消除累积的噪声。

(3)START、STOP信号也可能有抖动,而噪声和上升时间的变化可能会改变时间信号记录的输入时刻。(没太明白这句话啥意思(-_-),是不是在说上升沿受到噪声印象导致测量值变化)

(四)HIGH-PRECISION INTERPOLATION(四种高精度TDC插值技术: 参考循环结构、多级插值技术、亚门级延迟链、INL查找表校验(码密度校验))

一、高精度插值技术

1、矛盾与平衡:

中可以看出:时间-数字转换的精度受到量化噪声、INL、抖动等许多因素的影响(在 中比较详细的介绍了)。高精度要求高分辨率,高分辨率降低量化噪声;但直接实现的分辨率受到数字端口传播延迟的限制。同时高精度要求低非线性,INL应当最小化,但INL随着延迟链的增长了增大。为了提高适用范围和降低功耗要求低的参考时钟频率,但是传统插值在低参考时钟频率同时保持高精度(LSB小)需要长延迟链,造成面积消耗和INL非线性。可以用下图表示:

中可以看出:时间-数字转换的精度受到量化噪声、INL、抖动等许多因素的影响(在 中比较详细的介绍了)。高精度要求高分辨率,高分辨率降低量化噪声;但直接实现的分辨率受到数字端口传播延迟的限制。同时高精度要求低非线性,INL应当最小化,但INL随着延迟链的增长了增大。为了提高适用范围和降低功耗要求低的参考时钟频率,但是传统插值在低参考时钟频率同时保持高精度(LSB小)需要长延迟链,造成面积消耗和INL非线性。可以用下图表示:

二、参考回收循环结构:

1、循环过程:

将已经通过延迟链传播的参考时钟边缘再循环回到其输入,在一定数量的循环之后引入来自参考时钟源的新的无抖动的信号到延迟链中进行下一轮的循环。

2、经典参考循环结构及原理:

(1)结构:由计数器及多路选择器、环形振荡器、鉴相器及电荷泵等构成。

(2)原理:这种延迟线架构以循环倍频DLL的形式呈现。

延迟线由奇数个可调延迟反相器构成;多路选择器由计数器控制,控制进入延迟线的信号流。

当来自参考时钟的“干净”(抖动、倾斜几乎没有)信号进入延迟链时,多路选择器切换到循环通道,延迟链作为环形振荡器工作。经过一定数量的回收循环(图中为4轮)后计数器设置多路选择器,以允许新的“干净”的参考时钟信号进入延迟链。鉴相器和电荷泵将新输入的信号与已经循环多次的“旧”信号的最后上升沿匹配,以便循环延迟链中的延迟与输入信号循环时间匹配。

3、针对插值改进的参考循环回收技术:

要进行采样的时间插值必须改进以形成具有恒定延迟的时间样本,结构如下图所示:

(1)结构:

延迟链由两个信道差分多路选择器构成,虽然只有第一个元件使用两个信道,但为了保证每个延迟单元延迟时间相同,所有延迟单元都相同。

(2)原理:

由于最后一个单元和第一个单元之间交叉耦合(意思应该是反相),再循环的差分信号每经过一轮以反相顺序再次通过。寄存器REG16暂存差分输出信号表示延迟链的状态。差分循环直到计数器决定输出新的“干净”的参考时钟信号进行下一轮的循环。

(3)优点:

①寄存器REG16从每个延迟单元接受两个时间样本(差分信号),降低功耗并使延迟线有效长度加倍。(说实话这句没明白差分咋就降低了功耗⊙▂⊙)

②插值器循环延迟链结构提高了插值率(interpolation ratio),若延迟链上含有![]() 个延迟单元,一次循环

个延迟单元,一次循环![]() 次,则插值率为:

次,则插值率为:![]()

③插值器循环延迟链结构可以使延迟链更短,可以有效降低INL。INL在每一轮循环结束后清零,即使稳定仅匹配插值周期的开始和结束。

64个延迟单元和16个延迟单元循环4次INL如下图所示:

可以看到参考回收循环延迟链可以有效降低INL

(4)代价:

沿延时链传播过程中信号的随机相位噪声增加。 因此,只有在累积相位噪声开始主导并限制精度之前,才能增加循环次数。

三、多级插值技术

1、单级插值的不足:

所用延迟单元的数量会影响INL(延迟单元数量越多,INL越大),也会影响面积(延迟单元数量越多,面积开销越大)。延迟链的长度可由参考时钟周期 与单个延迟单元的延迟时间 的比值来确定,即延迟元件数量 当采用低频率参考时钟( 非常大)同时要求高分辨率( 非常小)时,N往往非常大,INL大且造成面积的浪费。

2、使用多级插值可以在延迟单元和存储器较少的情况下提高插值率。

如下图所示:

在本图中,首先用四个延迟单元在参考周期时间内对时间信号输入时刻进行插值;然后用四个延迟单元在第一级插值的分辨率内具有更高分辨率功能的另一级插值。由此可以得出第一级分辨率为![]() ,第二级分辨率为

,第二级分辨率为![]() 。两级插值总共用到了4+4=8个延迟单元,相比之下单级插值需要16个延迟单元,这极大节省了延迟单元的数量,减小了面积和功耗。

。两级插值总共用到了4+4=8个延迟单元,相比之下单级插值需要16个延迟单元,这极大节省了延迟单元的数量,减小了面积和功耗。

对于多级插值,总插值率为不同级插值率的乘积。

四、亚门级延迟链

1、传统级联延迟链的不足:

级联延迟单元构成的延迟链可实现的最小分辨率受到延迟单元(buffer)固有延迟时间的限制。

2、并联延迟链:

不同比例的延迟单元之间的延迟差可以远小于单个门的延迟时间,因此可以用并联延迟单元构成的延迟链来实现亚门级的分辨率。结构如下图所示:

(1)每个延迟单元总延迟时间为![]() ,每个单元延迟比前一个延迟单元相差已知时间

,每个单元延迟比前一个延迟单元相差已知时间![]() ,每个单元具有相等的基本延迟

,每个单元具有相等的基本延迟![]() 可以在稍后的信号处理中抵消;延迟单元内的数字表示延迟比例因子。因此,当输入信号触发延迟线时,产生高分辨率的并行时间样本作为输出进行后续处理(后面会讲)。

可以在稍后的信号处理中抵消;延迟单元内的数字表示延迟比例因子。因此,当输入信号触发延迟线时,产生高分辨率的并行时间样本作为输出进行后续处理(后面会讲)。

(2)并联延迟单元中的误差(DNL),不会像级联延迟链结构那样累积。特定时间样本中的INL知识其中的DNL (这里猜测像游标延迟链型TDC利用慢链和快链的时间差,留个疑问看他后面咋讲)

五、INL查找表校验

(感觉就是码密度校验呀,为了证明我还没有忘干净还是赘述下吧)

1、码密度校验原理:

延迟单元的微分非线性(DNL)随着信号在延迟链中的传播逐渐积累引起的非线性误差称为积分非线性(INL)。

如果我们知道每一个延迟单元的延迟时间,就可以准确的计算出有INL下的时间间隔,岂不美哉。 我们可以通过大量随机脉冲(在任何时刻跳变的可能性相同)来统计每个落在每个延迟单元上脉冲的数量(通过建立一个查找表来存放状态编码与对应时间间隔的映射),通过计算就可以得出每个延迟单元的延迟时间。

举个栗子如下:![]()

已知当输入N个足够多的跳变,第i个延迟单元的延迟时间![]() ,落在第i个延迟单元的次数

,落在第i个延迟单元的次数![]() 跳变总数N 、总延迟时间

跳变总数N 、总延迟时间![]() ,则第i个延迟单元的延迟时间为:

,则第i个延迟单元的延迟时间为:![]() ;对前i级延迟单元的延迟时间累加得到随机脉冲到达每一级延迟单元所用的累计时间:

;对前i级延迟单元的延迟时间累加得到随机脉冲到达每一级延迟单元所用的累计时间:![]()

2、通过码密度校验我们可以得出在有非线性情况下的时间间隔啦,这样消除了非线性的影响,但是需要主义的时误差依然可能存在(LSB/分辨率引起的误差)

(五)TWO-LEVEL RECYCLING REFERENCE TDC(本项目两级循环参考TDC结构)

一、设计概述

本项目设计的高精度TDC采用0.35umCMOS技术,使用计数器和两级插值(粗、细),其中细插值也使用两级实现。

参考循环技术将粗插值器中的参考循环最多128次。粗插值器通过在延迟线中对信号进行采样,每循环一轮从参考信号中形成16个时间样本。细插值器将粗插值器的虚时钟周期分为32个具有并行缩放延迟链的段。因此,TDC相对于参考时钟的最大插值率为:128*16*32 = 65536。另一方面,插值只需要使用20个独立延迟单元:粗插值器8个、细插值器第一级4个、细插值器第二季8个。 TDC系统框图如下所示:

组成:

组成:

1、15位计数器

2、粗插值器

3、细插值器

二、回收参考与计时器:TDC时序图如图所示:

1、参考时钟周期![]() 通过循环参考回收技术被DLL分为N份(N为图中可选循环因子,定义为参考时钟周期

通过循环参考回收技术被DLL分为N份(N为图中可选循环因子,定义为参考时钟周期![]() 与粗插值器周期

与粗插值器周期![]() 的比值,即一个参考时钟周期包含N个粗插值器周期).

的比值,即一个参考时钟周期包含N个粗插值器周期).

2、计数器对时间信号之间的延迟链循环的周期进行计数。计数由STRAT启动、STOP终止,计数器的状态代表STOP信号来临循环延迟链的循环次数。 计数器通过同步计数与粗插值器的结果同步,以提供明确的结果(难道还有不明确的时候?我的理解是DLL中的鉴相器检测上升沿同步到延迟链中,使参考时钟周期恰好为粗插值器测量周期的整数倍,就消除了不匹配造成的最后一个粗测量周期不完整的问题)。

三、粗/细插补器

(注意上图(a)与(b)部分单位时间长度不同)

1、如上一张图所示,循环粗延迟线周期![]() 通过每个延迟单元之后采样而被划分为16段,每一段长为

通过每个延迟单元之后采样而被划分为16段,每一段长为![]() ,因此粗插值器延迟线作为虚拟时钟工作,周期为

,因此粗插值器延迟线作为虚拟时钟工作,周期为![]() ;细插值器通过在两级中将

;细插值器通过在两级中将![]() 分为32个时间段(32 = 8(第二级)*4(第一级)),第一级用4个延迟单元将虚拟时钟

分为32个时间段(32 = 8(第二级)*4(第一级)),第一级用4个延迟单元将虚拟时钟![]() 分解为四个周期为

分解为四个周期为![]() 的时间段,第二级用8个延迟单元将第一级周期划分为八个周期为

的时间段,第二级用8个延迟单元将第一级周期划分为八个周期为![]() 的时间段;将第一级的四个状态用S0……S3来表示,将第二级的八个状态用F0……F7来表示,细插值器的状态由SF来表示,因此有4*8=32个状态,从而将

的时间段;将第一级的四个状态用S0……S3来表示,将第二级的八个状态用F0……F7来表示,细插值器的状态由SF来表示,因此有4*8=32个状态,从而将![]() 划分为32个时间段。因此,可以用插值器的状态编码表示插值时间。

划分为32个时间段。因此,可以用插值器的状态编码表示插值时间。

2、细插值器结构如图所示:

(1)细插值器精细分辨率![]() 基于并行可缩放延迟单元之间的差异。 如前文所述,同步信号和定时信号生成具有预定义差值

基于并行可缩放延迟单元之间的差异。 如前文所述,同步信号和定时信号生成具有预定义差值![]() 的定时边缘,这些边沿连接到包含32个仲裁器的仲裁器寄存器组中。仲裁器寄存器组中的值根据参考和时序信号相位之间的时间差交替,这表示 内时序信号的到达时刻。(这个仲裁器是个什么鬼?在图上咋用了SR锁存器表示?)。

的定时边缘,这些边沿连接到包含32个仲裁器的仲裁器寄存器组中。仲裁器寄存器组中的值根据参考和时序信号相位之间的时间差交替,这表示 内时序信号的到达时刻。(这个仲裁器是个什么鬼?在图上咋用了SR锁存器表示?)。

(2)缩放延迟单元的基本延迟时间![]() 从结果中被抵消,因为参考信号线和时序信号线都包含相同的基本延迟。(终于呼应上文留的疑问了呢(-_-)我的理解是:虽然并行延迟链的同一层级的不同延迟单元延迟时间不同(

从结果中被抵消,因为参考信号线和时序信号线都包含相同的基本延迟。(终于呼应上文留的疑问了呢(-_-)我的理解是:虽然并行延迟链的同一层级的不同延迟单元延迟时间不同(![]() 、

、![]() ……

……![]() ),但是就像游标延迟连型TDC一样我们利用的是时间差

),但是就像游标延迟连型TDC一样我们利用的是时间差![]() ,因此并行缩放延迟链延迟单元的延迟时间为

,因此并行缩放延迟链延迟单元的延迟时间为![]() ,消除了

,消除了![]() 的影响)。

的影响)。

(3)细插值结构只有在时间信号到达的时候工作,因此消耗很少的功耗。

四、延迟单元

1、粗插值器延迟单元的结构:

粗插值器中的延迟单元的电路结构如图所示,是个可调差分多路选择器。多路选择器的第二个信道只在第一个单元中需要,但是为了保证所有延迟单元的延迟时间相同,所有的延迟单元都需要用相同的结构,因此都用了可调差分多路选择器作为延迟单元。与单链级联相比,差分结构提高了分辨率。因为时间分辨率在不同情况下应恒定,所以延迟信号必须在延迟单元前后处于同一相位(上升或下降)。(如温度变化会对信号上升和下降时间产生不同的影响,这回扭曲反相信号之间的延迟)

2、差分信号的优点:

差分逻辑包括每个单元输出端的信号及其反相的信号,这些信号可以交替使用,以实现元件前后的相同相位,不需要任何额外的反相元件,而这在单端逻辑中是需要的。因此差分延迟单元的延迟时间几乎是单端延迟单元的一半。同时差分结构也减小了噪声的影响(例如工作电压中的噪声同等的影响两个互补的差分信号)(又一次感受到了来自模集的恐惧,差分结构妙啊)

3、细插值器结构:

细插值器中非常小的延迟差是通过缩放缓冲器的负载电容来实现的,如右图所示。并联延迟原件之间的精确延迟差![]() 是通过在延迟单元中具有特定数量的单元电容负载来实现的(有n个延迟差

是通过在延迟单元中具有特定数量的单元电容负载来实现的(有n个延迟差![]() 就有n个负载电容)。 值得注意的是,在这种由并联延迟单元组成的延迟链中,单个元件的DNL是由相应延迟单元的绝对延迟失配产生的,而不是延迟单元之间的延迟差,因为基本延迟

就有n个负载电容)。 值得注意的是,在这种由并联延迟单元组成的延迟链中,单个元件的DNL是由相应延迟单元的绝对延迟失配产生的,而不是延迟单元之间的延迟差,因为基本延迟![]() 在每个延迟单元中都有一些随机变化。这要求在布局设计的时候应当格外小心以最小化DNL。 还需要注意的是,INL在此并不积累,与延迟单元的DNL完全相同(啥意思?沿延迟链传播难道不会积累INL?)。

在每个延迟单元中都有一些随机变化。这要求在布局设计的时候应当格外小心以最小化DNL。 还需要注意的是,INL在此并不积累,与延迟单元的DNL完全相同(啥意思?沿延迟链传播难道不会积累INL?)。

4、LSB时长 用左图中的DLL锁定为![]() 。DLL匹配两个缩放元件之间的延迟差

。DLL匹配两个缩放元件之间的延迟差![]() ,缩放差为32个单位电容负载,因此是单个单位电容负载的延迟对应于

,缩放差为32个单位电容负载,因此是单个单位电容负载的延迟对应于![]() 。

。

下图显示了上图中所示类型的不同负载电容缩放延迟单元之间的延迟。基本延迟 为300ps,相邻单元之间的延迟 调整为10ps。

(六)MEASUREMENTS(一系列对比实验结果)

一、硬件平台

1、采用0.35um的数字CMOS工艺。布局面积2.5mm*3.0mm(包含焊盘),版图如下图所示。

2、在+60℃下粗延时链最大正常工作内部频率为160MHz,使用5MHz外部参考时钟(Tektronix AWG2021),通过粗精度DLL中循环32次时钟边缘进行测量。由于循环延迟链中累积抖动增加效应,再循环因子N的任何进一步增加都开始降低单次激发精度。

二、性能评估

1、插值LSB分辨率为12.2ps。15位计数器能测量时间范围为0到204s。3.3V工作电压的能耗为40mW,主要在粗插值器中消耗。TDC每秒能进行超过500000次的测量。

2、对比有无INL查找表校验的精度:

在粗插值器周期的时间范围内产生1000000次随机脉冲并统计落在各个延迟单元的脉冲的次数制成INL查找表。对比在使用INL查找表和不使用INL查找表下单次测量精度的均方误差。通过计算在插值范围内几个时间间隔10000次异步定时信号测量结果的平均和标准差得到如下折线图:

未经过INL校正的单次测量精度在室温下的均方误差未13.0ps;经过INL校正的单次测量精度在室温下均方误差为8.1ps。

从上图中可以看出,当时间间隔为粗延迟链长度的整数倍时,TDC精度最高,这是因为START、STOP通道之间的INL差在这些点处最低(啥意思?)。上图中精度曲线以更长的时间间隔重复自身,因为插值器INL通常时基于延迟线的时间内插中可实现精度的主导因素,在不同插值周期中重复。 3、精度的主要影响因素:

13.0ps的单次测量精度的sigma值由几个因素共同作用,插值STRAT信号脉冲位置的插值器的INL如下图所示。在STRAT信号插值器中被测芯片的INL标准差为7.9ps。当LSB为12.2ps时,量化噪声的均方根为5.0ps,因此INL是影响精度的主要因素。

4、线性度:

用延迟发生器产生不同时间间隔来估计TDC的线性度。对10000次测量结果进行平均以减少延迟发生器中的色散(应该指的是延迟发生器产生时间间隔的非理想性吧),并使用一个已知其非线性的TDC测量相同的时间间隔。对这些平均结果的比较表明,当时间间隔>12ns时,测量线性度<5ps;当时间间隔在3~5ns时,线性误差<30ps,这可能时由于START和STOP信道之间的串扰。

5、温度稳定性:

在-40℃到+60℃的温度范围内测量TDC芯片的温度稳定性。细插值器START和STOP信道中的延迟偏移<0.28ps/℃。STRAT和STOP信道之间的延迟差导致START和STOP插值结果中与温度相关的偏移,温度漂移取决于该信号通路的延迟误差,不同芯片的温度票哟不同。 下面的表格罗列了本项目TDC与其他一些高分辨率的TDC的性能。(这里的插值比Interpol ratio只是外部参考振荡器周期与TDC的LSB的比值)。

即使0.35um工艺在对比的其他TDC中比较好,但是本项目在适用性(参考时钟频率)、低功耗和高精度方面做的真的很棒。

(七)CONCLUSION(得出结论)

1、本项目成果:

在0.35um的CMOS工艺下实现了高精度TDC的设计。使用低5MHz外部参考时钟作为时基,分辨率和测量范围分别为8.1ps(使用INL查找表校验)和204s,而且仅使用了20个延迟单元就实现了16384的插值率。

2、本项目使用的获得低非线性的高插值比的技术:

(1)参考循环回收技术:

有效降低了粗插值器延迟链的长度,使第一级插值使用只有八个延迟单元的短延迟链。

(2)多级插值技术:

减少了延迟单元和寄存器数量,从而减小了TDC面积大小和非线性、还降低了TDC功耗。

3、本项目使用的提高测量精度的技术:

(1)并行缩放延迟技术:

细插值器使用了并行缩放延迟链将单个延迟单元延迟时间降到了亚门级别,提高了分辨率。

(2)INL查找表技术:

INL查找表减少了延迟链中延迟单元的DNL沿线传播积累的INL对测量精度的影响,从而获得了8.1ps的单次测量精度。

4442

4442

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?