本原创文章由深圳市小眼睛科技有限公司创作,版权归本公司所有,如需转载,需授权并注明出处(www.meyesemi.com)

一、开发系统介绍

开发系统概述

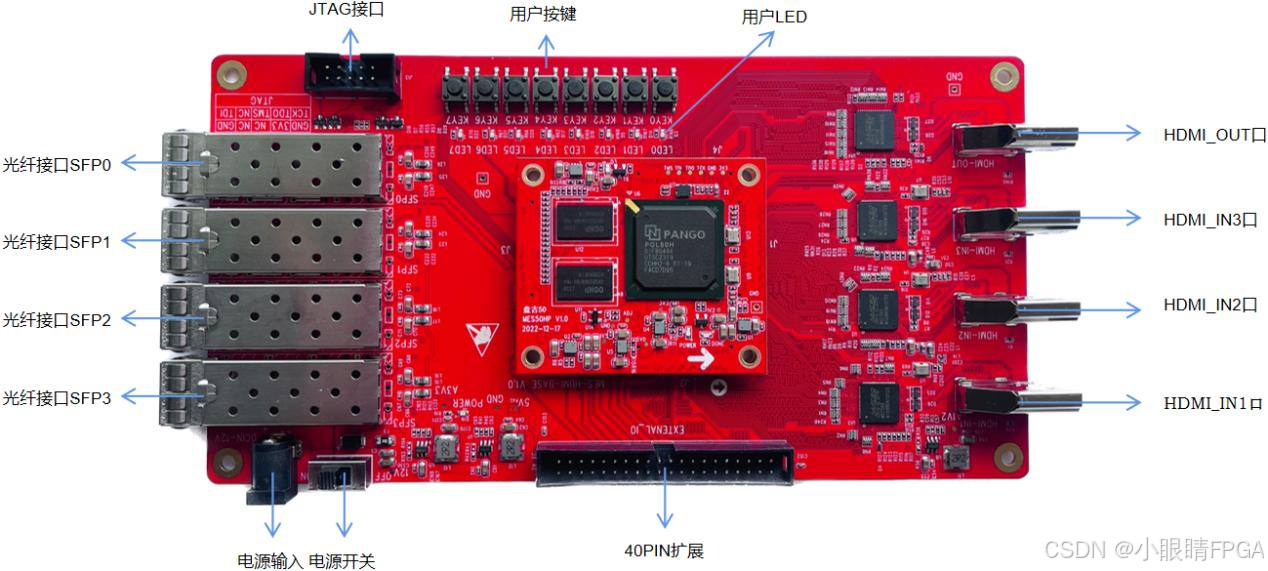

盘古 50KH 开发板(MES50H-HDMI)采用了核心板+扩展板的结构,核心板 与扩展板之间使用高速板对板连接器进行连接。

核心板主要由 FPGA+2 颗 DDR3+Flash+电源及复位构成,承担了 FPGA 的最 小系统运行及高速数据处理和存储的功能。FPGA 选用的是紫光同创 40nm 工艺 的 FPGA(logos 系列:PGL50H-6IFBG484);PGL50H 和 DDR3 之间的数据交互时 钟频率最高到 400MHz,2 颗 DDR3 的数据位宽为 32bit,总数据带宽最高到 25600 (800×32)Mbps,充分满足了高速多路数据存储的需求;另外 PGL50HFPGA 带 有 4 路 HSST 高速收发器,每路速度高达 6.375Gb/s,非常适合用于光纤通信和 PCIe 数据通信;电源采用多颗 EZ8303(艾诺)来产生不同的电源电压。

底板为核心板扩展了丰富的外围接口, 预留 HDMI 收发接口用于图像验证及 处理;预留的光纤接口;预留了一个 40pin 的 IO 扩展连接器,方便用户在开发 平台基础上验证模块电路功能。

开发系统简介

开发系统外设资源

◆ HDMI 输入接口*3

◆ HDMI 输出接口*1

◆ 光纤接口*4

◆ JTAG 调试接口*1

◆ 40PIN 扩展口*1

◆ 按键 *8

◆ LED *8

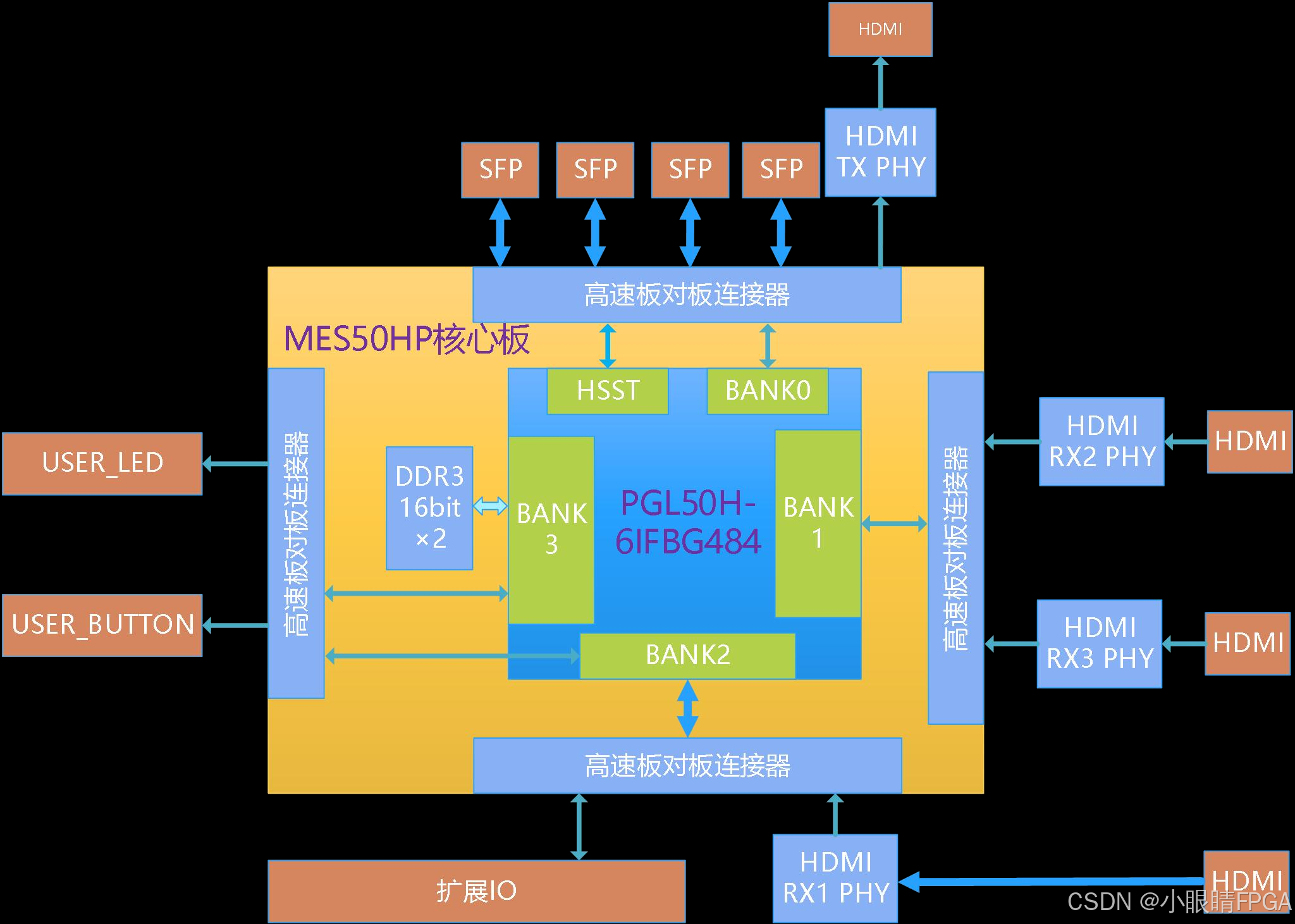

开发系统功能框图

开发系统功能框图

综上描述,盘古-50 开发平台可实现的功能细节如下:

◎ LogosFPGA 核心板

由 PGL50H+2 片 512MB DDR3+128MB QSPI FLASH 组成,另外板上有一个 高精度的 50MHz 和 125MHz 晶振,为 FPGA 系统和高速串行收发器 HSST 模块 提供稳定的时钟输入。

◎ SFP 高速光纤接口 * 4

Logos FPGA 的 HSST 收发器的高速收发器连接到 4 个光模块的发送和接 收,实现 4 路高速的光纤通信接口。每路的光纤数据通信接收和发送的速度高 达 6.375Gb/s。

◎ HDMI 输出 * 1

选用了国产宏晶微公司的 MS7210 HDMI 发送芯片,兼容 HDMI1.4b 及 HDMI 1.4b 下标准视频的 3D 传输格式。支持的最高分辨率高达 4K@30Hz,最高采样 率达到 300MHz;支持 HBR 音频。

◎ HDMI 输入 * 3

选用了国产宏晶微公司的 MS7200 HMDI 接收芯片,兼容 HDMI1.4b 及 HDMI 1.4b 下标准视频的 3D 传输格式。支持的最高分辨率高达4K@30Hz,最高;采 样率达到 300MHz;支持 HBR 音频。

◎ JTAG 接口

10 针 2.54mm 间距的双排排针口,用于 FPGA 程序的下载和调试。

◎ 40 针扩展口

预留 1 个 40 针 2.54mm 间距的扩展口,可以外接的各种模块。扩展口包含 5V 电源 1 路,3.3V 电源 2 路,地 3 路,I/O 口 34 路。

◎ LED 灯

8 个用户发光二极管;

◎ 按键

8 个用户按键;

二、核心板

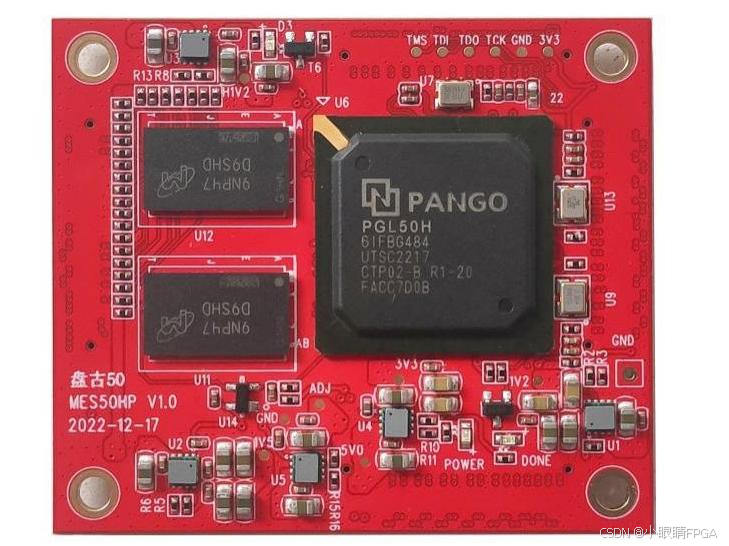

核心板简介

MES50HP 核心板是基于紫光同创 logos 系列 FPGA(PGL50H-6IFBG484) 开发的高性能核心板,具有高数据带宽、高存储容量的特点,适用于高速数据通 信、处理、采集等方面的应用。

这款核心板使用了 2 片启芯公司的 QN3B256M16H-16A::P 这款 DDR3 芯片, 每片 DDR 的容量为 4Gbit;2 片 DDR 芯片组合成 32bit 的数据总线宽度,FPGA 和 DDR3 之间的读写数据带宽高达 25Gb;这样的配置可以满足高带宽的数据处 理需求。

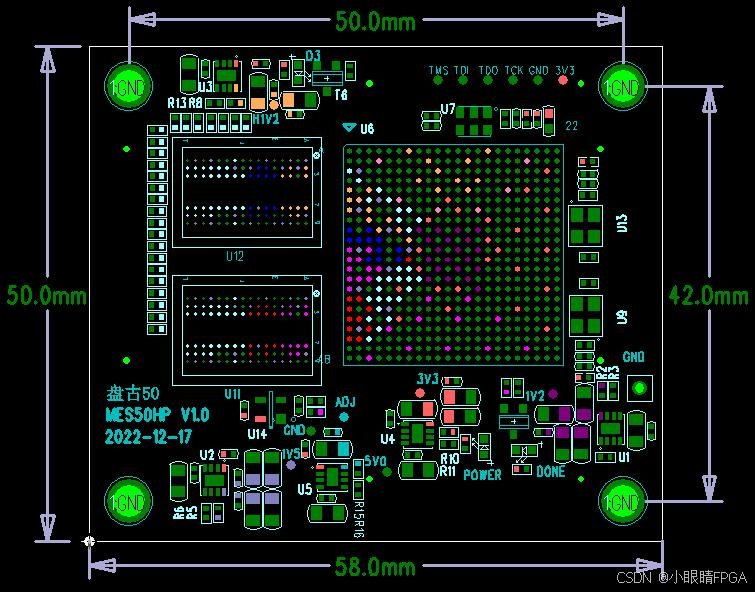

这款核心板扩展出 195 个默认电平标准为 3.3V 普通 IO 口,其中有 113 个 IO 电压标准可调,12 个 1.5V 电平标准的普通 IO 口,还有 4 对 HSST 高速 RX/TX 差分信号和 1 对 HSST 高速接口的参考输入时钟。对于需要大量 IO 的用户,此 核心板将是不错的选择。而且,FPGA 芯片到接口之间走线做了等长和差分处理。 核心板尺寸仅为 50*58(mm),对于二次开发来说非常适合。

核心板资源

FPGA

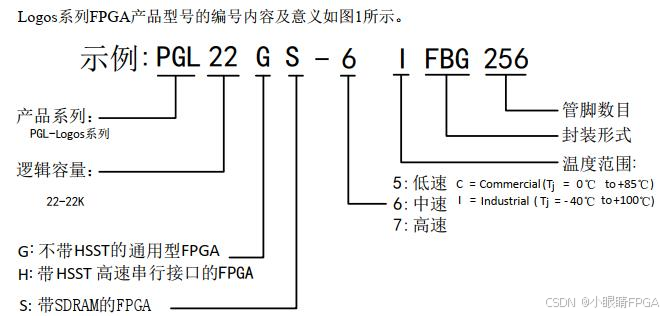

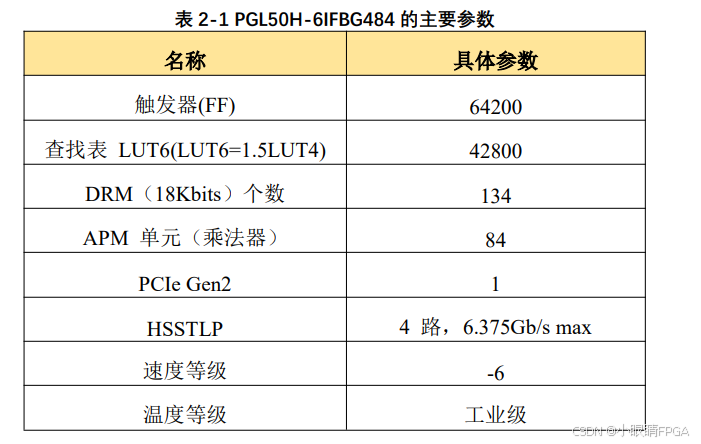

MES50HP 核心板使用的 FPGA 型号为 PGL50H-6IFBG484,属于紫光同创公司 Logos 系列的产品,速度等级为 6,温度等级为工业级。此型号为 FBG484 封装,484 个引脚。紫光同创 LogosFPGA 的芯片命名规则如下:

logos 系列 FPGA 命名规则

其中 FPGA 芯片 PGL50H 的主要参数如下所示:

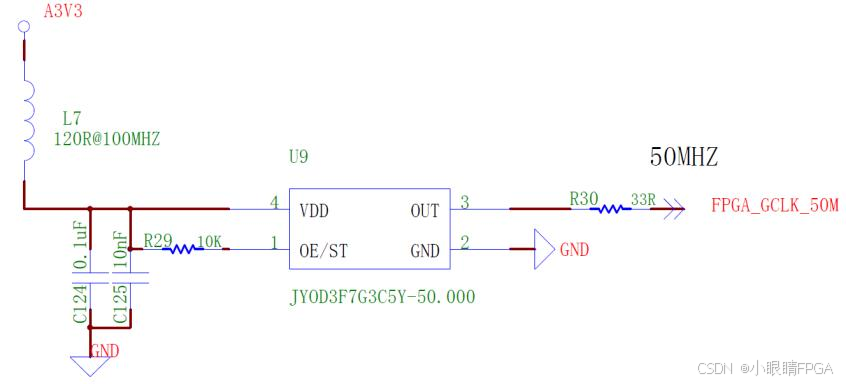

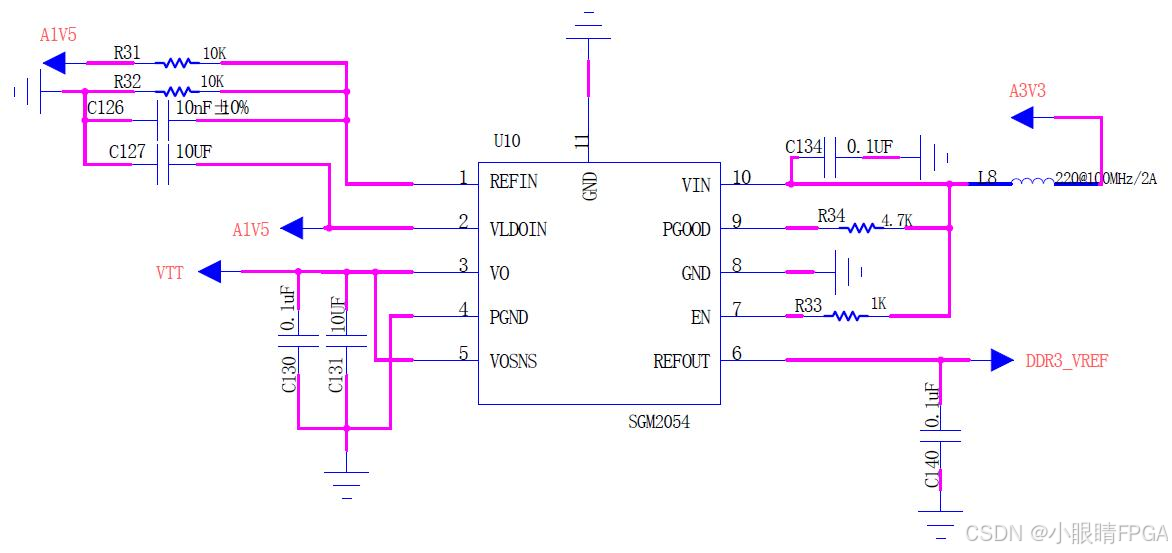

时钟

MES50HP 核心板上配有 1 个 125MHz 有源差分晶振、1 个单端 50MHz 晶振和 1 个单端 27MHz 晶振。差分晶振用于 HSST 收发器的参考时钟输入;单端 50MHz 用于 FPGA 的系统时钟源。

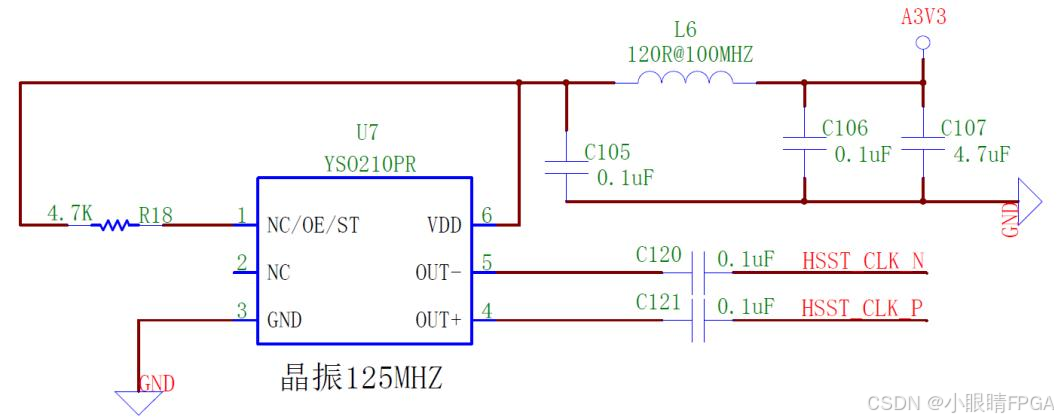

125MHz 差分晶振

下图中的 U7 为 125M 有源差分晶振电路,此时钟是给 FPGA 内部的 HSST 模块 提供的参考输入时钟。晶振输出连接到 FPGA HSST BANK 的时钟管脚上。

有源差分晶振原理图

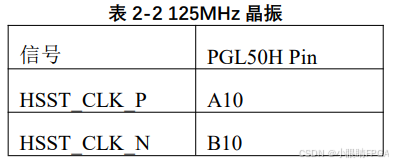

单端晶振

下图中的 U9 即为 50M 有源晶振电路,此时钟接到给 FPGA 内部的全局时钟管 脚上,可为 FPGA 提供的参考输入时钟。

有源单端晶振 50M 原理图

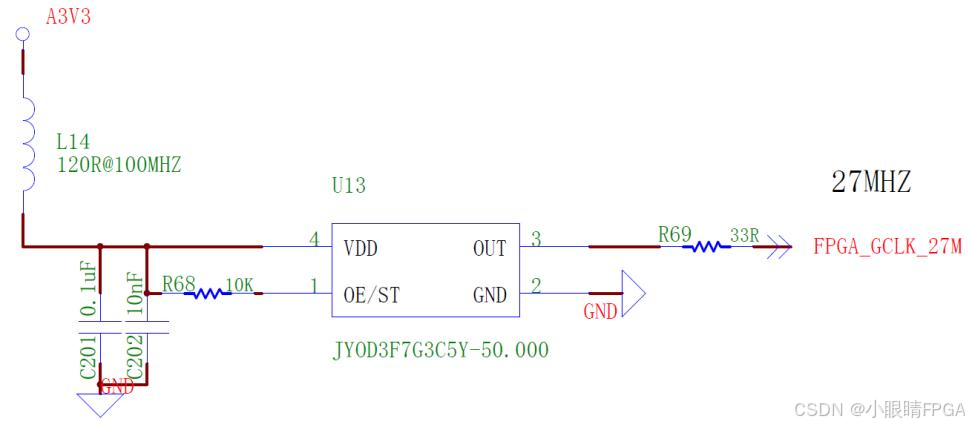

下图中的 U13 即为 27M 有源晶振电路,此时钟接到给 FPGA 内部的全局时钟管 脚上,可为 FPGA 提供的参考输入时钟。

有源单端晶振 27M 原理图

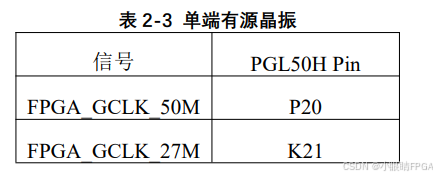

具体管脚分配请看下表:

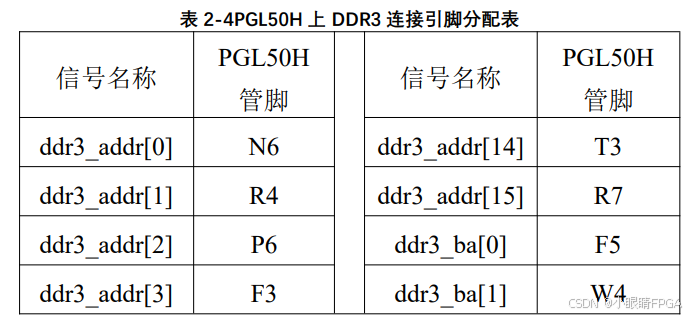

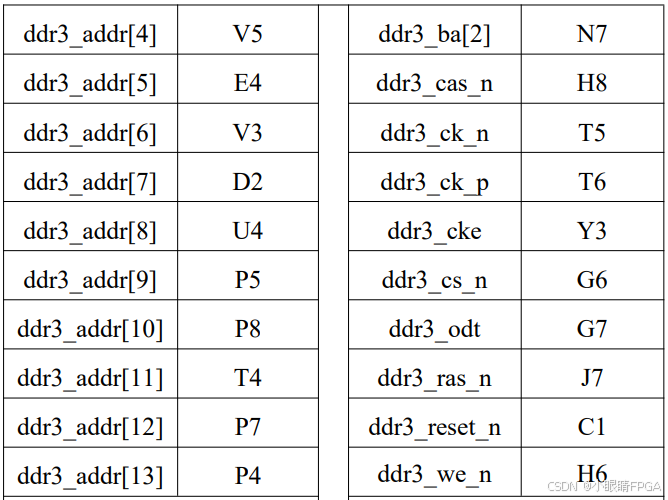

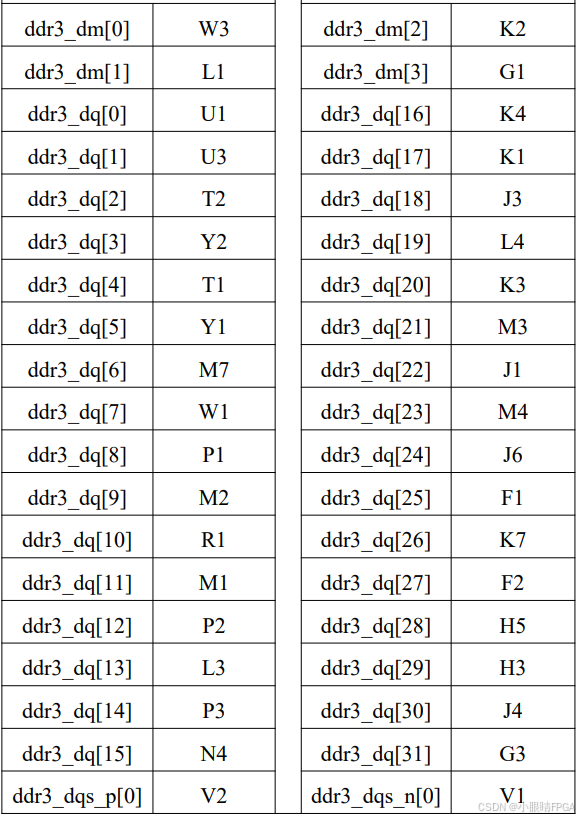

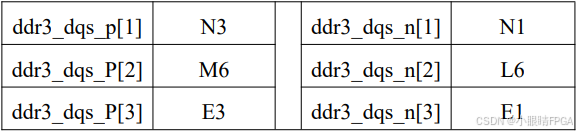

DDR3

MES50H核心板上配有2个启芯公司的4Gbi(t 512MB)的DDR3芯片(共计8Gbit), 型号为 QN3B256M16H-16A:P(兼容 Micron MT41K256M16HA-125)。DDR 的总线 宽度共为 32bit。DDR3 SDRAM 的最高运行时钟速度可达 400MHz(数据速率 800Mbps)。该 DDR3 存储系统直接连接到了 FPGA 的 BANK B3, DDR3 DRAM 的硬 件连接示意图如图 2.2 所示:

PGL50H 与 DDR 连接框图

PGL50H 内可运行 DDR 控制器最大支持位宽可达 32bit,速度高达 400MHz (800Mbps)。DDR3 使用 1.5V SSTL 接口标准,在 MES50H-HDMI 开发板上 PGL50H 与 DDR3 紧密的排列在一起,保持连接和匹配。

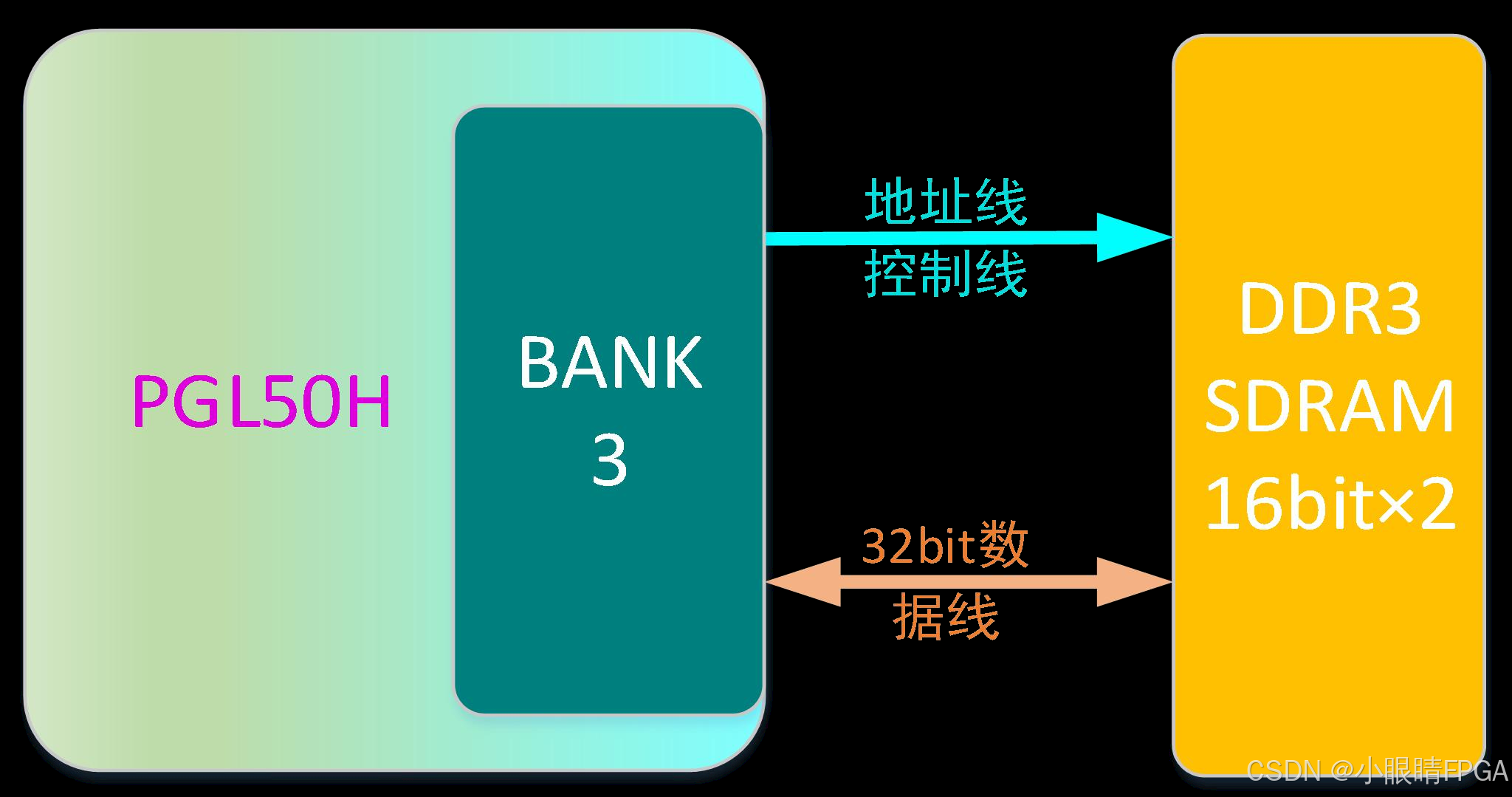

DDR3 布线采用 50 欧姆走线阻抗用于单端信号,DCI 电阻(VRP / VRN)以 及差分时钟设置为 100 欧姆。每个 DDR3 芯片在 ZQ 上都需要 240 欧姆电阻下拉。 DDR-VDDQ 设置为 1.5V,以支持所选的 DDR3 器件。DDR-VTT 是与 DDR-VDDQ 始终电压跟随,保持为 1 2 倍 DDR-VDDQ 的电压值。DDR-VREF 是一个独立的缓 冲输出,等于 1 2 倍 DDR-VDDQ 的电压。DDR-VREF 是隔离的,可为 DDR 电平转 换提供更清晰的参考。

DDR3 参考电压及上拉跟随电压原理图

该 DDR3 存储系统直接连接到了 PGL50H 的 Bank 3 上;DDR3 的硬件设计需 要严格考虑信号完整性,我们在电路设计和 PCB 设计的时候已经充分考虑了匹 配电阻/终端电阻,走线阻抗控制,走线等长控制,保证 DDR3 的高速稳定的工作。

DDR3 的具体管脚分配如下:

FLASH

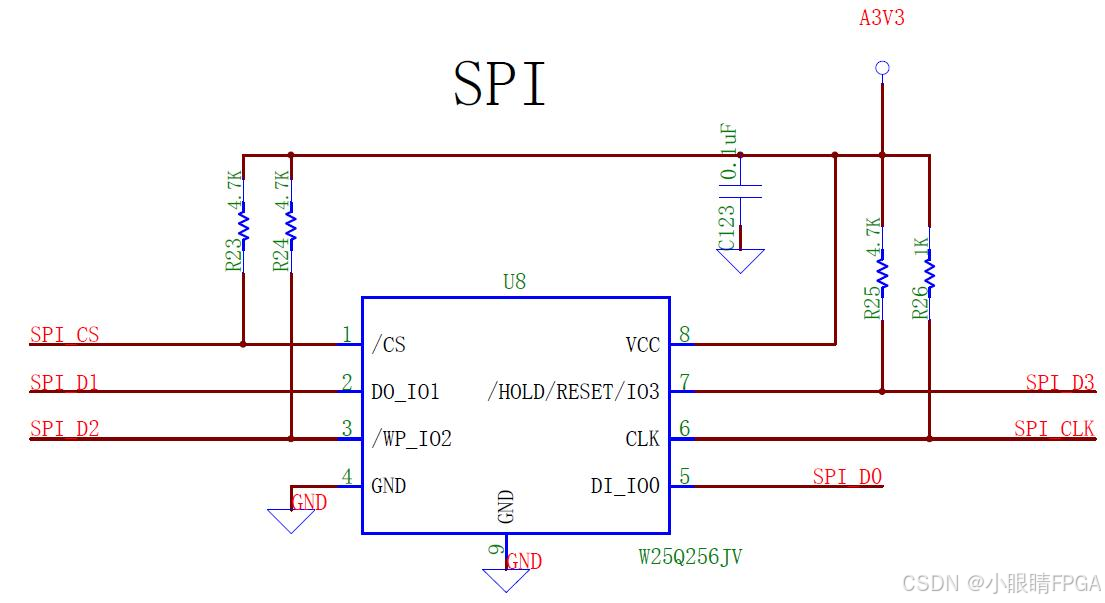

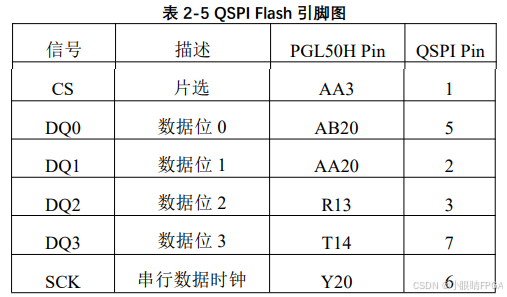

MES50H-HDMI 开发板具有 4 位 SPI(QSPI)串行 Nor 闪存,使用的是兆易 创新的 GD25Q128E/华邦 W25Q256JV。连接在 PGL50H 的特定引脚上,采用 3.3V 电平标准。

QSPI 的电路连接如下:

Flash 电路图

管脚分配如下

扩展接口

核心板的背面一共扩展出 4 个高速扩展口,使用 4 个 80Pin 的板间连接器和底 板连接。FPGA 的 IO 口通过差分走线方式连接到这 4 个扩展口上。连接器的 PIN 脚 间距为 0.5mm,和底板的母座连接器配置实现高速数据通信。

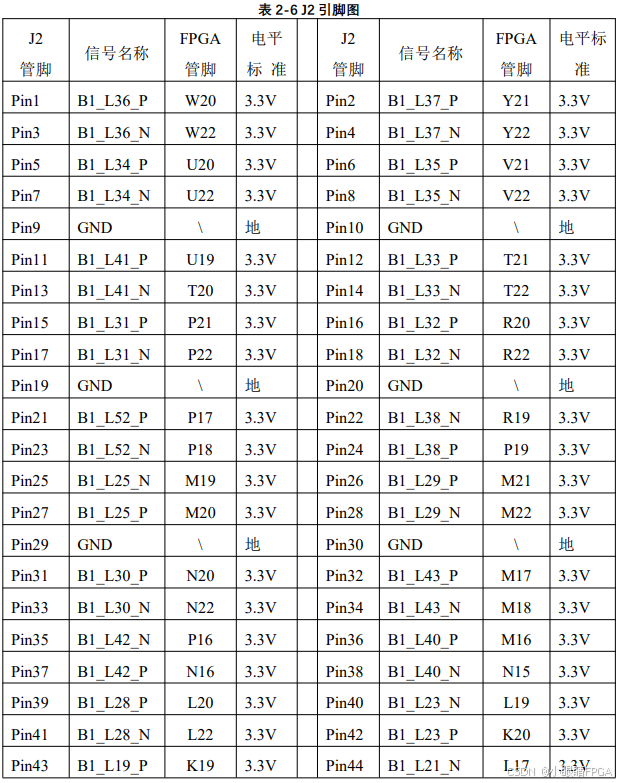

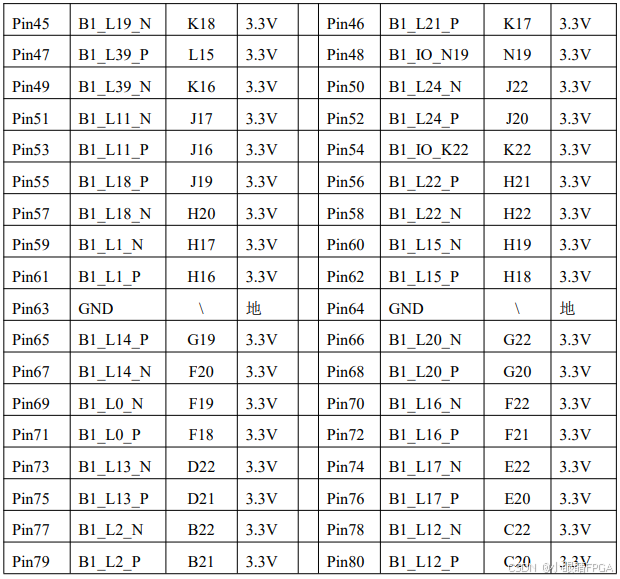

扩展接口 1:J2

80Pin 的连接器 J2 用来扩展 FPGA 的 BANK B1 的普通 IO,B1 的电压标准是 3.3V 的,J2 扩展口的管脚分配如下表所示:

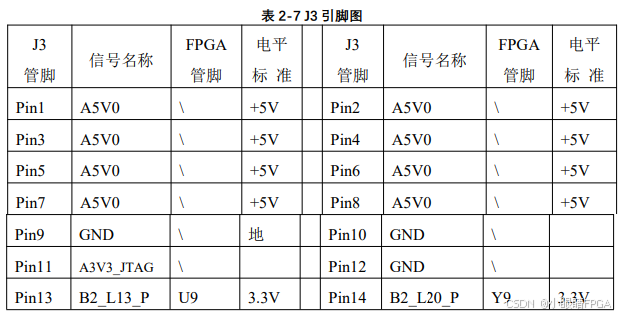

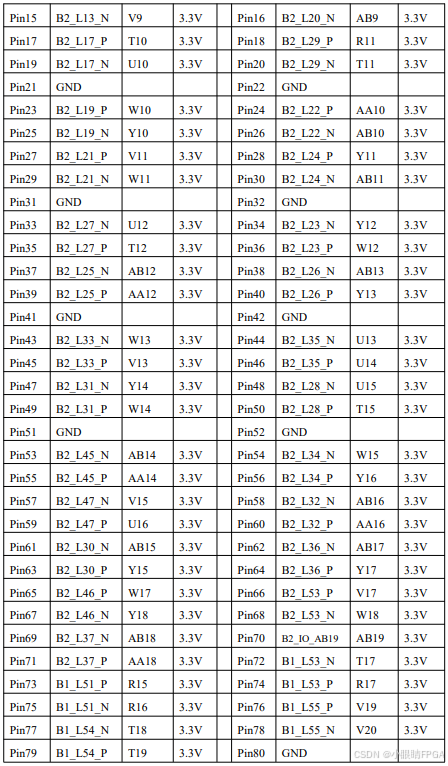

扩展接口 2:J3

80Pin 的连接器 J3 用来连接底板的 VCCIN 电源(+5V),地和 FPGA 的 BANK2 及 BANK1 的普通 IO,B2 的 IO 口的电压标准是 3.3V 的,如果用户想输出其它标准的 电平,可以通过修改电源进行, J3 扩展口的管脚分配如下表所示:

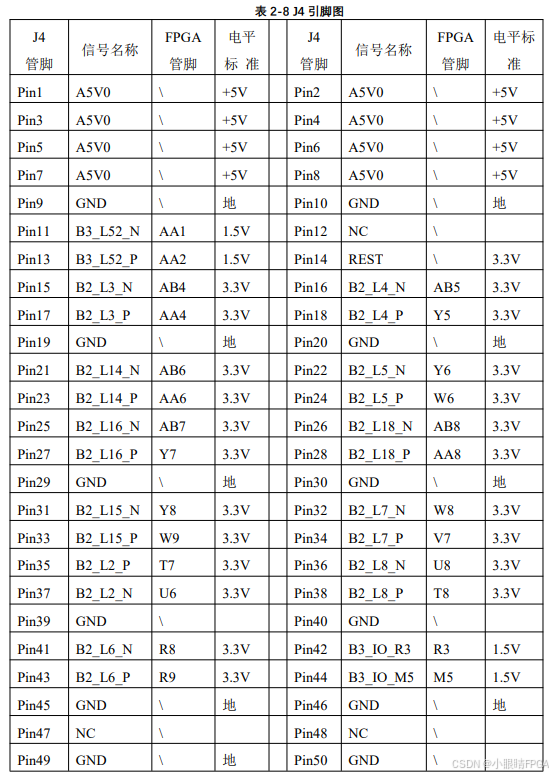

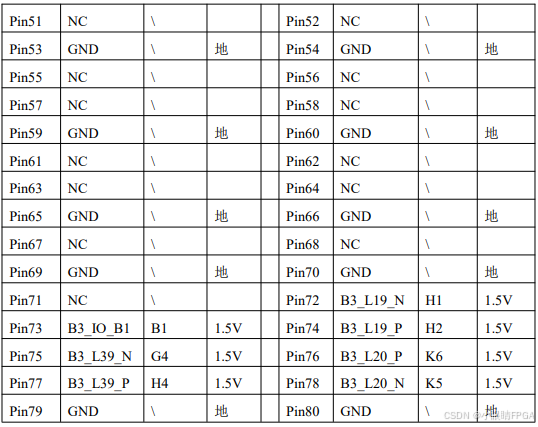

扩展接口 3:J4

80Pin 的连接器 J4 用来连接底板的 VCCIN 电源(+5V),地和 FPGA 的 BANK2 及 BANK3 的普通 IO,B2 的 IO 口的电压标准是 3.3V 的,如果用户想输出其它标准的 电平,可以通过修改电源进行, Bank3 由于挂载了 DDR3,所以 IO 口的电压标准固定 为 1.5V, J4 扩展口的管脚分配如下表所示:

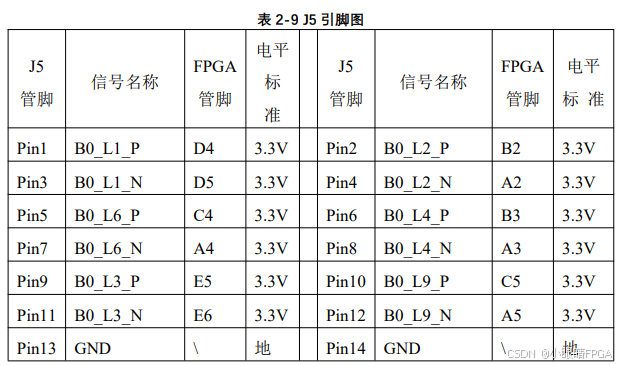

扩展接口 4:J5

80Pin 的连接器 J5 用来扩展 FPGA 的 BANK B0 的普通 IO 和 HSST 的高速数据和 时钟信号。B0 的 IO 口的电压标准可以通过修改电源电阻的阻值调整,默认是 3.3V, 如果用户想输出其它标准的电平,可以通过修改电源进行。HSST 的高速数据和时钟 信号在核心板上严格差分走线,数据线等长及保持一定的间隔,防止信号干扰。J5 扩展口的管脚分配如表 2-7-4 所示:

电源

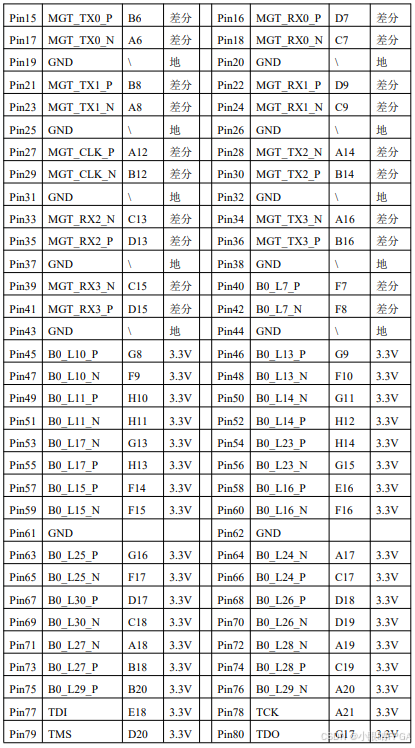

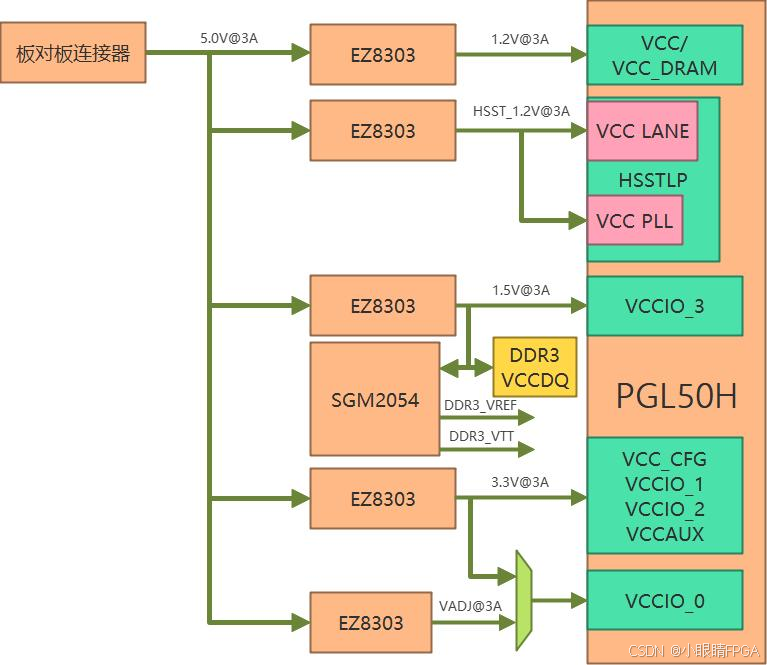

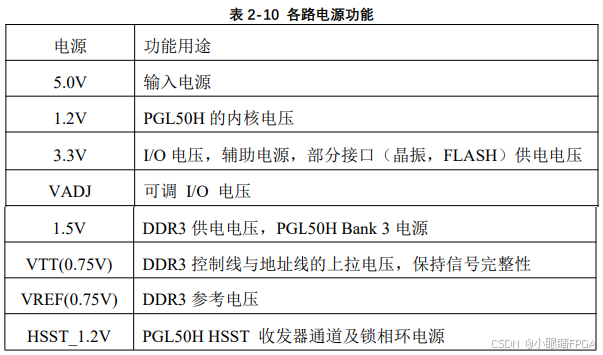

MES50HP 核心板供电电压为 VCCIN,输入电压为 5V,需通过板对板连接器供 电,连接底板时通过底板供电。板上的电源设计示意图如下图所示:

核心板电源树

核心板通过+5V 供电, 通过 4 路 DC/DC 艾诺电源芯片 EZ8303 转化成+3.3V, +1.5V,HSST_VCC12、+1.2V 4 路电源, 4 路输出电流可高达 3A。其中 VCCADJ 产生 VCCIO 的电压可调,VCCADJ 主要是对 FPGA 的 B0 进行供电,用户可以通过修 改电源电阻的阻值调整电压,使得 B0 的 IO 适应不同的电压标准。HSST_VCC12 是 高速收发器的 PLL 及通道电源。1.5V 通过圣邦微的 SGM2054 生成 DDR3 需要的 VTT 和 VREF 电压。各个电源分配的功能如下表所示:

尺寸结构图

核心板尺寸结构图

三、扩展底板

扩展底板简介

通过前面开发系统的介绍可知,扩展底板的外设资源如下:

◆ HDMI 输入接口*3

◆ HDMI 输出接口*1

◆ 光纤接口*4

◆ JTAG 调试接口*1

◆ 40 pin IO 扩展口*1

◆ 按键 *8

◆ LED *8

外接通信口

SFP 光纤接口

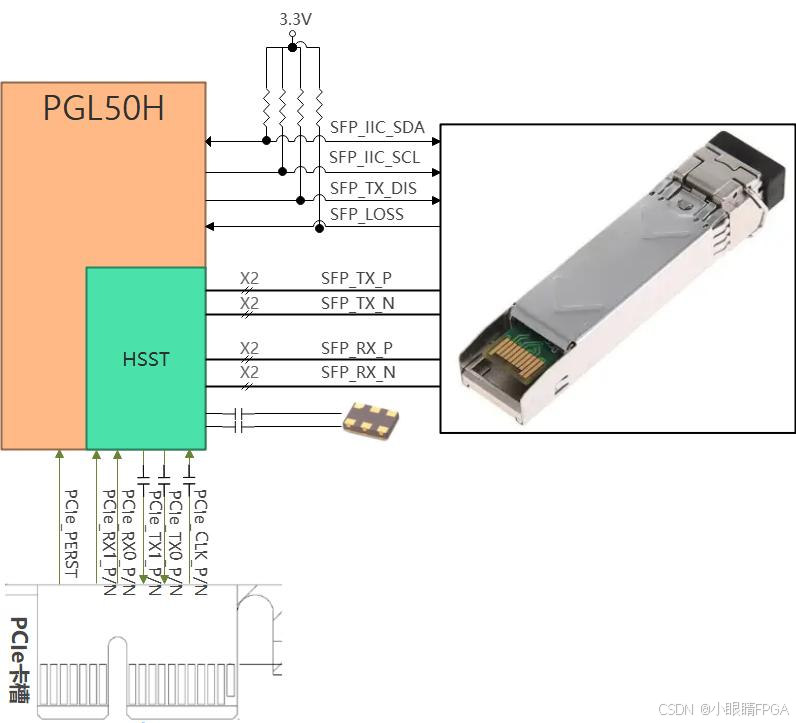

MES50H-HDMI 板上有 4 路光纤接口,用户可以购买光模块插入到这 4 个 光纤接口中进行光纤数据通信。4 路光纤接口分别跟 FPGA 的 HSST 收发器的 4 路 RX/TX 相连接, TX 信号和 RX 信号都是以差分信号方式通过隔直电容连 接 FPGA 和光模块,每路 TX 发送和 RX 接收数据速率高达 6.375Gb/s。HSST 收发器的参考时钟由板载的 125M 差分晶振提供。

FPGA 和光纤设计示意图如下图所示:

PGL50H HSST 功能连接图

下表显示了 PGL50H 与 4 个 SFP 接口的管脚连接。

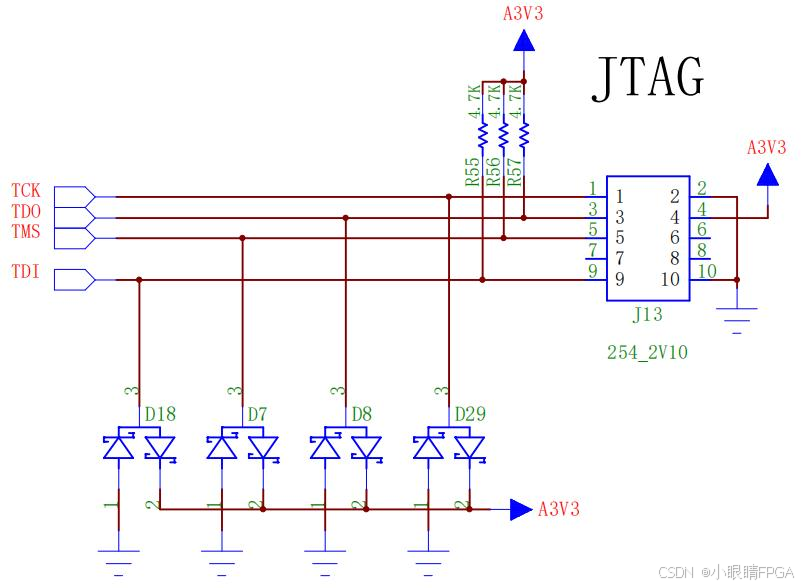

JTAG

MES50H-HDMI 开发板预留了一个 JTAG 接口,用于下载 FPGA 程序或者 固化程序到 FLASH。为了避免带电插拔造成对 FPGA 芯片的损坏,我们在 JTAG 信号上添加了保护二极管来保证信号的电压在 FPGA 接受的范围,避免 FPGA 的损坏。在使用过程中应尽量避免通电状态下插/拔 jtag 接口。

PGL50H JTAG 功能连接图

HDMI

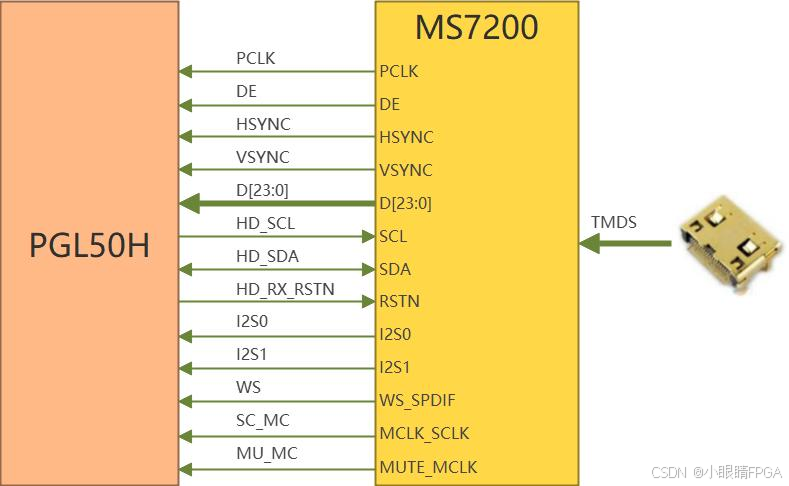

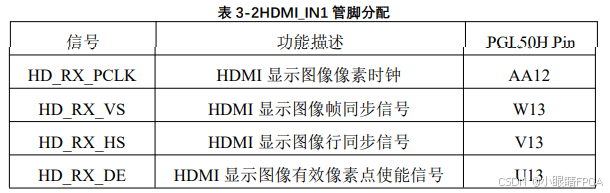

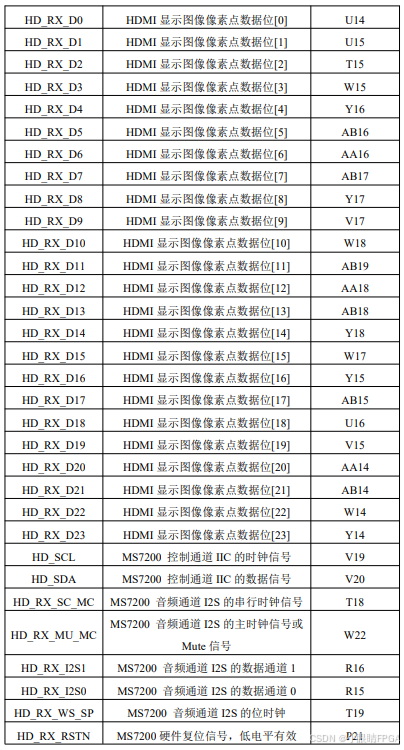

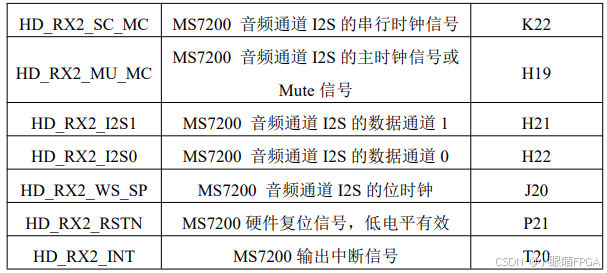

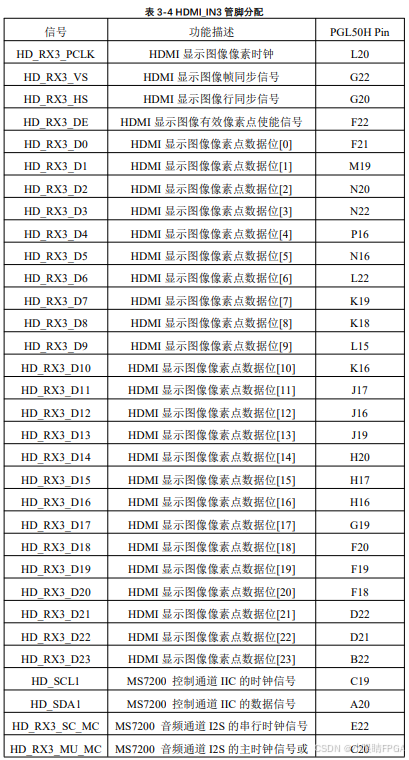

HDMI 输入接口

HDMI 输入接口的实现,选用了国产宏晶微公司的 MS7200 HDMI 接收芯片, 兼容 HDMI1.4b 及 HDMI 1.4b 下标准视频的 3D 传输格式。支持的最高分辨率高 达 4K@30Hz,最高采样率达到 300MHz;

MS7200 支持 YUV 和 RGB 之间的色彩 空间转换,数字接口支持 YUV 及 RGB 格式输出; MS7200 支持通过 IIS 总线或 SPDIF 传输高清音频,同时还支持高比特音频 (HBR)音频,在 HBR 模式下,音频采样率最高为 768KHz。

其中,MS7200 的 IIC 配置接口与 FPGA 的 IO 相连,通过 FPGA 的编程 来对 MS7200 进行初始化和控制操作,MES50H-HDMI 开发板上的 HDMI_IN1 口 的的 MS7200 的 SA 脚是上拉到电源电压,故 IIC 地址是 0XB2。HDMI_IN2 口的 MS7200 的 SA 脚是下拉到地,故 IIC 地址是 0X56。HDMI_IN3 口的 MS7200 的 SA 脚是下拉到地,故 IIC 地址是 0X56.

HDMI 输入接口的硬件连接如下图所示。

HDMI Receiver 连接示意图

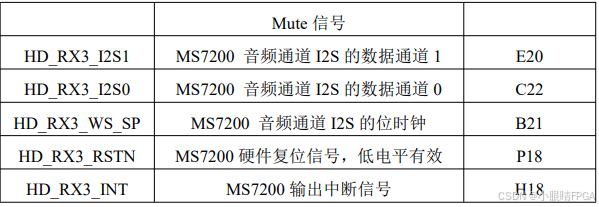

具体管脚分配请看下表:

MS7200 硬件复位信号,HDMI_IN1 和 HDMI_IN2 共用。

HDMI_IN1 和 HDMI_IN2 共用 IIC 总线。

HDMI_IN3 和 HDMI_OUT 共用 IIC 总线。

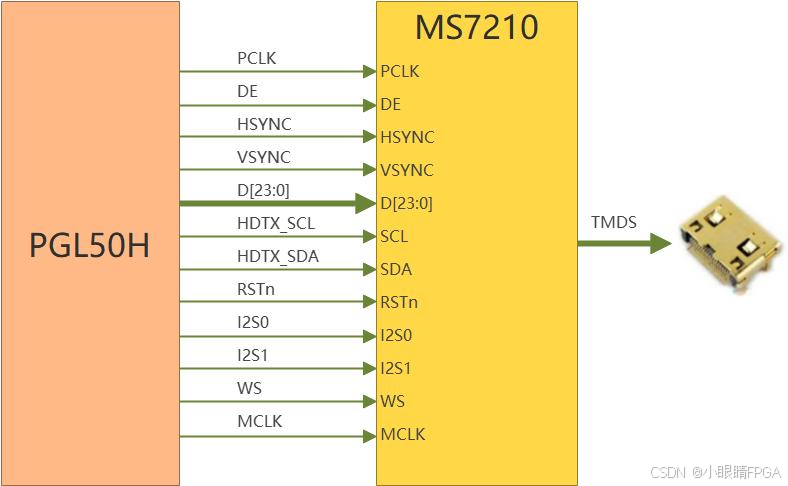

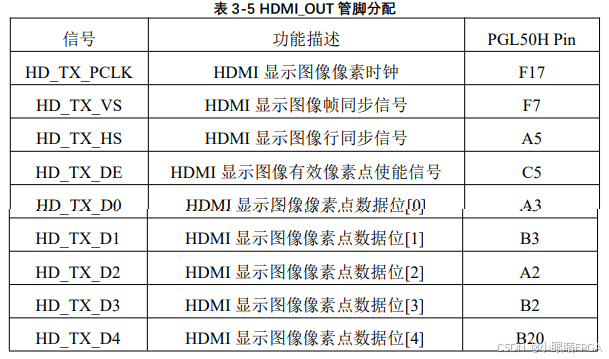

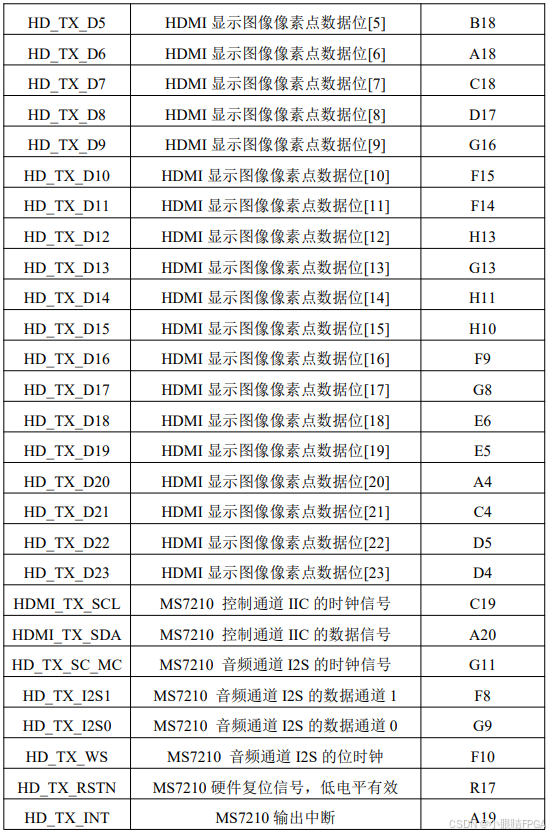

HDMI 输出接口

HDMI 输出接口的实现,选用了国产宏晶微公司的 MS7210 HDMI 发送芯片, 兼容 HDMI1.4b 及 HDMI 1.4b 下标准视频的 3D 传输格式。内置可编程 EDID 缓 存,支持的最高分辨率高达 4K@30Hz,最高采样率达到 300MHz;MS7210 支持 YUV 和 RGB 之间的色彩空间转换,数字接口支持 YUV 及 RGB 格式输入;

MS7210 的 IIS 接口支持高清音频的传输,同时还支持高比特音频(HBR)音 频,在 HBR 模式下,音频采样率最高为 768KHz。

其中,MS7210 的 IIC 配置接口与 FPGA 的 IO 相连,通过 FPGA 的编程 来对 MS7210 进行初始化和控制操作,MES50H-HDMI 开发板上将 MS7210 的 SA 管脚上拉到电源电压,故 IIC 的 ID 地址为 0xB2;

HDMI 输出接口的硬件连接如下图所示。

HDMI Transmit 连接示意图

具体管脚分配请看下表:

HDMI_IN3 和 HDMI_OUT 共用 IIC 总线。

按键/指示灯

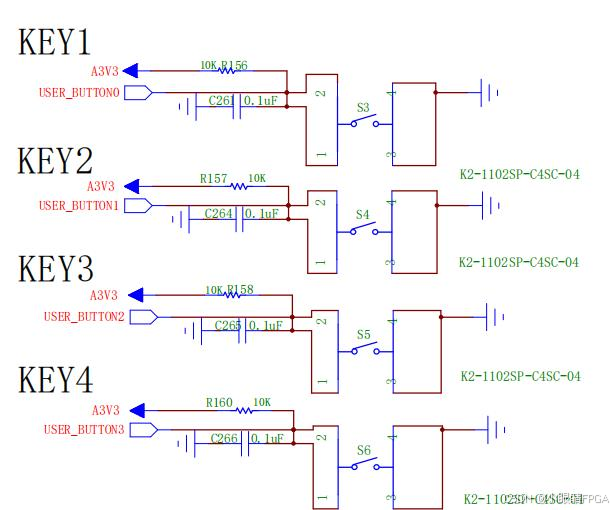

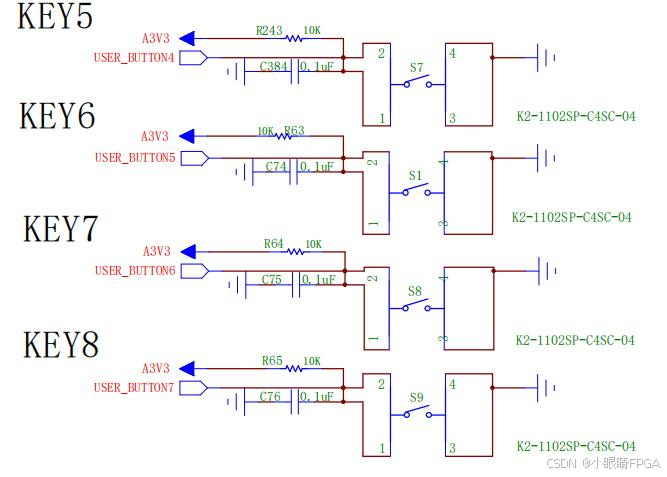

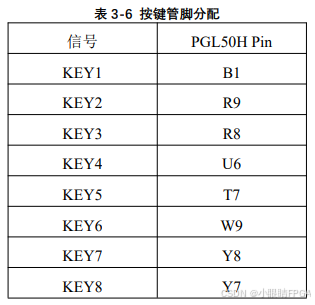

按键

MES50H-HDMI 扩展底板提供了 8 个用户按键(K1~8);1 个重加载按键, 重加载按键通过一个延时复位芯片连接到 PGL50H 的 RSTN 管脚;8 个用户按键 都连接到 PGL50H 的普通 IO 上,按键低电平有效,但按键按下时,IO 上的输入 电压为低;当没有按下按键时,IO 上的输入电压为高电平;

用户按键电路图

具体管脚分配如下;

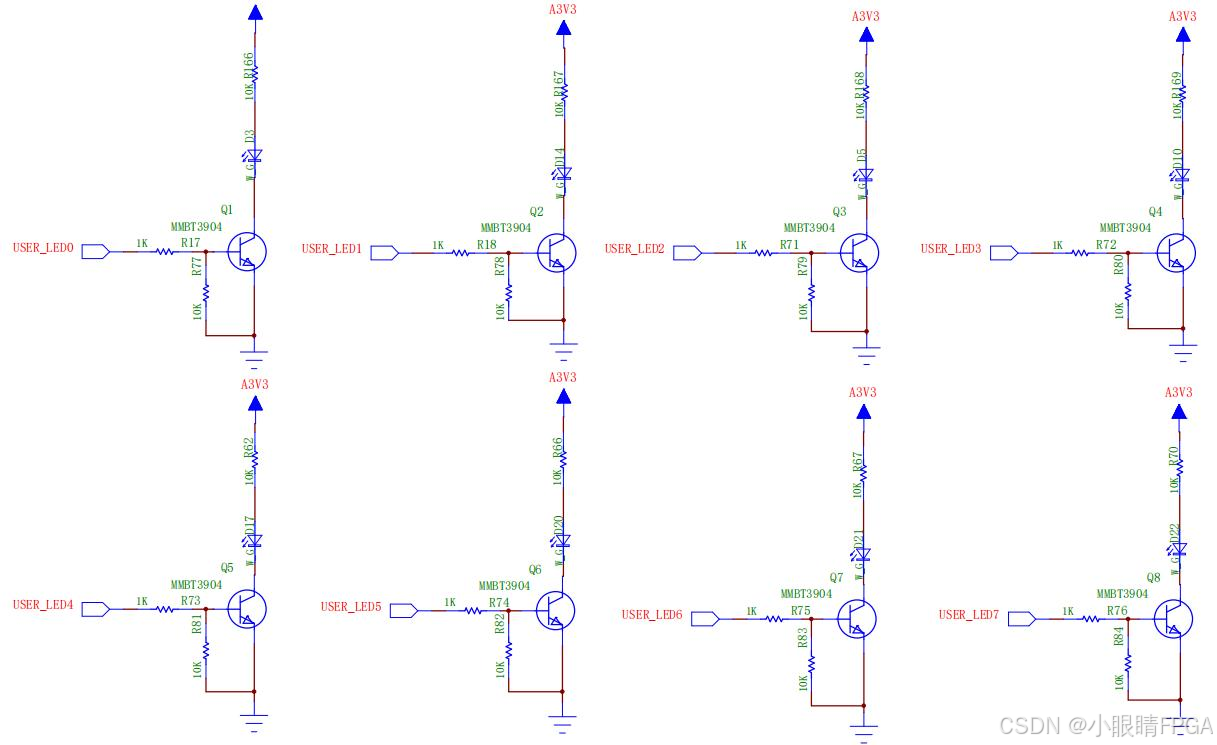

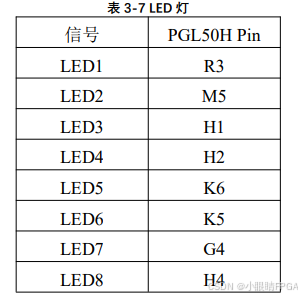

Led 灯

MES50H-HDMI开发板有11个翠绿LED灯,其中1个是电源指示灯(POWER);2 个是 FPGA 的运行的状态指示灯:INIT 和 DONE; 8 个是用户 LED 灯(LED1~ 8)。连接在 PGL50H BANK 0 的 IO 上,FPGA 输出高电平时对应的 LED 灯亮灯, 板上 LED 灯功能电路图:

LED 灯电路原理图

具体管脚分配请看下表:

扩展口

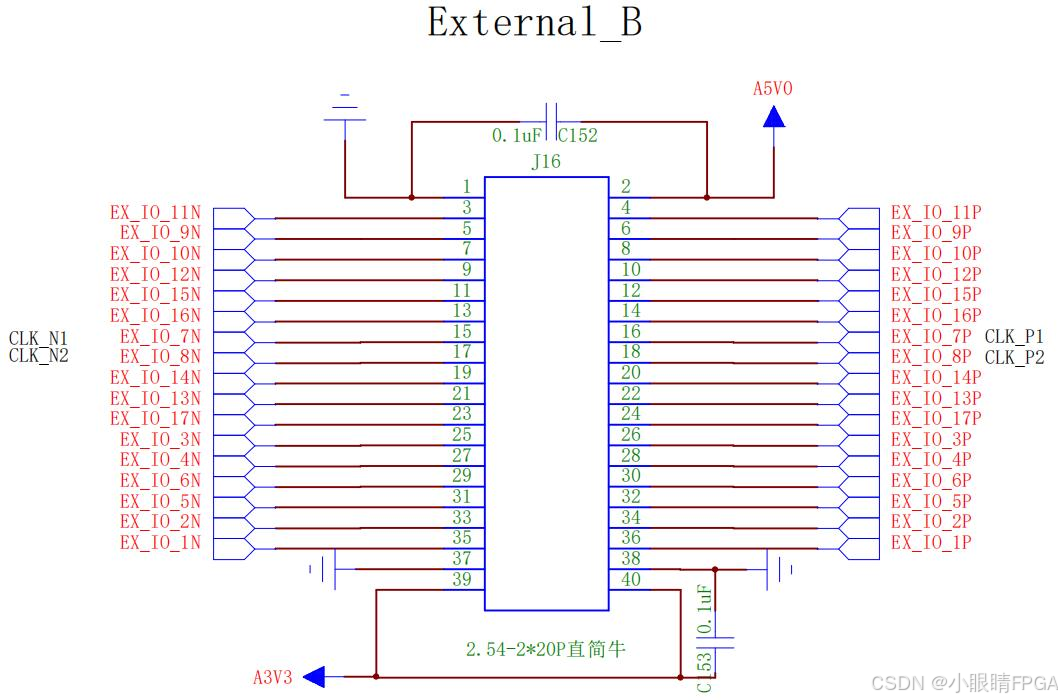

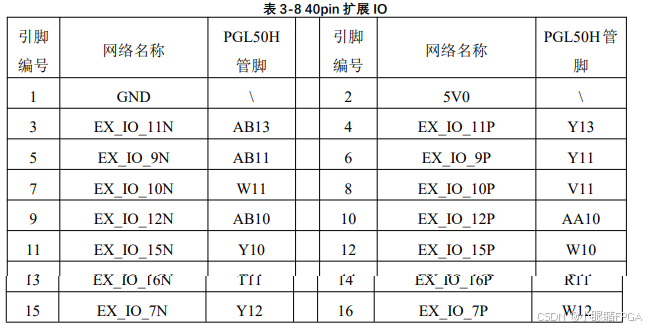

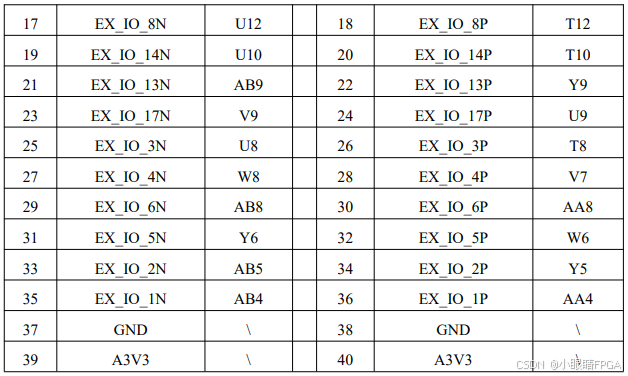

40pin 扩展口

扩展板预留 1 个 2.54mm 标准间距的 40 针的扩展口 J8,用于连接各个模块或 者用户自己设计的外面电路,扩展口有 40 个信号,其中,5V 电源 1 路,3.3V 电源 2 路,地 3 路,IO 口 34 路。切勿 IO 直接跟 5V 设备直接连接,以免烧坏 FPGA。 如果要接 5V 设备,需要接电平转换芯片。

40pin 扩展 IO 原理图

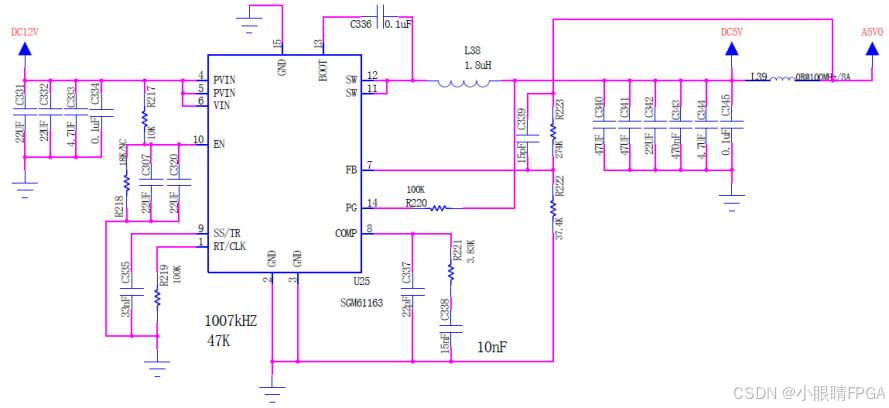

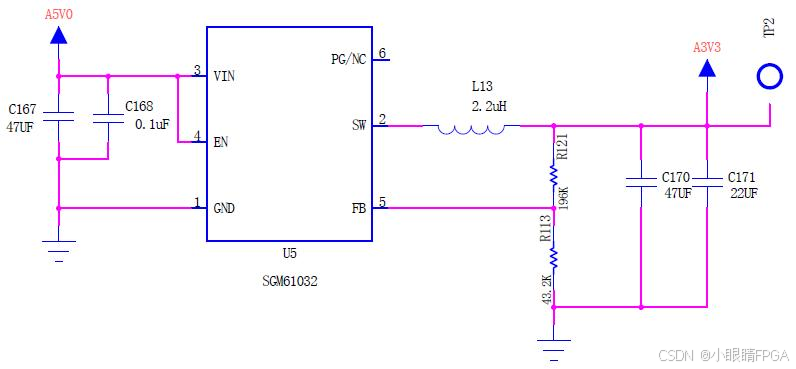

供电电源

开发板的电源输入电压为+12V,请使用开发板自带的电源,不要用其他规格的电 源,以免损坏开发板。扩展板上通过 1 路 DC/DC 电源芯片 SGM61163 把+12V 电压 转化成+5V 电源;另使用一路 DC/DC 电源芯片 SGM61032 把+5V 转换出+3.3V 供外 设接口使用;扩展板上的+5V 电源通过板间连接器给核心板供电,扩展板上电源设 计如下图所示:

12V 转 5V 原理图

5V 转 3.3V 原理图

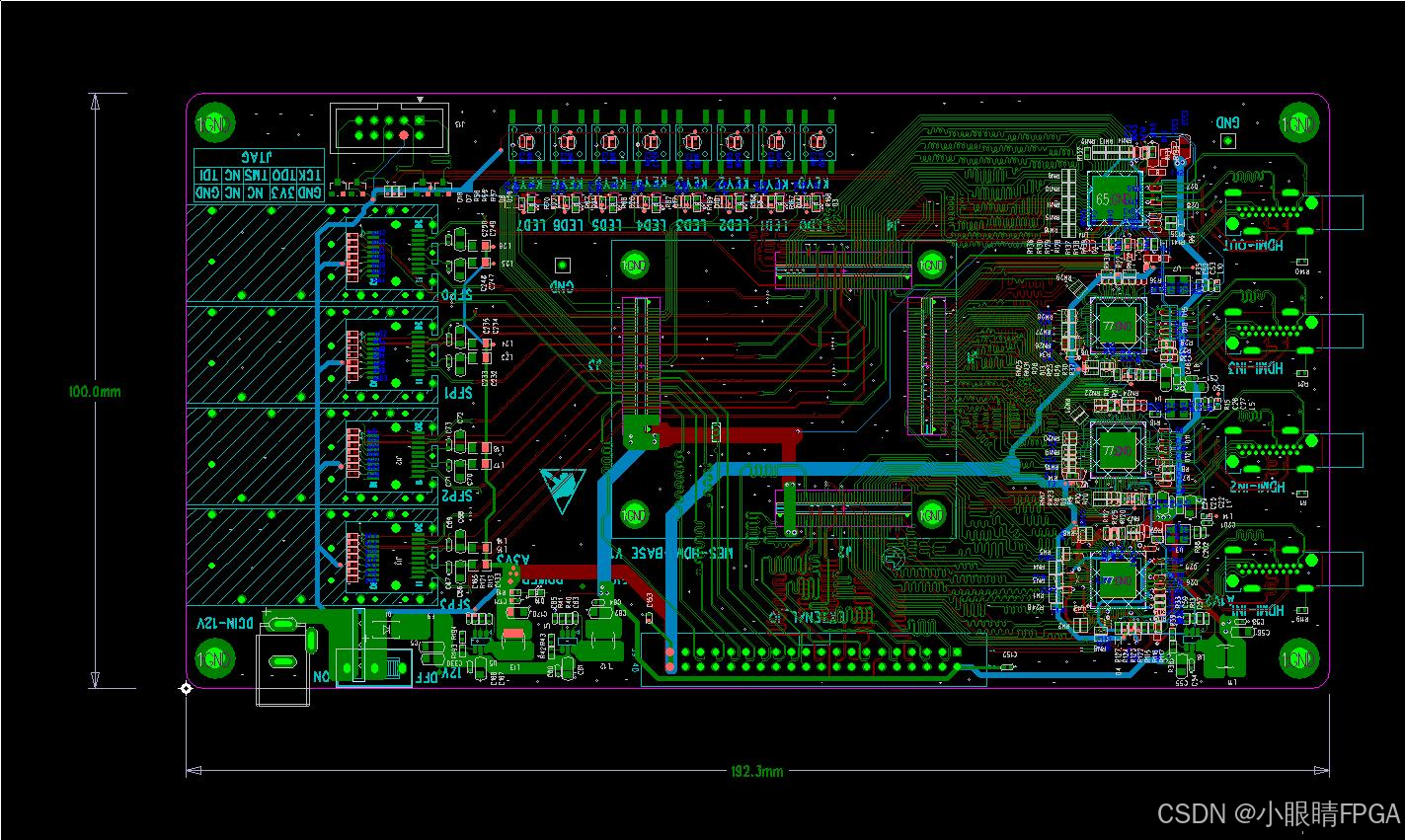

尺寸结构图

扩展底板尺寸结构图

1333

1333

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?