本原创教程由深圳市小眼睛科技有限公司创作,版权归本公司所有,如需转载,需授权并注明出处

适用于板卡型号:

紫光同创PGL50H开发平台(盘古50K)

一:盘古50K开发板(紫光同创PGL50H开发平台)简介

盘古50K开发板(紫光同创Logos系列PGL50H关键特性评估板)采用核心板+扩展板的结构,并使用高速板对板连接器进行连接。

核心板由 FPGA+2 颗 DDR3+Flash+电源及复位构成,承担 FPGA 的最小系统运行及高速数据处理和存储的功能。FPGA 选用紫光同创 40nm 工艺的 FPGA(logos 系列:PGL50H-6IFBG484)。PGL50H 和 DDR3 之间的数据交互时钟频率最高到 400MHz,2 颗 DDR3 的数据位宽为 32bit,总数据带宽最高 25600(800×32)Mbps,充分满足高速多路数据存储的需求。

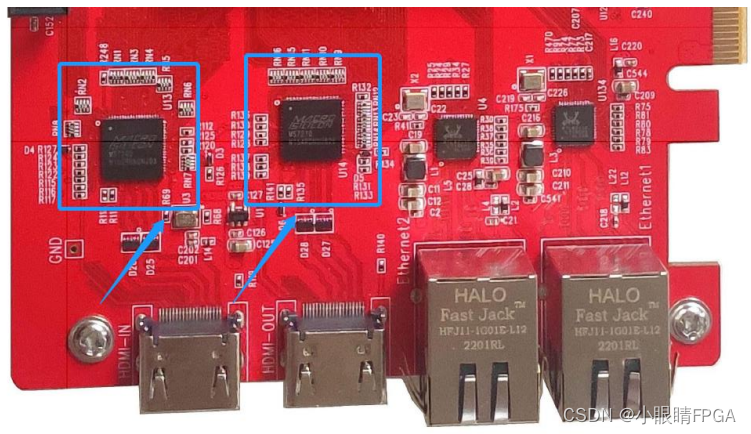

PGL50HFPGA带有4路HSST高速收发器,每路速度高达 6.375Gb/s,适合用于光纤通信和PCIe数据通信;电源采用多颗 EZ8303(艾诺)产生不同的电源电压。底板为核心板扩展丰富的外围接口, 预留 HDMI 收发接口用于图像验证及处理;预留的光纤接口、10/100/1000M 以太网接口,PCIE 接口,方便各类高速通信系统验证;预留一个 40pin 的 IO 扩展连接器,方便用户在开发平台基础上验证模块电路功能。

二、实验目的

实验 1:MES50HP 开发板通过 HDMI 在屏幕上显示彩条;

实验 2. MES50HP 开发板 HDMI IN 接收,通过 HDMI OUT 实现环路输出;

三、实验原理

1.显示原理

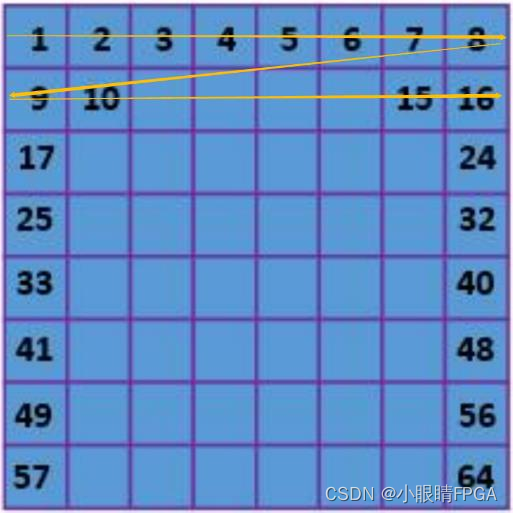

下图表示一个 8*8 像素的画面,图中每个格子表示一个像素点,显示图像时像素点快速点 亮的过程按表格中编号的顺序逐个点亮,从左到右,从上到下,按图中箭头方向的“Z”字形 顺序。

以上图为例,每行 8 个像素点,每完成一行信号的传输,会转到下一行信号传输,直到完 成第 8 行数据的传输,就完成了一个画面的数据传输了,一个画面也称为一场或一帧,显示每 秒中刷新的帧数称为帧率。比如 1920*1080P 像素,就是 1 行有效像素点 1920,一场有效行为 1080 行。

每个像素点的像素值数据,对应每个像素点的颜色。常见的像素值表示格式比如:RGB888, RGB 分别代表:红 R,绿 G,蓝 B,888 是指 R、G、B 分别有 8bit,也就是 R、G、B 每一色光有 28=256 级 阶 调 , 通 过 RGB 三 色 光 的 不 同 组 合 , 一 个 像 素 上 最 多 可 显 示 24 位 的 256*256*256=16,777,216 色。

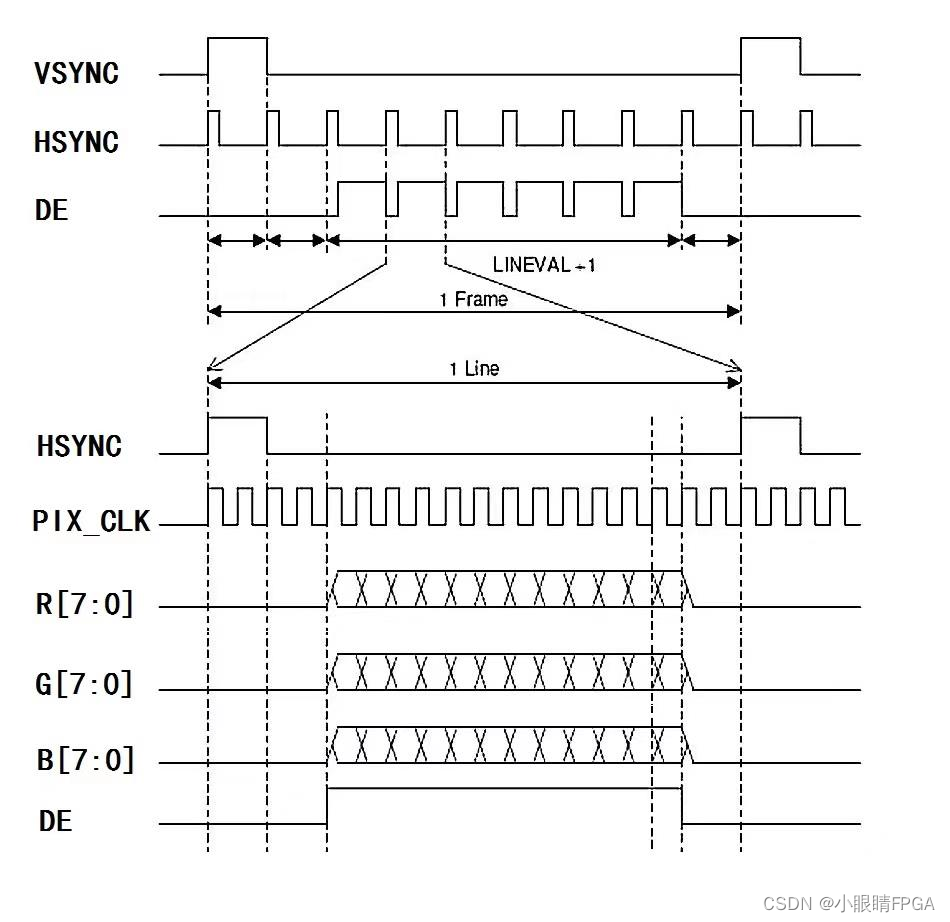

像素数据源源不断输送进来,行、场的切换通过行场同步信号来控制,即 hsync(行同步) 和 vsync(场同步信号)。

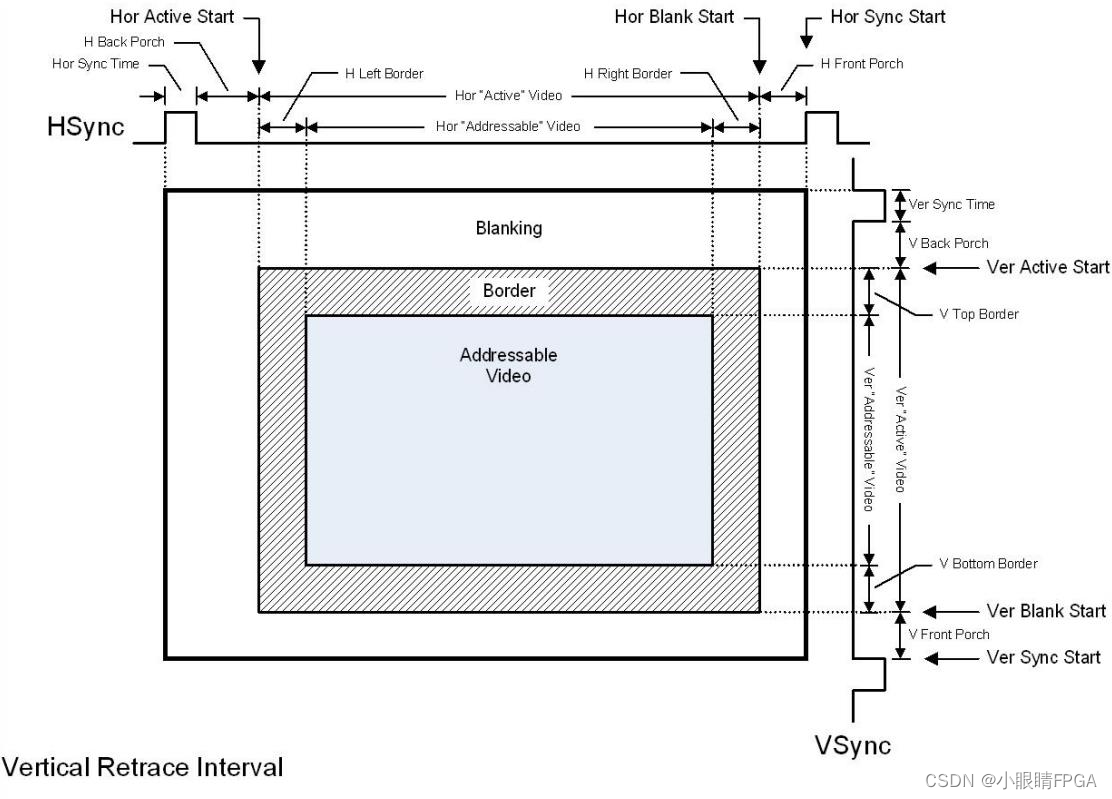

上图中 Addressable 部分内容是在显示器中可看到的区域,像素点是否有效通过 DE 信号 标识;Border 可理解为显示黑边或者显示边框,通常 Border 显示的像素值是 0(黑色)。行、 场切换过程都是在用户感受不到的区域进行的,这个区域就是 Blanking 部分,称为消隐区间。 同步信号上升沿表示新的一行/一场开始,Hsync 对应行,Vsync 对应场。

彩条产生:

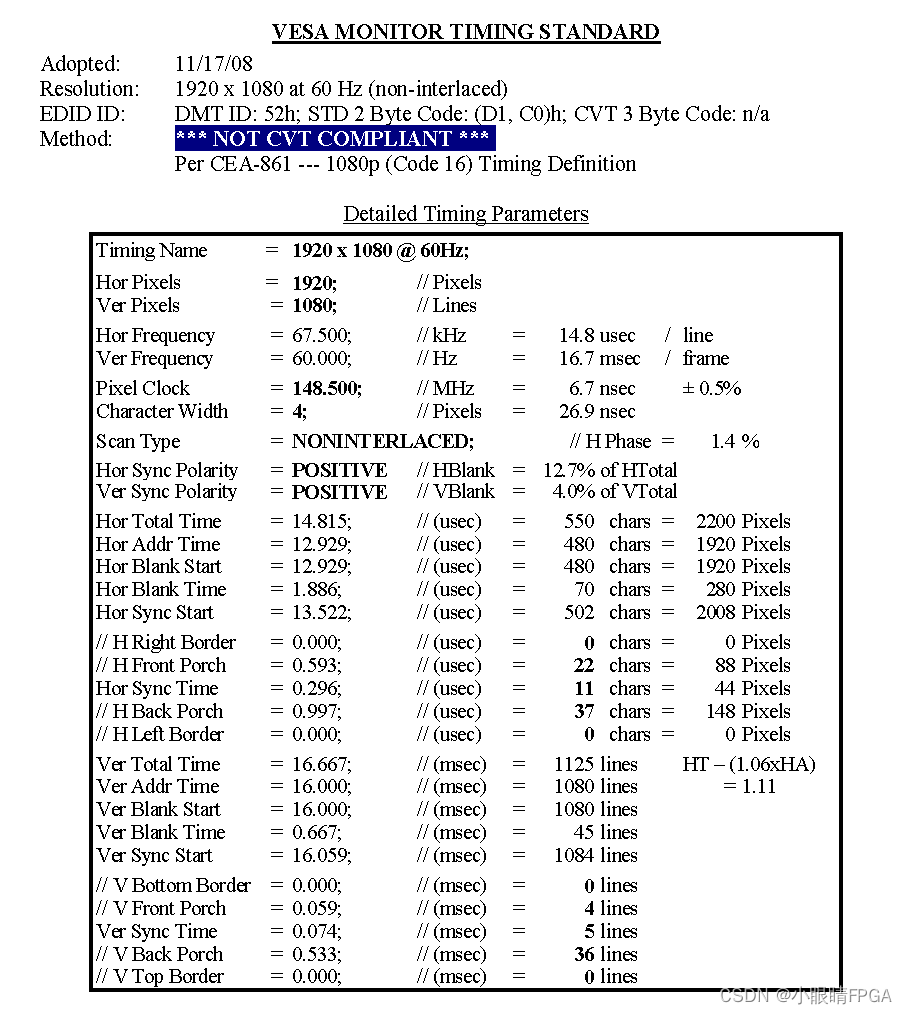

本实验采用 1920*1080@60 的视频规格,详细时序参数如下:

(其他视频规格参数详情请查阅: MES50HP_v1\7_doc\VESA)

HDMI 显示的数据源采用 verilog 编写的显示时序产生模块 sync_vg 实现上图的时序,彩 条生成模块 pattern_vg 根据像素点所在位置,即列数和行数确定像素值,实现彩条图案。

彩条按照每行均匀分成 8 部分,根据每行的像素点数的范围对像素值设置成对应的颜色, 实现彩条信号。

2.HDMI_PHY 配置

MS7200 为 HMDI 接收芯片,MS7210 为 HMDI 发送芯片,芯片的 IIC 配置接口已与 FPGA 的 IO 相连,芯片正常使用需要通过 FPGA 的对芯片进行初始化和配置操作。

hdmi_loop 例程包含对 MS7200 和 MS7210 的配置模块 ms72xx_ctl,已将 MS7200 和 MS7210 配置成 1920*1080@60 RGB888 模式,配置流程参考源码,用户可例化模块 ms72xx_ctl 使用。

四、实验源码设计

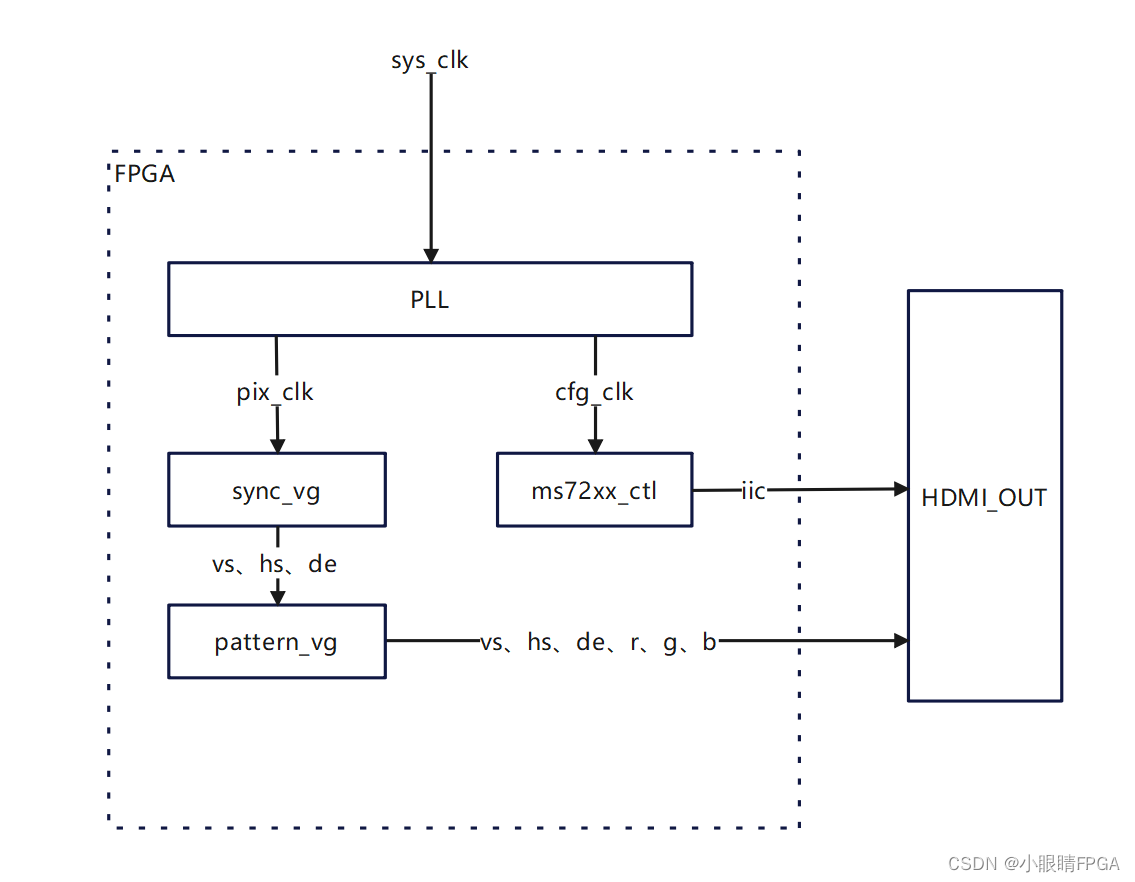

实验 1: hdmi_test HDMI 输出彩条显示例程,分成 4 个模块,时钟模块 pll、MS7210 配置模块 ms72xx_ctl、 显示时序产生模块 sync_vg、彩条生成模块 pattern_vg,以下为模块拓扑图,源码详情请查看 demo。

实验 2:hdmi_loop HDMI 环路例程,将 MS7200 接收的信号给到 MS7210 即可实现 HDMI 环路输出,以下为模块 拓扑图,源码详情请查看 demo。

五、实验现象

实验 1 现象: hdmi_test 连接好 MES50HP 开发板和显示器,下载程序,可以看到显示器显示 8 条彩条。

实验 2 现象:hdmi_loop 连接好 MES50HP 开发板、视频源和显示器,注意视频源必须为 1920*1080P@60,下图为设 置分辨率步骤,下载程序,可以看到显示器显示与视频源一致的图像。

2105

2105

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?