到中流击水—MIG-DDR3

一、到中流击水—DDR3时钟部分

(重点,这一部分时钟关系,能够进一步帮助理解DDR3预读取工作)

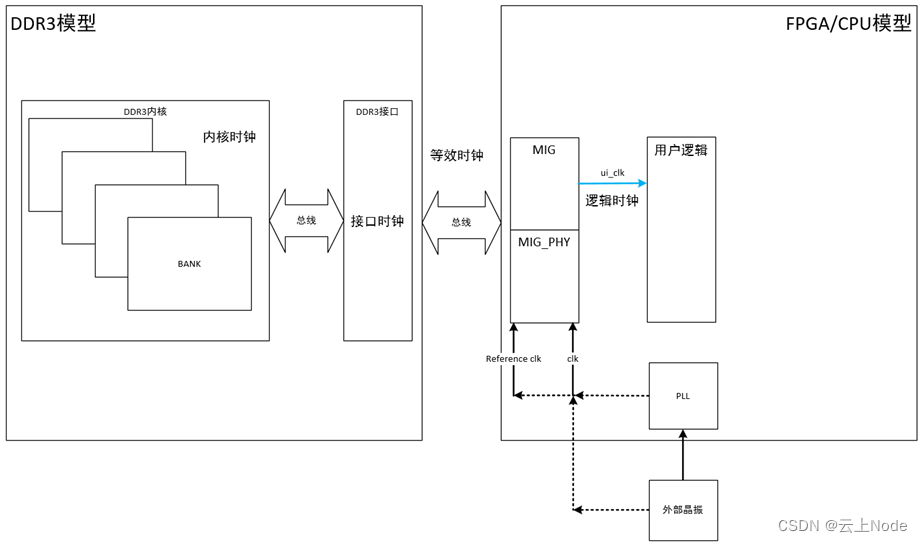

DDR3 FPGA时钟框图搭建

DDR3部分三个时钟(上图左侧部分)

1.DDR3内核时钟:DDR3内部逻辑部分使用的时钟,用户侧无需关心,跟DDR3芯片内核性能相关。

2.DDR3接口时钟:DDR3与外界通信实际使用的时钟(实际时钟),跟DDR3芯片接口性能相关。

3.DDR3等效时钟:DDR3与外界通信实际的有效时钟(双倍速率)。

FPGA部分三个时钟(上图右侧部分)

1.FPGA参考时钟:FPGA用于MIG IP数据传输的参考时钟,固定频率200MHz;

可以由PLL提供、系统时钟(200MHz外部时钟)、外部差分(单端)输入。

2.FPGA IP时钟:FPGA用于MIG IP内部逻辑的时钟;

它可以由PLL提供、外部差分(单端)输入。

3.FPGA用户时钟:FPGA用于给用户提供设计的时钟;

它是由MIG控制器输出给用户的时钟。

DDR3芯片预读取原理

上图分析可知,内核,接口所用的时钟频率不同,所以可以有如下假设:

假设内核工作在100MHz,接口工作在400MHz。内核一次把8bit’数据准备好,来满足接口双沿传输使用(8:1);这就是预读取原理。在不提升内核工作频率情况下,通过预读取方法提高数据传输带宽。

上述部分内容参考了部分网友分享的资料

重点

MIG ip配置完成后,用户只需要关心例化模板ui_clk。因为用户实际使用的时钟是mig ip 提供的(ui_clk),而不是直接使用晶振或pll给的时钟。

二、到中流击水—MIG(MIS) DDR3 UI

MIG—ui接口一图知天下

我们用三个图,表达原理。原理清楚了,配置MIG IP也就非常简单。

一味蛮干是工具人,好思路往往起到事半功倍作用。

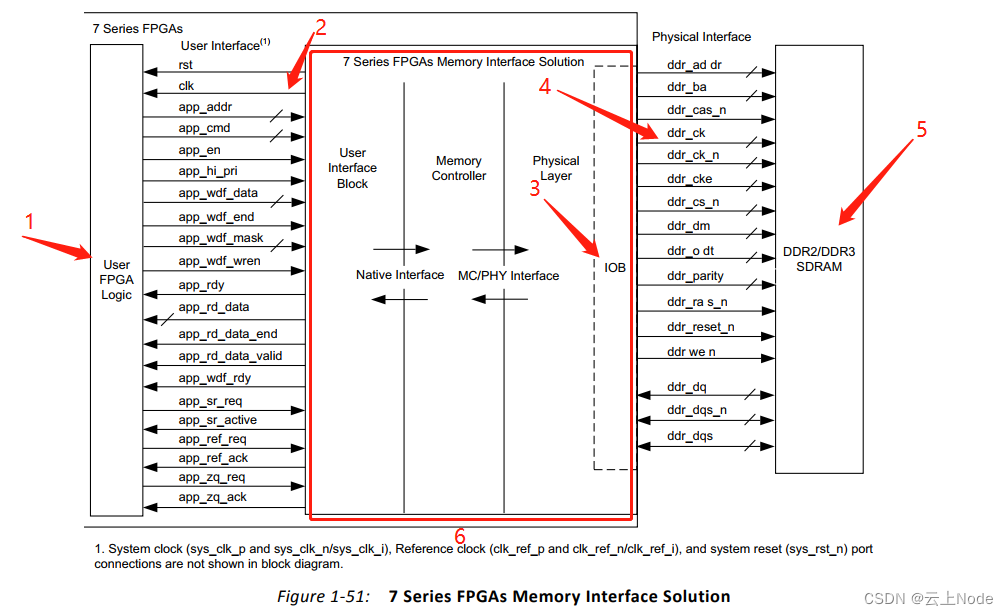

1.ui接口原理框图

序号

1.用户需要写逻辑的部分(基于此接口开发逻辑)

2.用户需要关心的信号(主要完成地址、数据、读写控制),其中,用户逻辑由MIG 控制器输出的时钟驱动,MIG 时钟与用户时钟频率一致(非常重要,请记住,不然在后文用户接口计算数据位宽会产生各种不理解)。

3.IO物理连接管脚区域(约束管脚)

4.FPGA与DDR3实际发生数据需要的信号(用户不用关心)

5.DDR3存储器(配置MIG IP需要选择是颗粒还是条等信息)

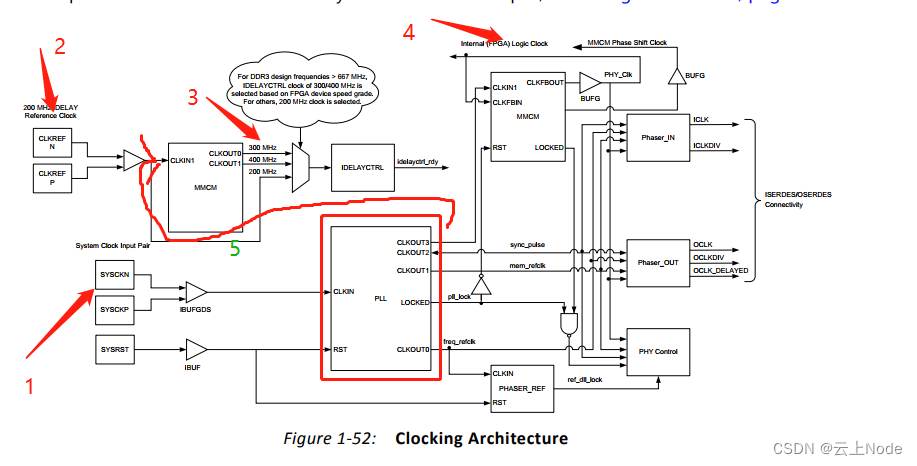

2.MIG ip核时钟原理图

1.MIG IP核输入时钟,根据开发板晶振频率决定。

2.IDELAY 参考时钟,用户只需要记住它是200MHZ频率即可(可以是外部时钟,可以是PLL出来的时钟,参考第5点内容)。

3.频率选择器,它有MIG自动完成配置,用户无需关心。(由MIG IP核配置的DDR频率决定)

4.表明大量内部逻辑是由PLL输出时钟驱动,用户无需关心。

5.IDELAY 参考时钟,它不仅可以由外部输入,也可以由1输入的时钟驱动,但需要倍频到200MHZ。(配置MIG IP核需要关注点)

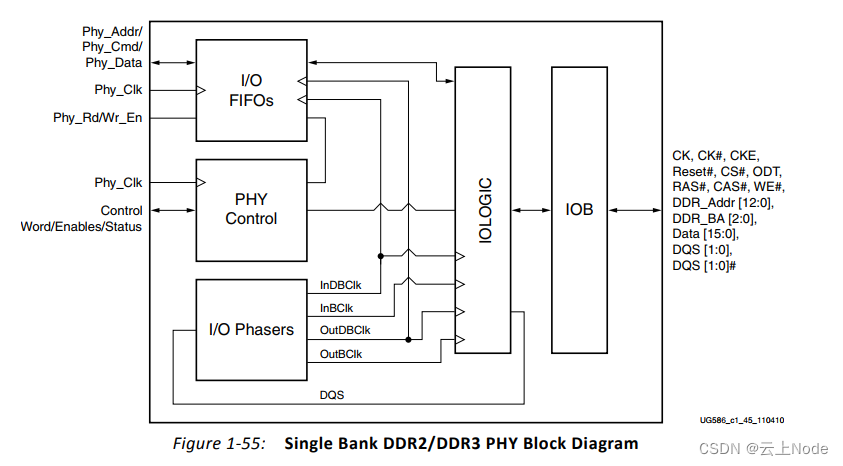

3.MIG PHY图

跟用户关系不大;管脚约束也只需要关注是哪个bank。

DDR3 MIG-IP重点配置参数

按IP配置界面一步一步来就行了,不要怕,不要怕,不要怕。重点说三遍!!!

无非就是如下几个参数:

1.接口频率 ,根据DDR选择

2.接口频率倍数(重点),可以是4:1;可以是2:1;具体根据FPGA能力确定(最高时钟频率、IO翻转能力等等)。

3.DDR3数据位宽;某种程度上影响ui(用户)数据接口位宽,具体需要结合突发长度、上述第二条时钟比来确定。

4.ui接口的封装,非AXI接口。

5.管脚约束及校验…

重点:ui(用户)数据位宽计算。

突发BL=8(perfetch 8bit数据),不解释了吧。由3代控制器IP决定。(参考本文第一部分内容,时钟驱动问题)

1.采用4:1模式,假设FPGA IO接口时钟频率 400MHZ;MIG IP时钟和用户时钟都是100MHZ;

2.DDR3数据传输速率可以暂理解为800MHZ(双沿传输);也就是IO传输速率是 800Mhz/s bit 。

3.用户只有100MHZ时钟,那么只能一个时钟提供8倍DDR3接口 位宽 的数据才能满足传输。

4.假设DDR3 芯片位宽为16bit;那么用户测数据位宽应为16*2(双速率)*4(时钟比例)=128bit。

5.用户侧8倍于DDR3接口侧数据位宽,也正好能够满足BL=8(突发8)。注意,这是是恰巧。正式因为这个恰巧,也是我们的用户逻辑设计比2:1模式变得简单。

6.数据位宽由MIG IP核采用并串转换实现一次perfetch 8预读(突发).

4.ui接口信号

比较简单;不做阐述

5.ui接口时序

比较简单;不做阐述;但仍有重点,写时序控制。CMD 与 WRDATA对应关系;信号采用统一对齐。

6.ui接口逻辑

三段状态机。空闲、写数据、写完成、读数据、读完成、空闲;

跳转逻辑比较简单;具体可按自己习惯写。

调试测试是工具人干的事…

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?