Xilinx MIG IP核使用

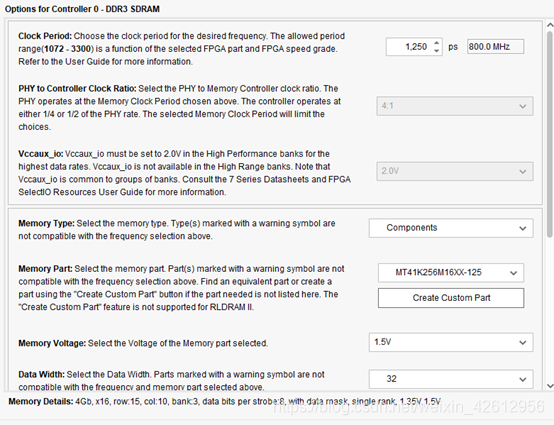

Clock Period:选择ddr芯片的工作时钟(这个时钟是从FPGA接口到DDR的时钟,ddr芯片会以这个时钟采数据)

PHY to Controller Clock Ratio:选择4:1或者2:1,可以理解为ddr3的工作时钟频率:用户时钟频率 = 4:1。

Memory Type:选择DDR3的芯片形式,主要有Component、RDIMMs、UDIMMs和SODIMMs四类,如果硬件选用的是DDR3芯片颗粒,则选择Component,如果硬件选用的是内存条形式,则选择RDIMMs、UDIMMs或SODIMMs中的某类,RDIMMs全称Registered Dual In-line Memory Module,带寄存器的双列直插内存模块;UDIMMs全称Unbuffered Dual In-line Memory Module,即无缓冲双列直插内存模块;SODIMMs全程Small Outline Dual In-line Memory Module,即小型双列直插式内存模块;

Memory Part:选择具体的DDR3型号。

选择ddr芯片型号(根据开发板定,如果只是看一下仿真,可以随意选择),

其中芯片名字有两个重要的点,位宽和容量,以上为例代表这一片ddr的位宽为16,总容量为256Mb x 16bit = 512MB。

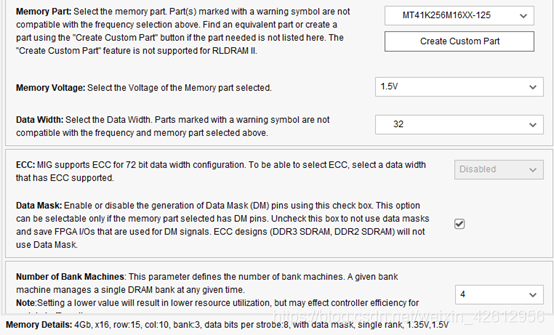

Memory Voltage:由芯片决定,芯片手册上有

Data Mask:数据宽度,一片ddr位宽为16,我现在是使用了两片ddr,所以位宽为32.

ECC:只有数据位宽为64时,可以选择8位的ecc校验码(总位宽就为72)。

Data Mask:数据掩码。

Memory Details:DDR信息的一个小总结,4Gb代表总容量(也就是512MB),x16为位宽,row为行,col为列,bank为2的3次方,可以通过这里算出一片ddr的容量,

16bit x 2^15 x 2^10 x 2^3 = 512MB

注意:这一栏只显示一片ddr的信息。

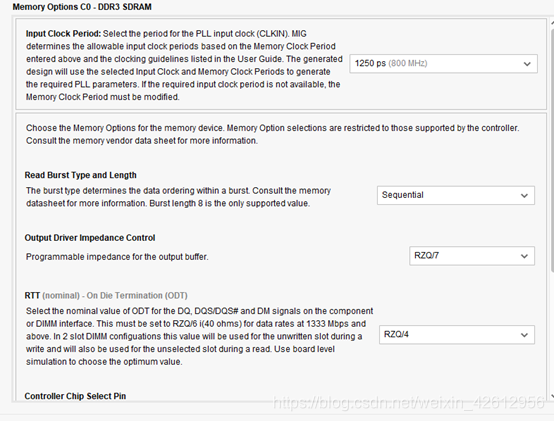

Input Clock Period : MIG IP核的输入时钟(我这里设置的100m,不知道软件有bug还是我操作不对,每次点进来都会变成800m,但是使用的时候还是100m)。

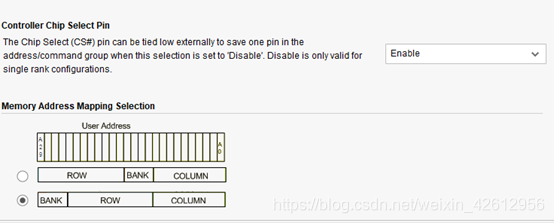

Memory Address Mapping Seletion :选择地址映射方式:

BRC这种映射方式,用的最多。其优点是,功耗低;

RBC的优点是适合数据流方式去访问数据,性能好;

其它项一般不用改变

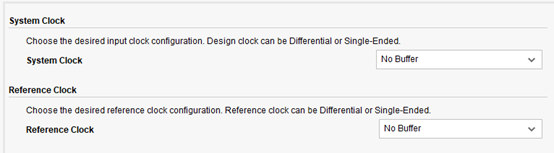

设置Referce Clock、System Clock:

可以选择单端,差分和No Buffer;

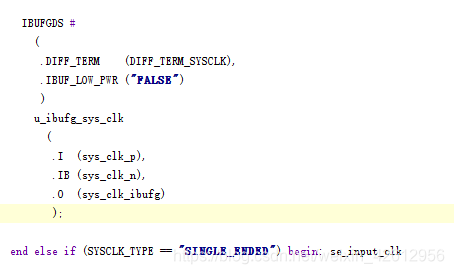

如果Referce Clock、System Clock这两个时钟设置为单端或者双端,IP核内部会为这两个时钟做缓存一下(这个叫法可能不太对);打开IP核内部会看见这样的一个原句(没有截全)

这两个原句只能对从IO输入的时钟使用,所以只能选择由外部输入的时钟。

如果选择no buffer就没有这个原句,就可以直接使用由FPGA内部其它模块送过来的时钟。

总结一下这个IP核里面的三个时钟:

第一个时钟(名字还真想不起来)是由FPGA通过管脚送到ddr芯片的时钟,由ddr芯片的工作频率决定

Sys_clk:这个时钟是由我们向MIG IP核提供的时钟,我们不在这个时钟域处理数据,IP核会送出来一个ui_clk,我们所有的操作包括发送接收数据都要在ui_clk这个时钟域,ui_clk和第一个时钟的比例关系也就是4:1;

Ref_clk:在migIP核中使用了idealy,odelay,idelayctrl原句,idelayctrl原句需要提供一个ref_clk作为基准。

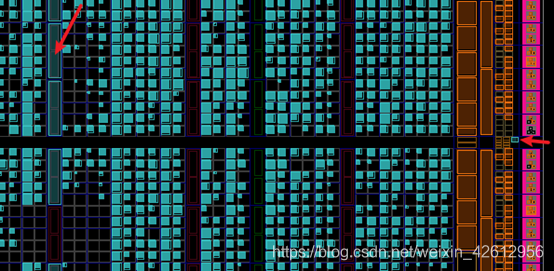

下图中左边标出来的长方形的蓝色是使用了的block ram资源,左边蓝色(除了block ram)是已经使用了的可配置逻辑块的资源,右边黄色(包括标出来的蓝色小块)是已经使用了的selectIO资源,其中标出来的蓝色小块就是idelayctrl资源。

其实xilinx的很多IP核里面都有ref_clk,一般情况下叫这个名字,那就是上面这种用法(当然,这是我自己的观点)。

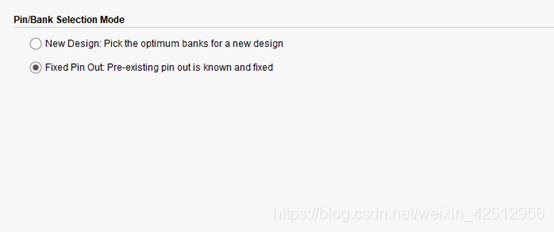

这里第一个的意思是系统给你分配它认为的最合适的管脚(如果只是看一下仿真,可以选择这个),

第二个的意思是你自己分配管脚(因为这里我使用的开发板,所以我选择第二个)

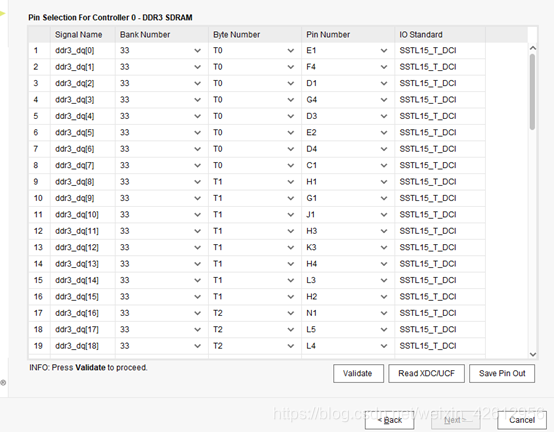

选择第二个就会出现这个页面,可以直接读SDC或者UCF文件(这个文件一般开发板的ddr例程就有,直接拽过来就可以使用)点击validata,验证通过后,下一步

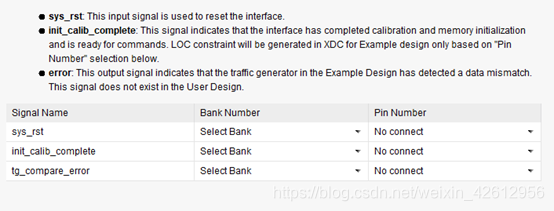

这一页也是在分配管脚,如果有需要可以将这几个信号接出去,但是这几个信号一般都是FPGA内部使用,所以选择No connect

全文一些是我自己的观点,如果有不对或者没说清楚的地方,非常非常欢迎指出。

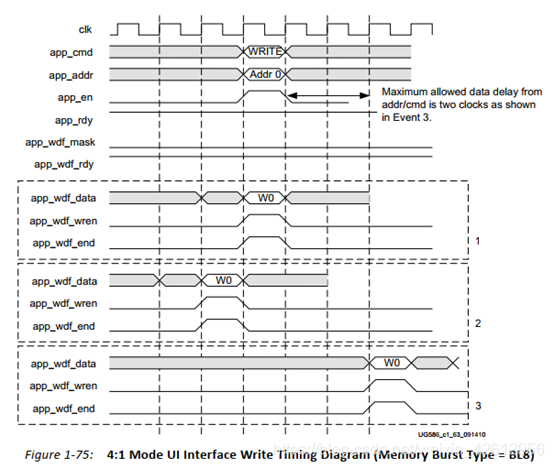

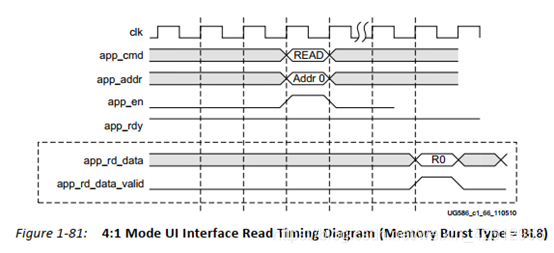

最后贴上4:1的时序图:

时序图来自官方文档:ug586

用户接口简介:

本文详细介绍了Xilinx MIG IP核的配置过程,包括ClockPeriod、PHYtoControllerClockRatio、MemoryType等参数的选择,以及DDR3芯片的选型和地址映射方式。同时,讨论了不同时钟的用途和内部结构,如Ref_clk的使用。此外,还提到了资源占用情况,如BlockRAM、Configurable Logic Block和SelectIO。最后,分享了个人见解,并提供了4:1时序图和用户接口介绍。

本文详细介绍了Xilinx MIG IP核的配置过程,包括ClockPeriod、PHYtoControllerClockRatio、MemoryType等参数的选择,以及DDR3芯片的选型和地址映射方式。同时,讨论了不同时钟的用途和内部结构,如Ref_clk的使用。此外,还提到了资源占用情况,如BlockRAM、Configurable Logic Block和SelectIO。最后,分享了个人见解,并提供了4:1时序图和用户接口介绍。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?