- 1. 第一代 AMD EPYC 处理器 Naples

- 2. 第二代 AMD EPYC 处理器 Rome

- 3. 第三代 AMD EPYC 处理器 Milan

- 4. 第三代 AMD EPYC 处理器 Genoa

1. 第一代 AMD EPYC 处理器 Naples

第一代AMD EPYC处理器(以前代号为“Naples”)设定了32核的目标,以在服务器CPU市场上竞争。

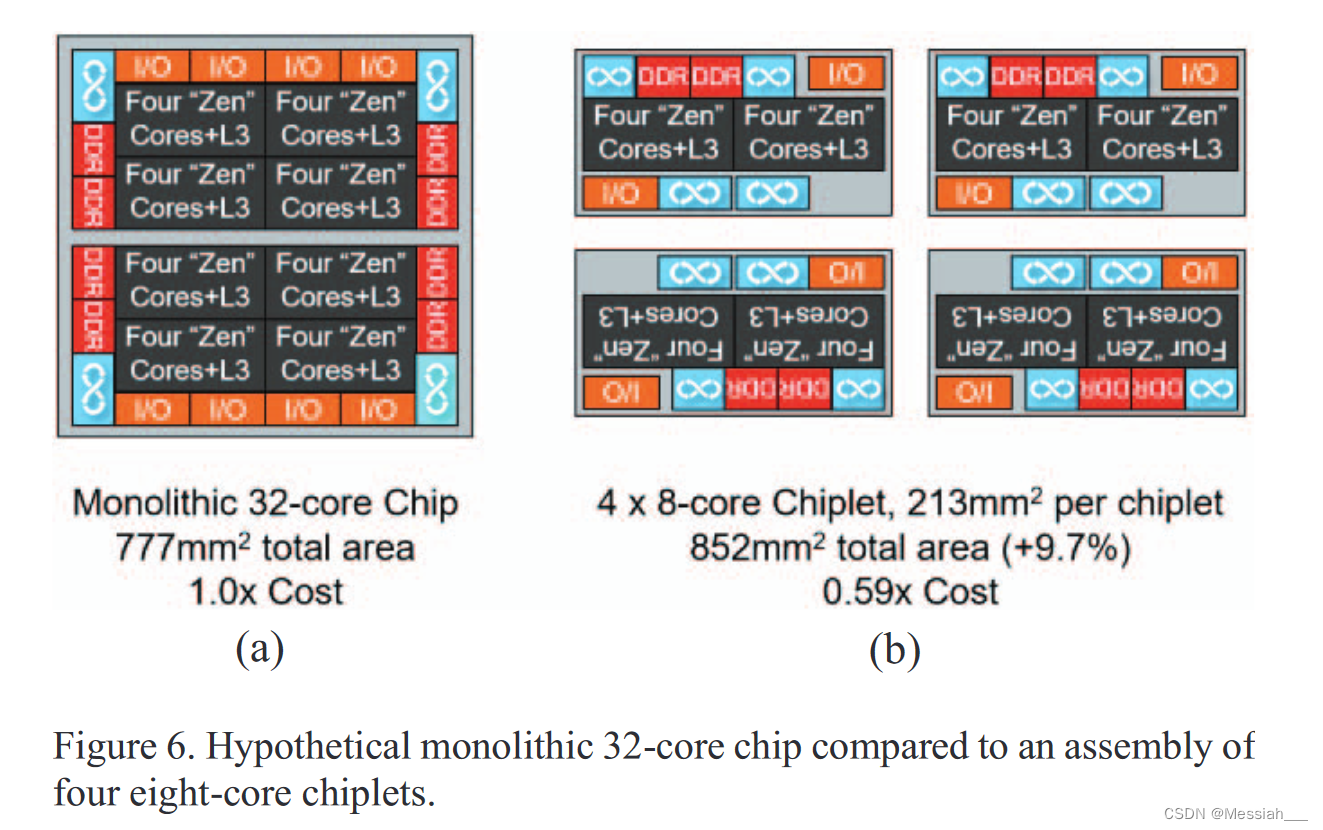

图 6(a) 显示了一个假设的单片32核处理器的原理图。根据我们的内部分析和产品规划练习,这样的处理器在14nm制程中需要777mm2 的芯片面积。虽然仍在光栅限制范围内,因此在技术上是可制造的,但如此大的芯片将非常昂贵,并使产品处于潜在的无竞争力地位。

第一代 AMD EPYCTM 处理器采用了具有四个相同小芯片的设计,代号为"Zeppelin",如图 6(b) 所示。每个小芯片提供八个"Zen"CPU 内核、两个 DDR4 内存通道和 32 通道 PCIe。另外,还需要额外的芯片面积来实现Infinity Fabric™互连四个小芯片以及III-B节中讨论的其他单芯片电路。因此,每个晶片的14nm制程的晶片面积为213 mm2,总的晶片面积为 4 * 213mm= 852 mm2。这里约有10%的芯片面积开销,而AMD估计4个chiplet设计的最终成本仅为单片方法的0.59,尽管总硅片消耗量多出约10%。

2. 第二代 AMD EPYC 处理器 Rome

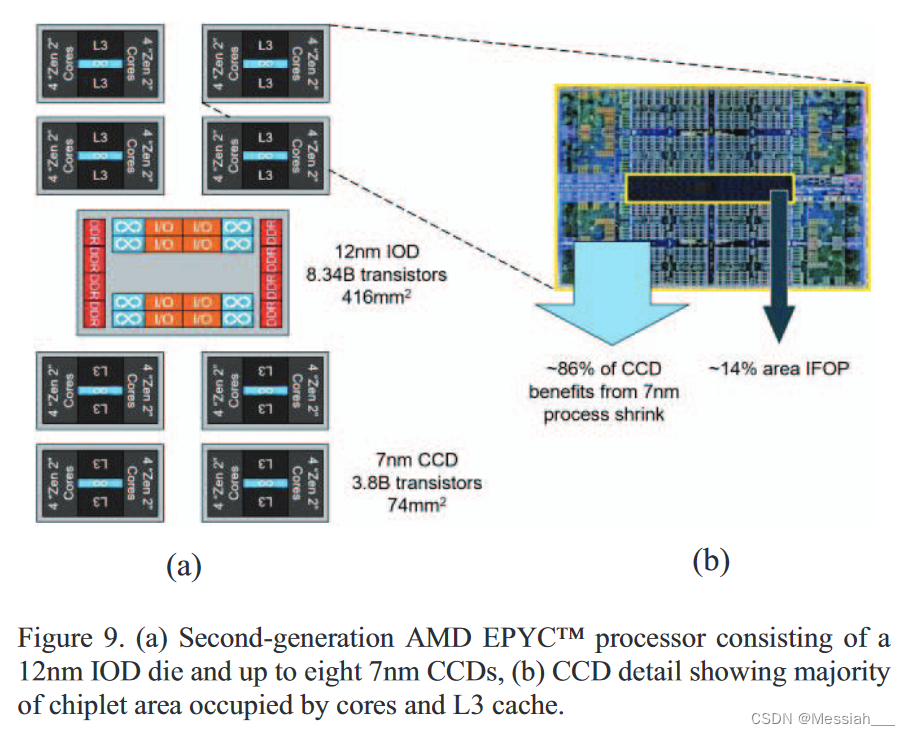

第二代AMD EPYC™处理器,以前代号为"Rome",采用双芯片方法。第一个芯片称为I/O芯片(IOD),采用成熟且具有成本效益的12纳米工艺实现。IOD的尺寸为416 平方毫米,有83.4亿个晶体管,它包含8个DDR4存储通道,128个PCIe gen4 I/O通道,其他I/O如USB和SATA, SoC数据结构和其他系统级功能。

第二个芯片是核心复合芯片(CCD),在领先的7nm节点上实现。每个CCD的尺寸只有~74mm2 ,即使在新工艺节点的早期,也能获得非常好的良率。图9(a)显示了如何将一个IOD与多达八个CCD组装在一起。每个CCD提供8个"Zen 2"CPU内核,实现64个内核。

3. 第三代 AMD EPYC 处理器 Milan

第三代AMD EPYC 处理器继续采用了 9 个小芯片的 Chiplet 设计,在一个 SoC 里封装了 8 个运算 CCD 与 1 个 IO Die,每个 CCD 小芯片中的 8 个核心都能够同时共享 32MB 的缓存,以此来降低时延,同时对于那些需要用内存子系统比较密集的应用来说它可以有效地提高性能。

4. 第三代 AMD EPYC 处理器 Genoa

第四代AMD EPYC 处理器的首要技术特点是基于业界领先的5nm的制程工艺,提供多达96颗“Zen 4”架构核心、192线程,以及最大384MB的L3缓存容量。这样的组合提供了领先的性能,不论是单核性能,还是整个插槽的吞吐量。第四代EPYC产品继续采用基于小芯片(Chiplet)的设计,其中的CCD使用5nm制程工艺,每CCD包含8个内核;IOD使用6nm制程工艺;全产品系列使用了2到12颗不等的CCD数量。

[1] Naffziger S, Beck N, Burd T, et al. Pioneering chiplet technology and design for the amd epyc™ and ryzen™ processor families: Industrial product[C]//2021 ACM/IEEE 48th Annual International Symposium on Computer Architecture (ISCA). IEEE, 2021: 57-70.

本文概述了AMD的AMDEPYC处理器系列,从第一代的Naples到第四代的Genoa,介绍了芯片设计的变化,包括从单片到Chiplet设计,以及工艺节点的提升,如12nm、7nm和5nm。

本文概述了AMD的AMDEPYC处理器系列,从第一代的Naples到第四代的Genoa,介绍了芯片设计的变化,包括从单片到Chiplet设计,以及工艺节点的提升,如12nm、7nm和5nm。

1467

1467

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?