之前跟小梅哥文档做的练手小实验,放上来做个总结。

本试验基于开发板上已有的ADC128S102CIMTX和DAC TLV5618a这两块芯片,他们的用户手册会随代码一同打包。

实验内容大概是:没有画图是因为了重装电脑,visio没下好,不是偷懒(

ADC芯片 ← ← ← ↑

↓ ↑

PC ← 串口发送 ←FPGA →DAC芯片 ↑

首先阅读用户手册:

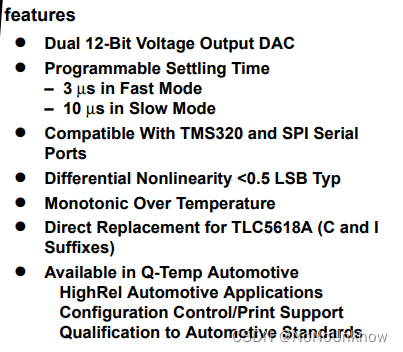

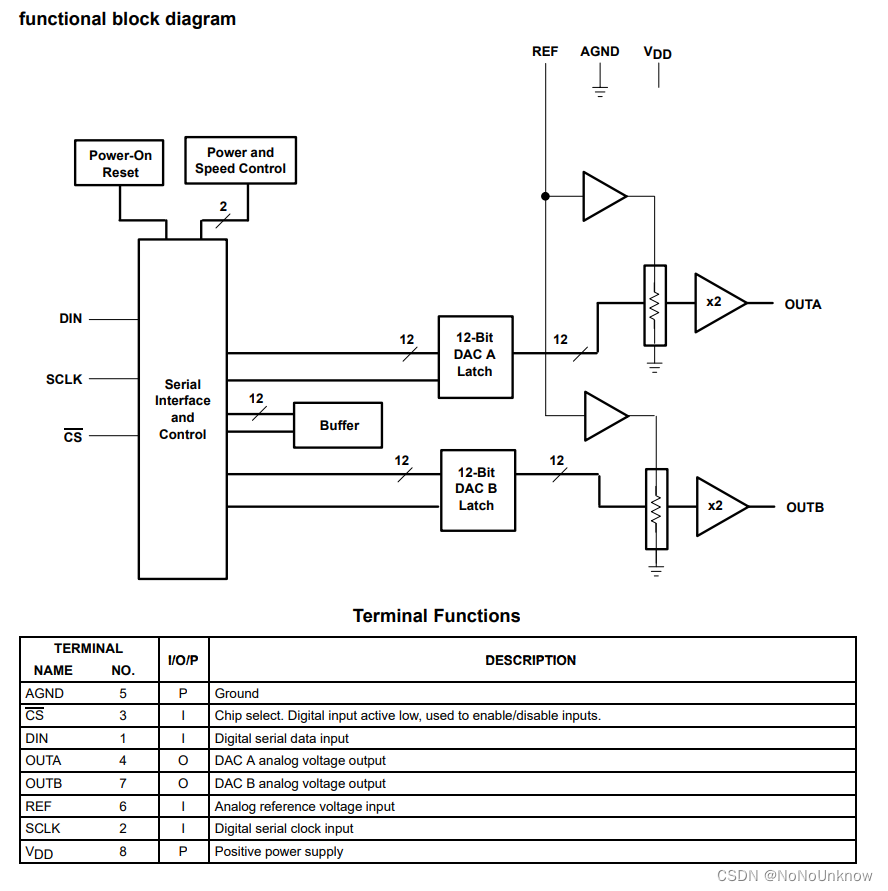

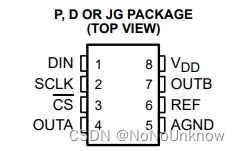

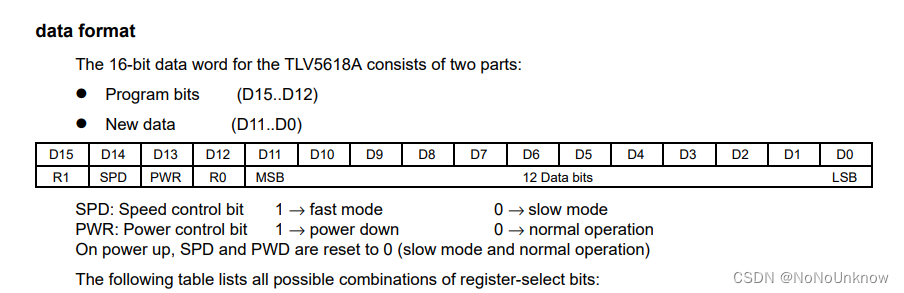

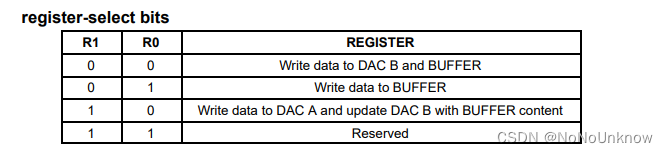

DAC手册:

12位两路电压输出,SPI协议。

非常简单。至少比我找CSDN怎么关水印要简单很多。

非常简单。至少比我找CSDN怎么关水印要简单很多。

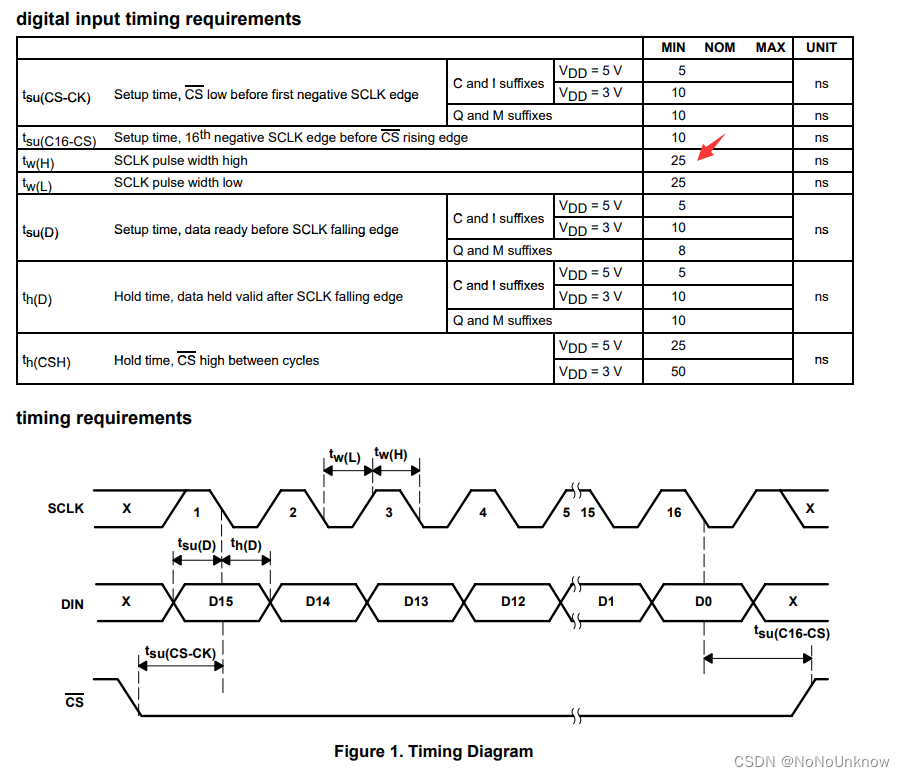

1/50ns→20mhz,信号保持一个周期问题不大,可满足su,hold time。

数据将在FPGA时钟上升沿修改,其在下降沿读取。

参数配置:通过同时控制双通道的有序输出,可以实现多位输出,但此处不做赘述。

代码如下:

///

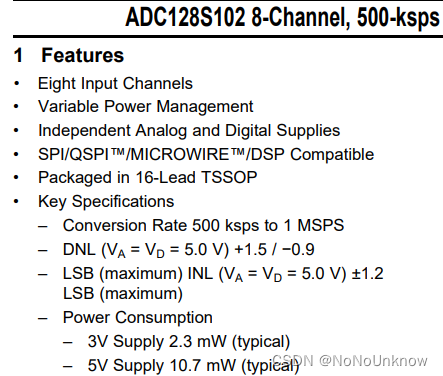

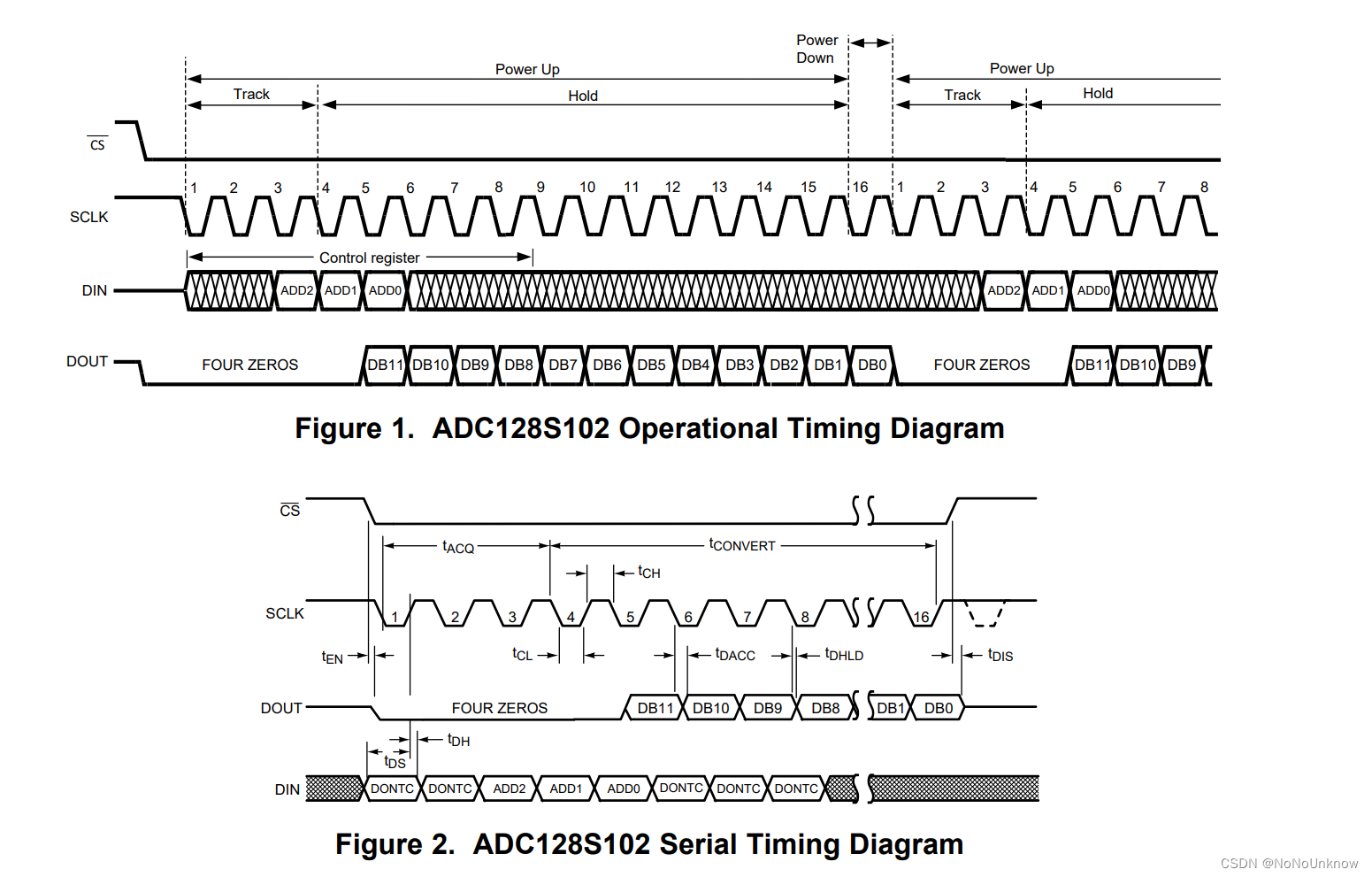

ADC手册:

值得一提:此处的DOUT输出的是上一轮ADDR的输出,毕竟ADDA的转换需要时间。

///

懒得写了,这个做的没意思,总结起来也很没意思,照着手册写完事。

5644

5644

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?