1. 地址增加长度

项目中使用的ddr位512*16 共4片,因此一次可写入64位,突发长度8 。每次写入数据是512位。

举例:写入147456bit数据,总共写入地址位147456/64=2304 。需要传输次数为:147456/512=288次。初始地址为0。传完这么多数据后,下一次传输起始地址为2304。

2. 时钟

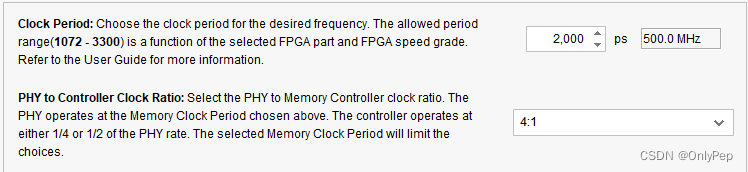

mig核设置如下

图1 user clock

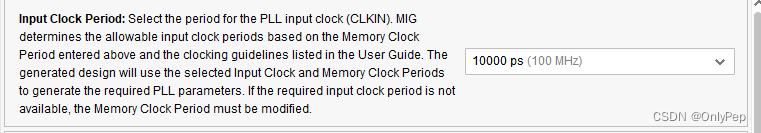

图2 system clock

图3 system clock configuration

clock period 设置成500 ,4:1。mig核会输出一个125M时钟供user使用。这个参数不用管,只要mig核允许即可,内部产生。

input clock period是根据板子来进行设置的,system clock 设置为differential 说明是板子提供了100m的差分时钟。

refenrence clock 设置了 no buffer表示经过pll产生的200m时钟。这里面当system clock 设置成了200m以后,refenrence clock会增加一个use system clock选项。

带宽计算: clock period设置为500M,ddr采样工作频率为1000M。我们项目里面带宽为

1000*64=64000Mb/s=8000MB/s=7.8125GB/s

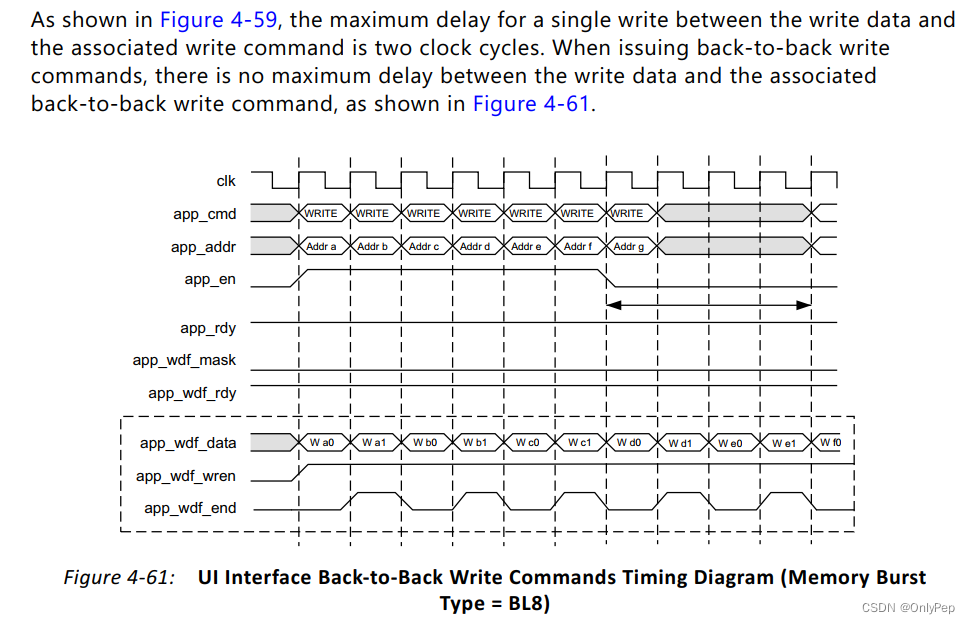

3. 时序

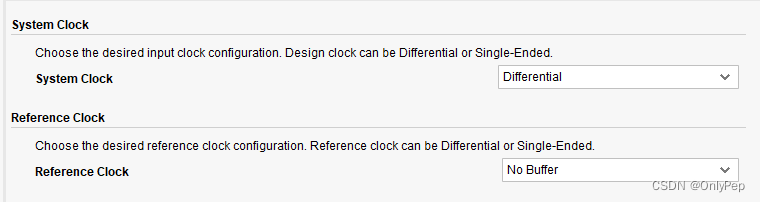

图 4 单个写

3.1 别人的经验

(1) 单个数据写操作 — 因为读操作很简单,故此处只讨论写操作

地址控制信号与写数据信号严格按照时序图图4要求即可,最好是都对齐。 判定写允许信号可以设定为app_rdy & app_wdf_rdy。 为简单起见,可令app_wdf_end = app_wdf_wren。且注意app_en信号有效时间为1clock,不要随意延长为2clock。如果是单个数据写操作一直写入100个数据,那么app_en信号和app_addr信号有效时间均为100clock,且需要完全对齐,

图5 连续写

由于写数据不用受到写指令时序的影响,可以让地址控制信号与写数据控制信号完全独立。分别用独立的计数器是控制各自的有效时间。通过实际调试发现:app_wdf_rdy有效时间 比 app_rdy有效时间更连续。举例说明如下:

假设单次写入数据长度为128个,当写数据计数器累加到128时,可能写指令有效计数器此时为100。那么状态机可以切换到下一个状态,改状态只进行写指令操作而不进行写数据操作(因为写数据操作已完成,快于写指令操作),直到写指令计数器也累加到128,从而单次写入数据操作才算是最终完成。

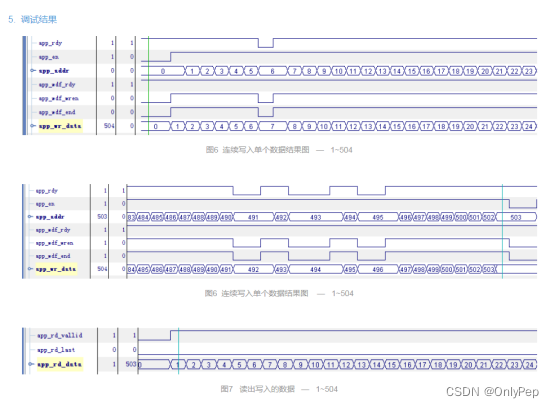

3.2 别人的调试结果

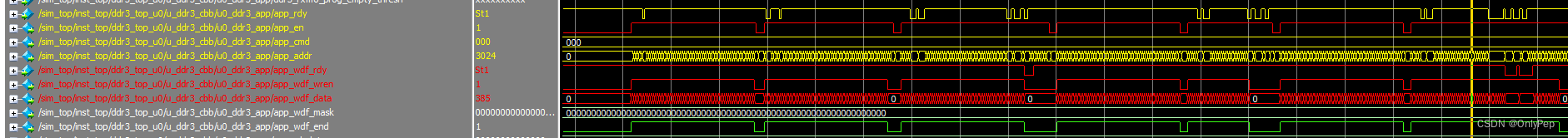

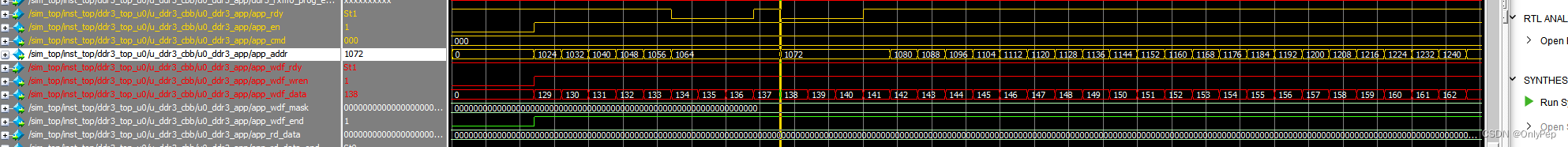

3.3 cbb仿真数据

图8 总体图

图9 局部放大图

图9可以看出这部分没对齐

4. 编程注意

一次写入数据不大于256B,比如512位,一次最多写入512个地址。即不跨256B,DDR交织的概念。

5. 参考

Xilinx FPGA平台DDR3设计保姆式教程(2)DDR3各时钟频率及带宽分析_子墨祭的博客-CSDN博客_ddr3时钟频率和数据速率

<RTL设计的艺术> 同一次DDR访问“不跨256B”,“不跨4KB”讲解_积小流哥的博客-CSDN博客_为什么一次突发burst不能跨4k地址

1112

1112

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?