Vivado综合时出现[Synth 8-91] ambiguous clock in event control

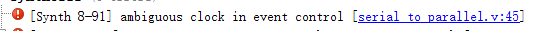

在使用vivado软件进行Run Synthesis综合时,出现这个错误**[Synth 8-91] ambiguous clock in event control** 如下图所示

在网上找了一波,改了一波,发现并没有消掉错误,头比较大,最终还是成功解决掉了。最终找到了博主

@Ysu-Slade的博客,结解决了这个问题。

原博客连接

错误定位在这个always块,我们通常习惯边缘触发,时钟上升沿和复位下降沿写到一起,但是,在always块里面并没有初始化的一些变量,也就是我们并没有用到rst_n,所以综合的时候就会报出上面的错误,将触发模式更改为always@(posedge clk)即可。

这里又一次感受到论坛技术共享带来的福音,所以这里引用一下,发出第一篇博客,并决定从现在开始介入共享大军。

1886

1886

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?