vcs2018+verdi实现独立仿真带有Vivado IP核的工程

前言

在对带有Vivado IP核的工程进行仿真时,通常有联合仿真和独立仿真两种方法。前者通过在Vivado软件内部与其他仿真器联合实现仿真,但这存在很多弊端,例如每次必须同时启动两个软件,不够方便,效率也低;每次修改工程中的文件,都要重新编译整个工程;从别人那里拷贝来工程还要考虑两个软件的版本问题等等…因此独立仿真在实际工程仿真中有重要意义,本文旨在介绍如何用vcs2018+verdi实现独立仿真带有Vivado IP核的工程。

工具准备

使用工具包括vcs-mx2018、dve、verdi和Vivado 2019.2,实现环境是Ubuntu 18.04LTS。前三个软件的安装可以参考下面这篇文章,写的非常详细和全面,照着上面一步步来即可。Vivado建议使用2019.2版本,笔者曾用2018和2017版本的Vivado尝试,均会报错与vcs-2018版本不符合。关于vcs和Vivado的版本对应问题,可自行在网上搜索,必须选择对应的版本。

但需要注意的是,必须用vcs-mx2018代替上述文章中安装的vcs2018,原因在于普通vcs只能编译verilog,但在后面对Vivado IP核库编译时还涉及到VHDL语言,因此必须采用vcs混合编译版即vcs-mx,否则在后续操作时会报错。安装包分享如下:

vcs-mx百度网盘

提取码:22r3

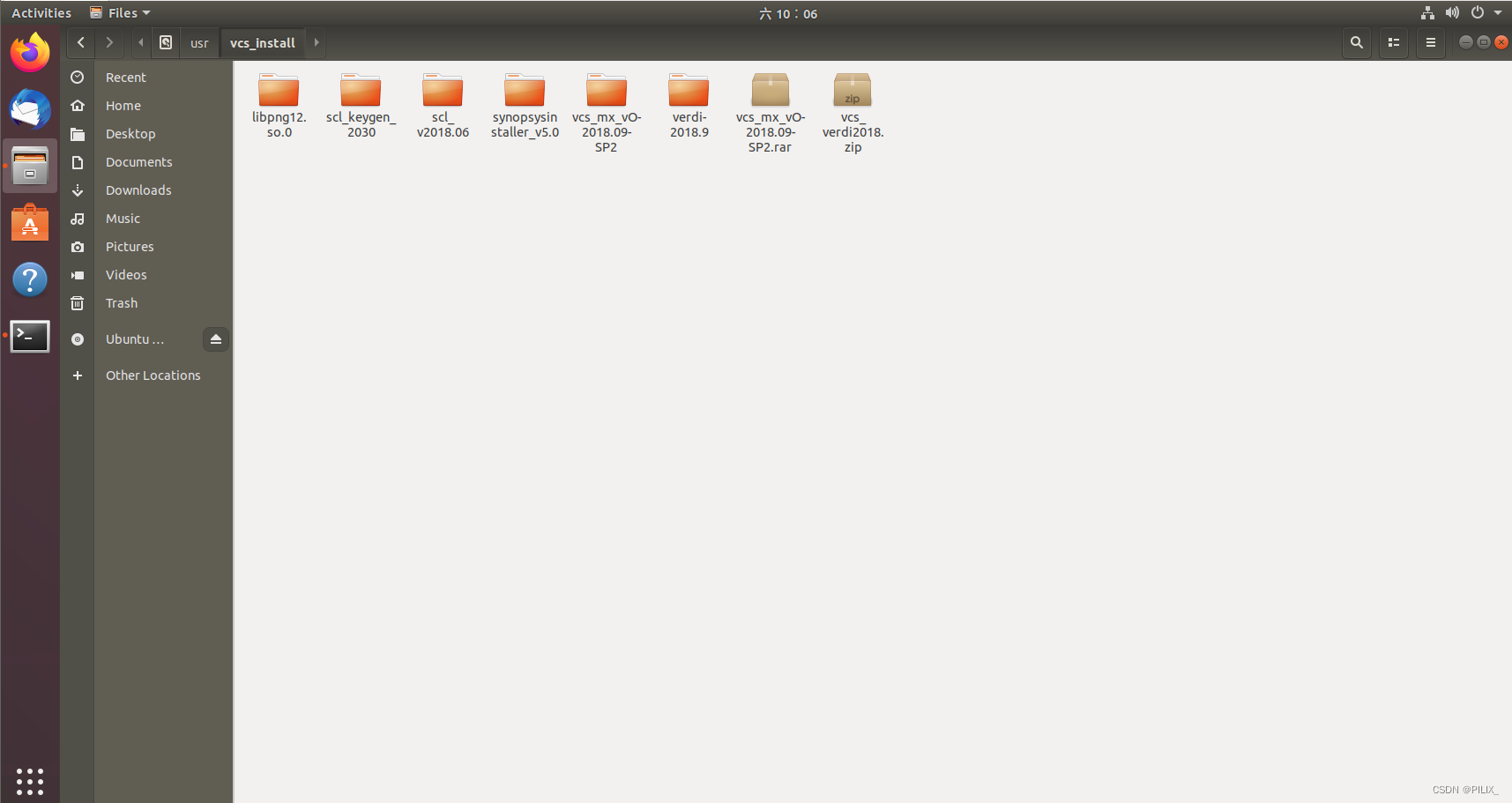

如下图,将VCS2018在Ubuntu20 18安装步骤中的安装包解压后,用vcs-mx百度网盘解压后的文件夹替代其中的vcs_vO-2018.09-SP2

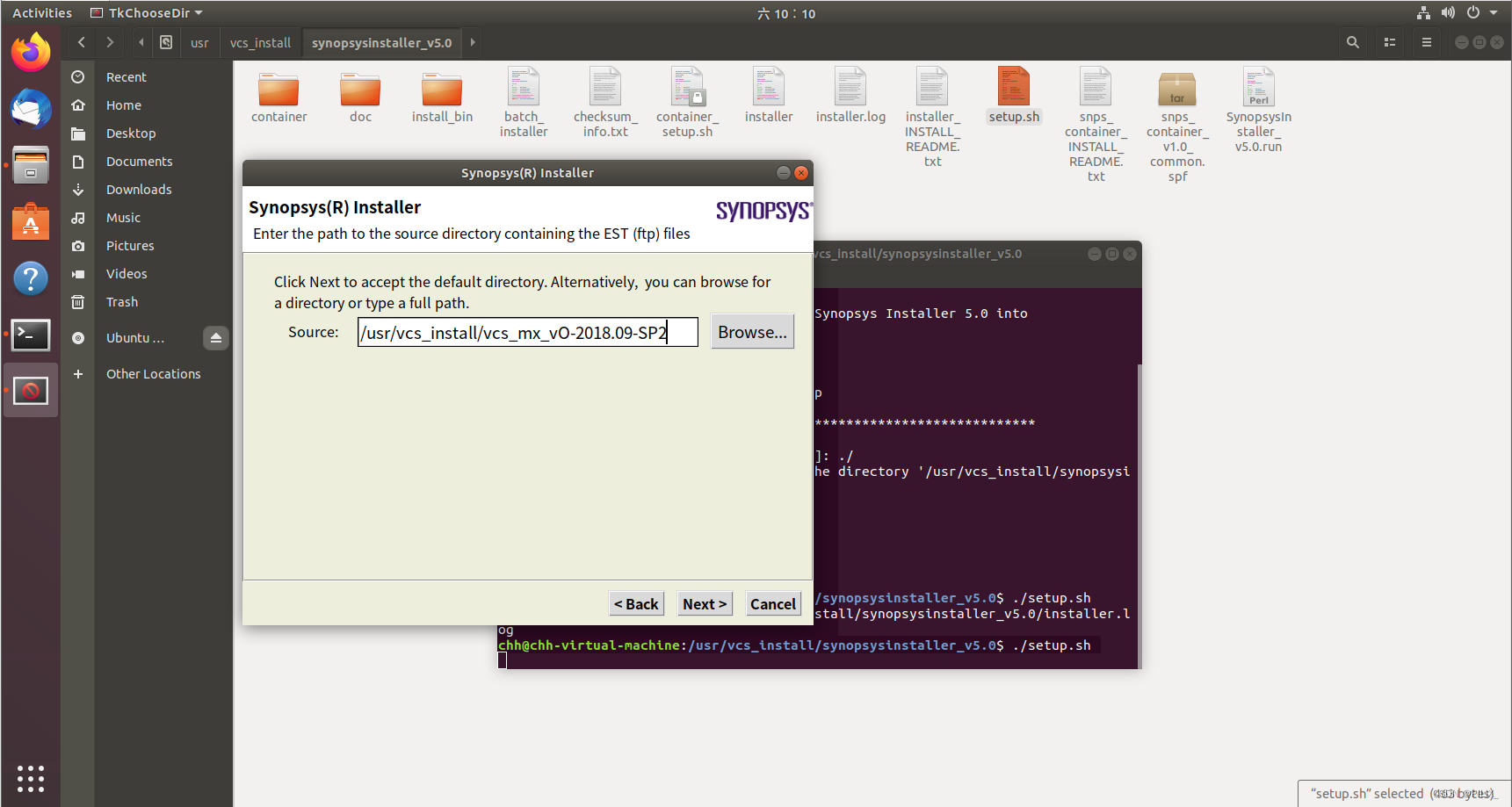

并在后续安装过程中选择安装vcs_mx

vcs编译Vivado库文件

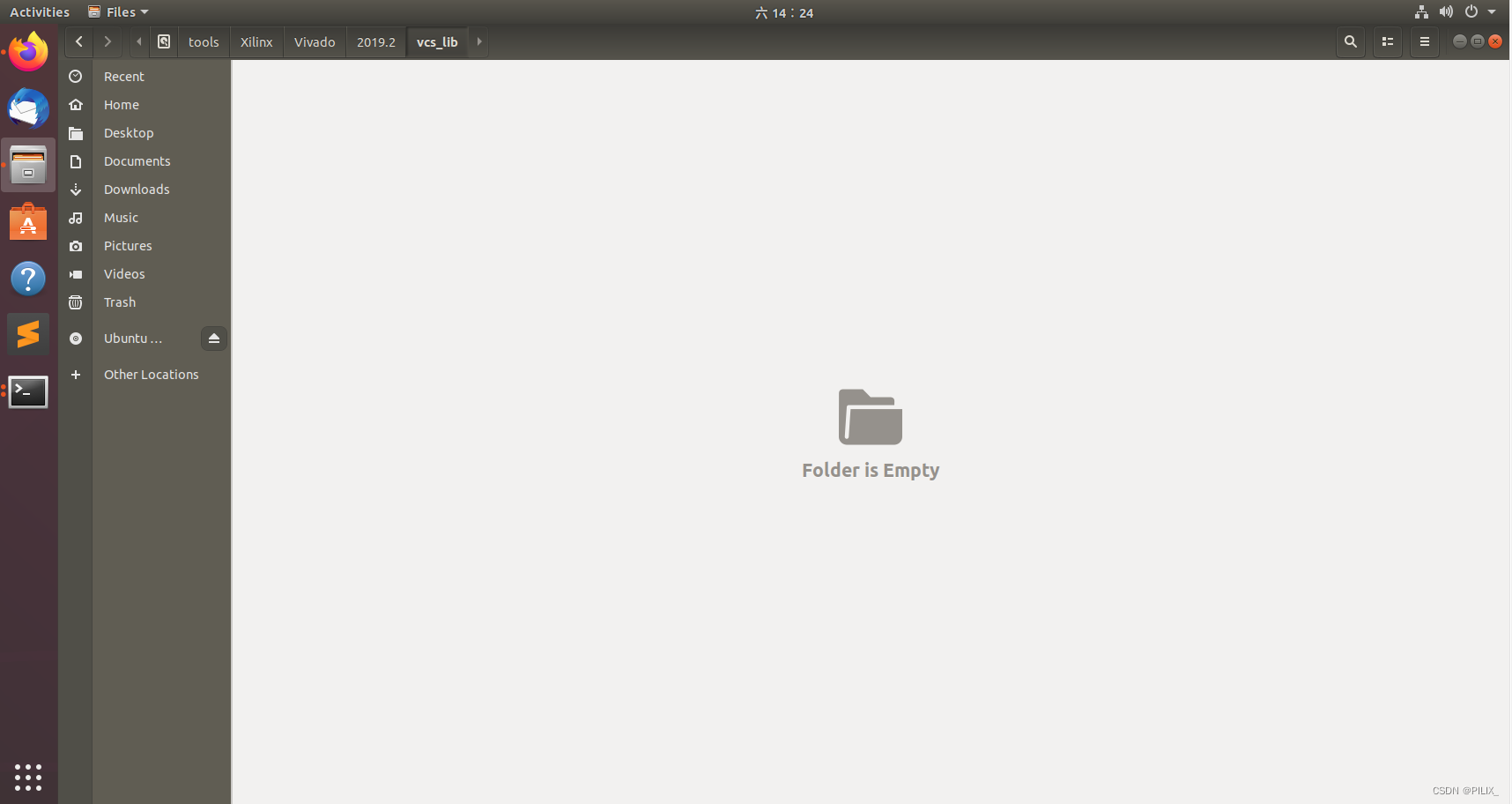

在安装完一系列软件后,首先要编译Vivado库文件,如下图所示,在Vivado的安装路径新建一个"vcs_lib“文件夹用于放编译好的一系列库文件:

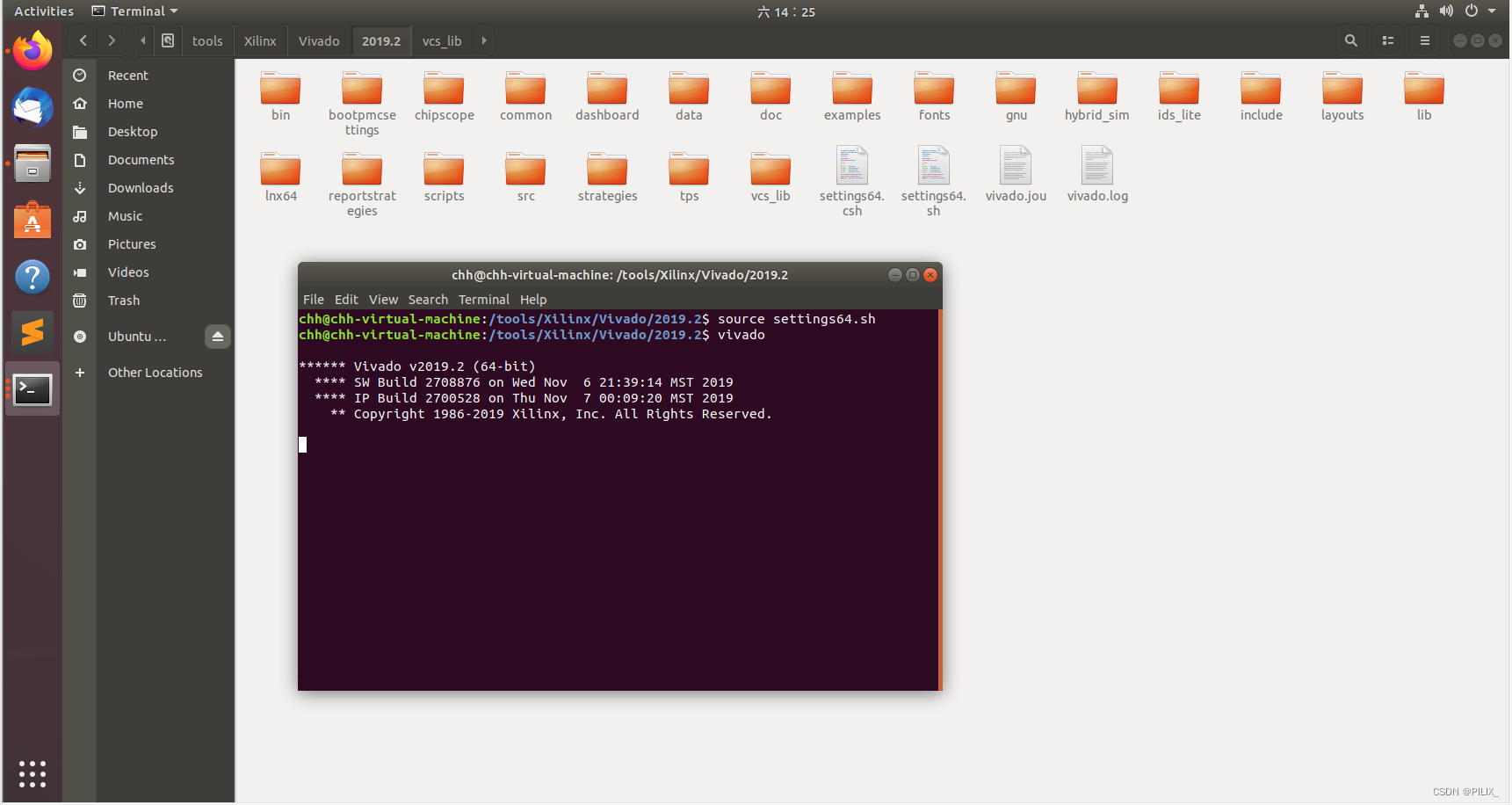

接着,在Vivado的安装路径下(我这里是/tools/Xilinx/vivado/2019.2)用如下命令行的方式启动vivado,如果直接在图形化界面双击打开,编译时可能会报错。

source settings64.sh

vivado

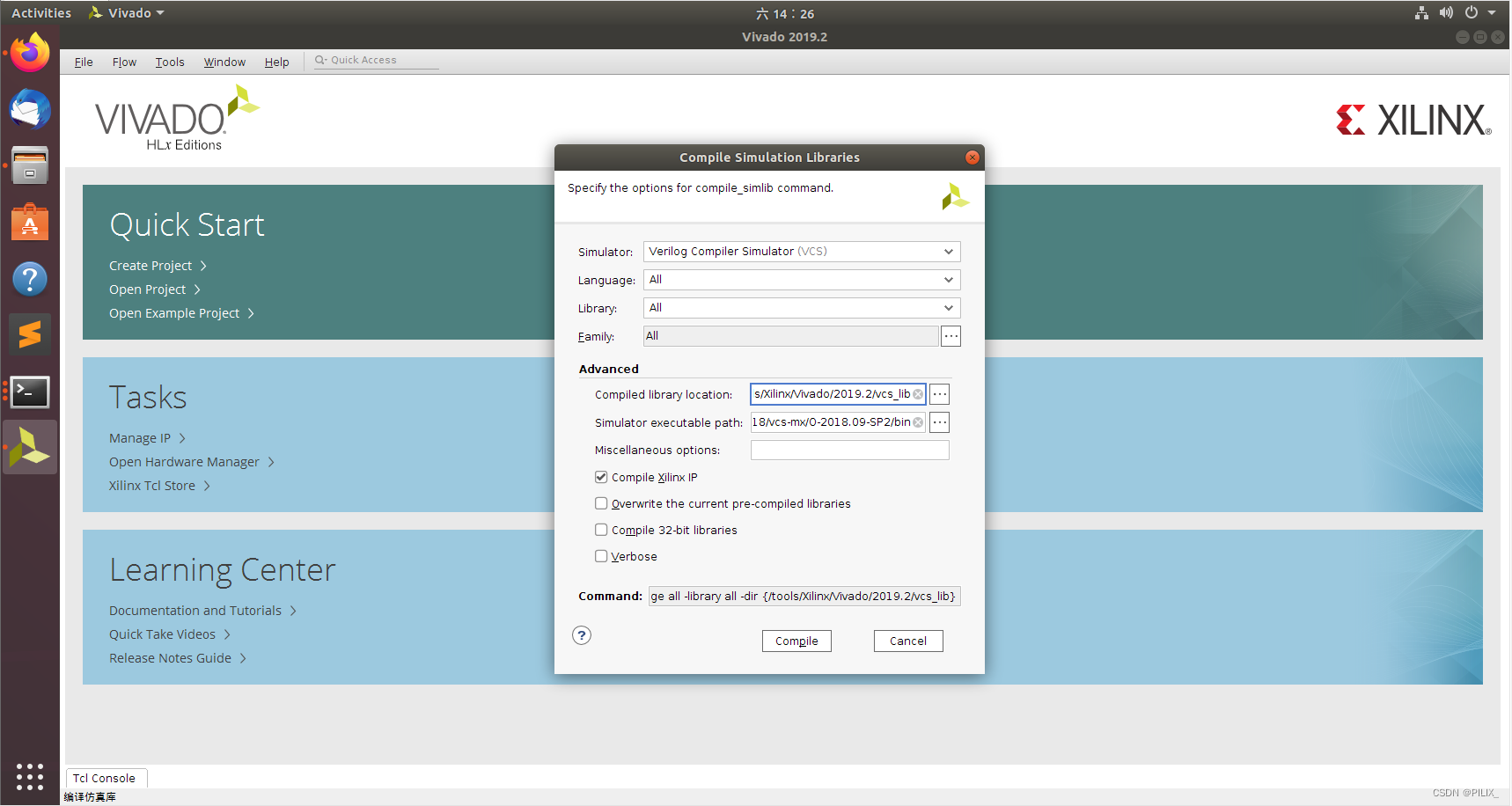

打开Vivado 2019.2后,点击Tools–>Compile Simulation Libraries,按下图所示配置:

其中:

Compiled library location :选择刚刚创建的vcs_lib路径,用于存放编译好的库文件

Simulator executable path:选择vcs-mx安装路径下的/bin,笔者此处为/usr/software/vcs2018/vcs-mx/O-2018.09-SP2/bin

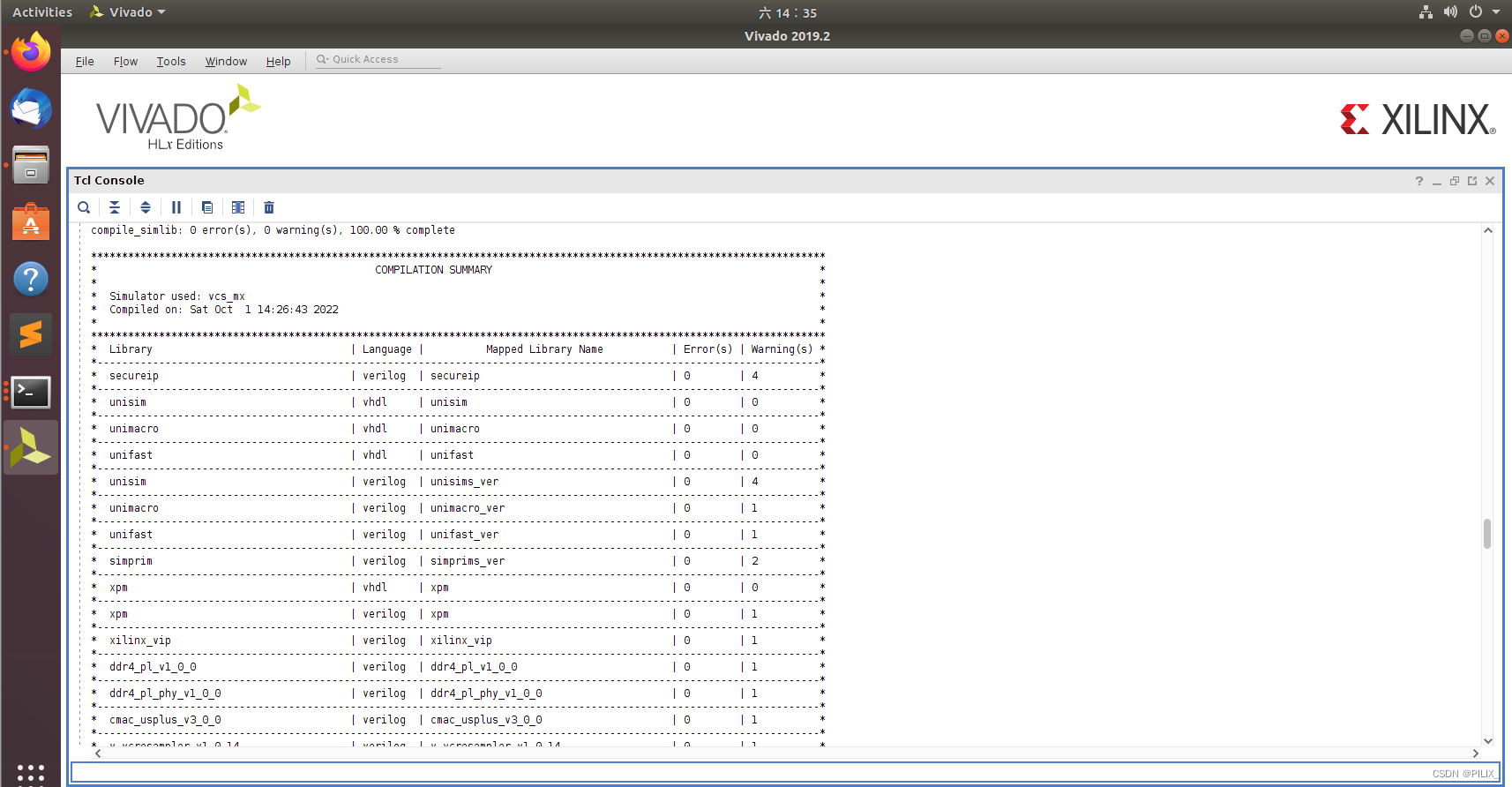

点击Compile开始编译,经过等待,出现以下信息,error为0即说明编译成功:

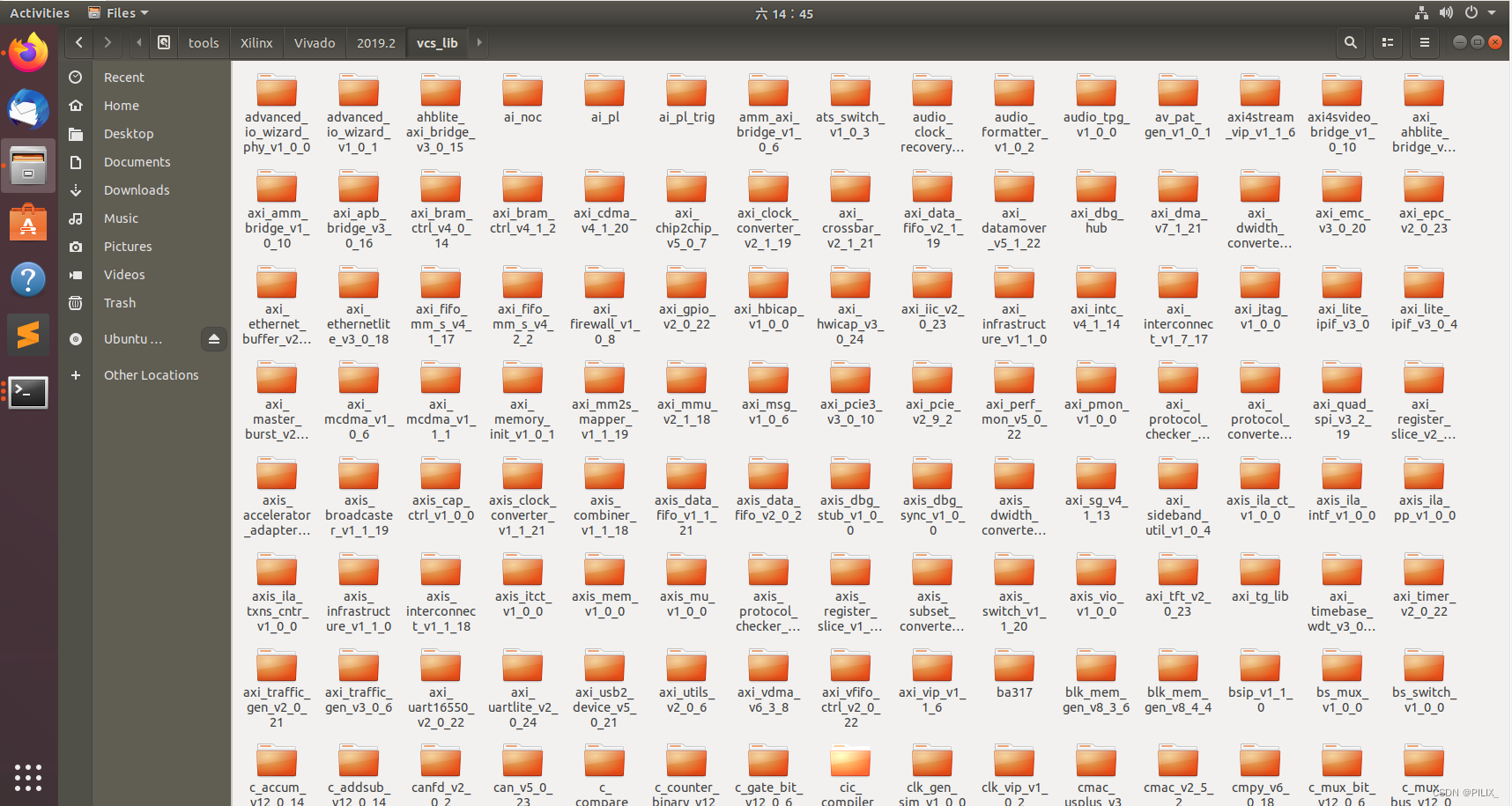

接着打开之前创建的vcs_lib目录就可以看到编译好的所有库文件

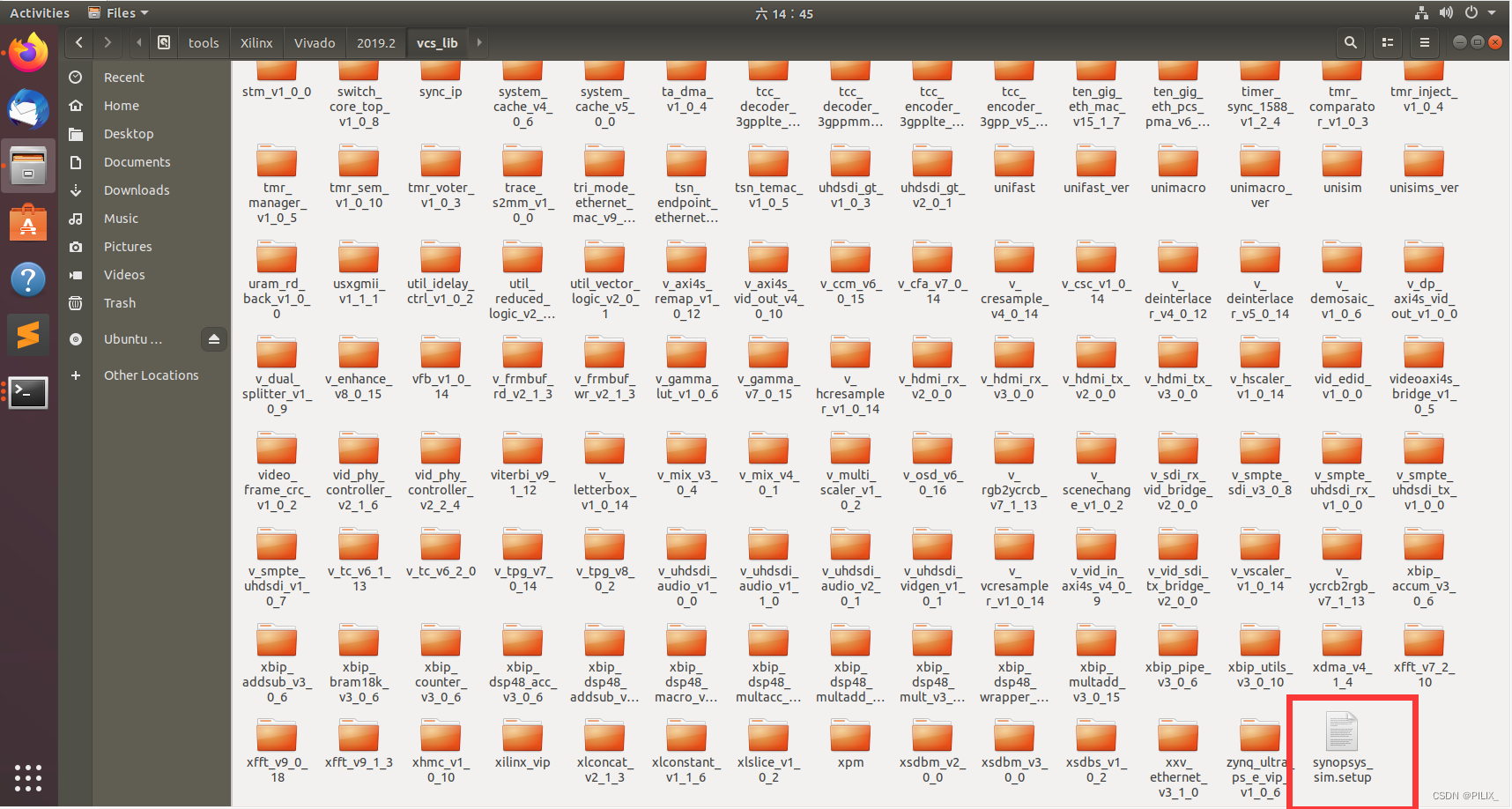

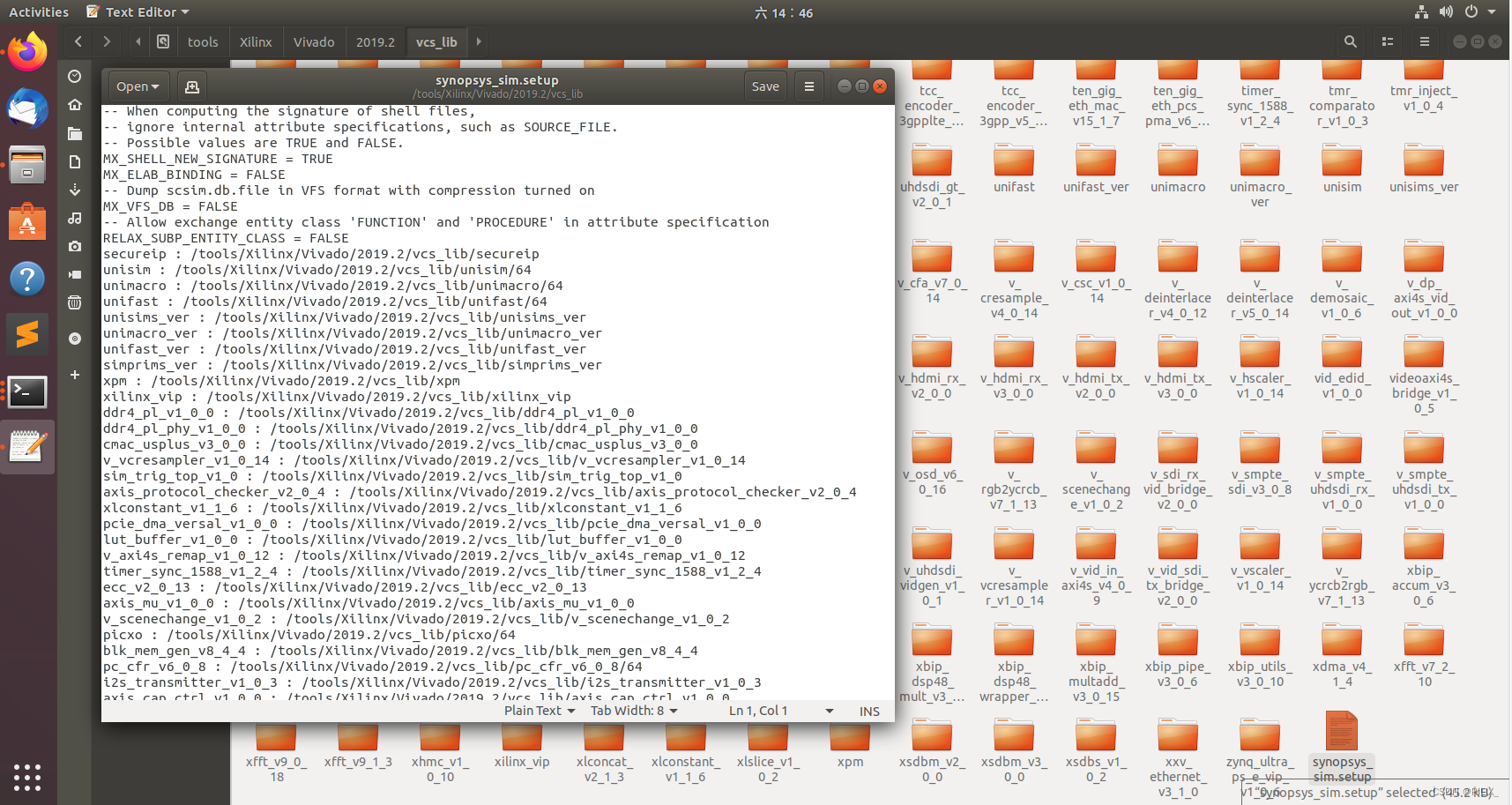

在这些生成的文件中,还包括一个非常重要的文件synopsys_sim.setup

这个文件非常重要,打开可以看到里面指明了Xilinx各个器件库的位置和绝对路径。vcs仿真时会调用这个文件来链接所有的器件库,可以说是我们实现独立仿真的”桥梁”。

使用Makefile实现仿真

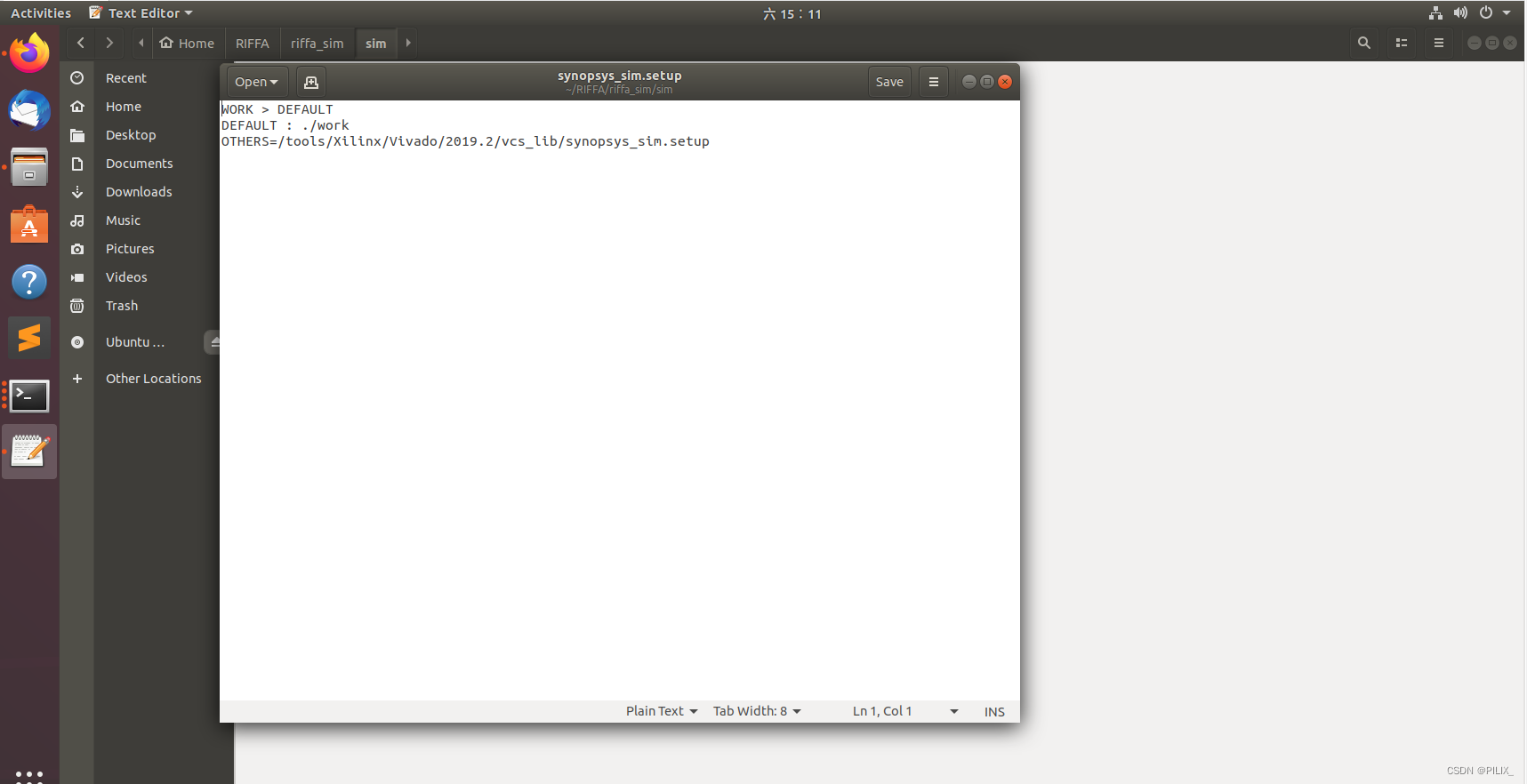

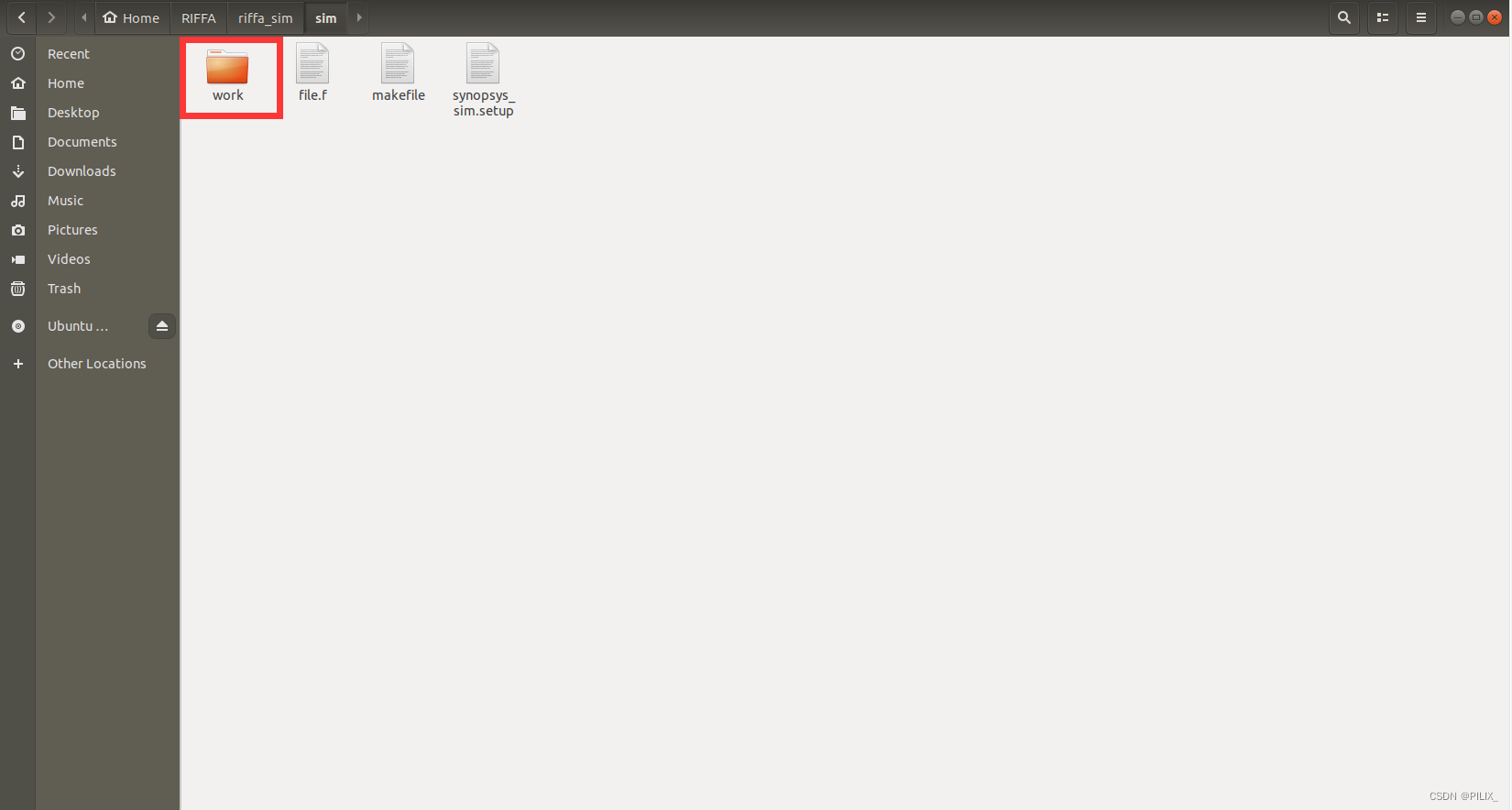

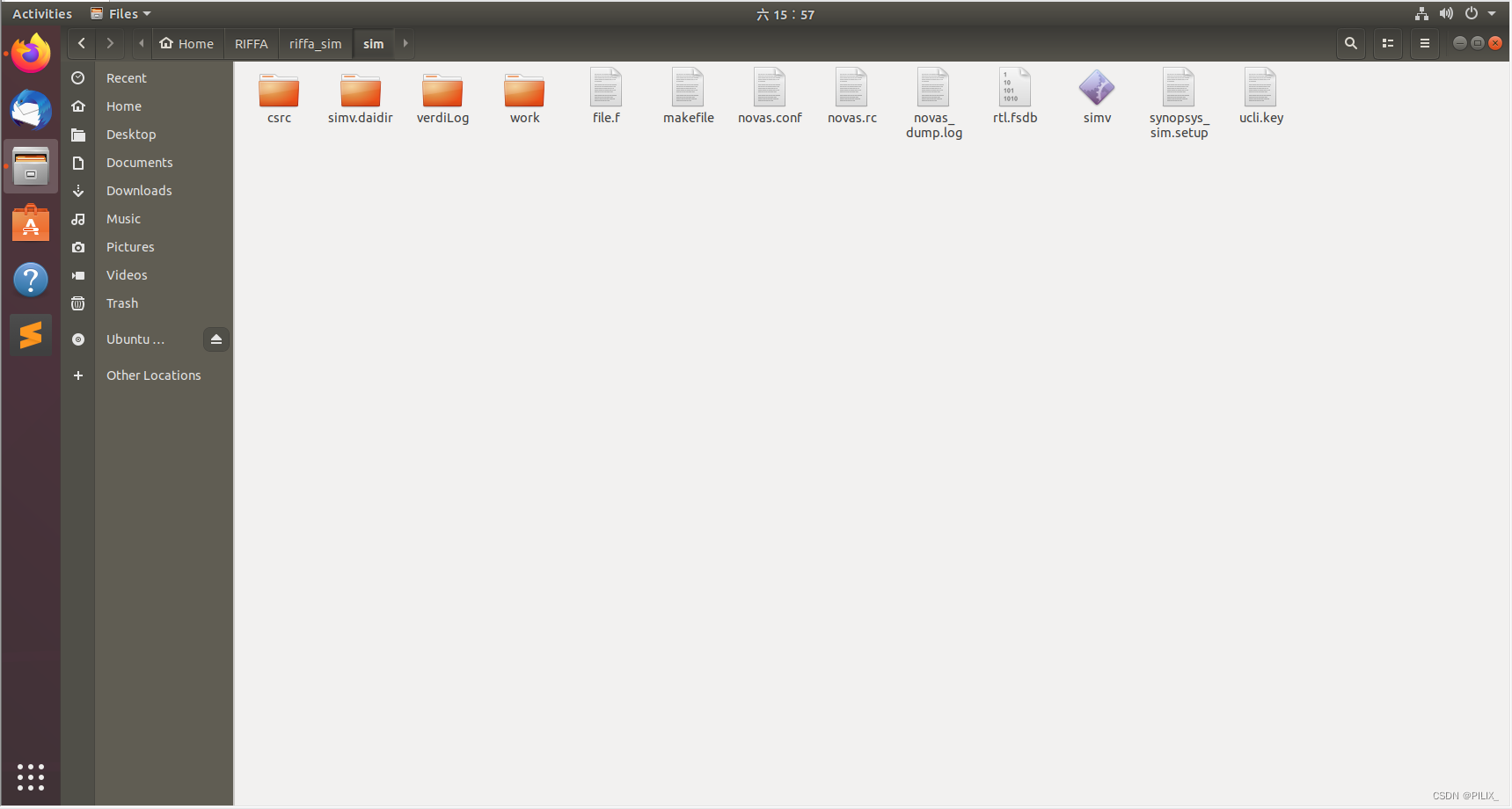

以一个工程为例来实现独立仿真,可将工程文件分为两个目录,分别是rtl/和sim/,其中rtl用来存放工程代码和testbench相关文件,此处不再赘述;sim/下主要要有三个文件,分别是makefile文件,file.f(或者其他格式,作用是存放要编译的代码文件名和路径),synopsys_sim.setup文件,用于链接到vcs_lib目录下的synopsys_sim.setup文件。

file.f

file.f文件的作用是用来存放要编译的代码文件(包括RTL文件和tb文件),使用file.f文件的好处在于如果工程需要大量的增加或减少编译的文件时,可以直接在该文件里修改,而不是每次都要重新编写makefile文件。

注意:绝对路径要修改为自己的代码文件路径

synopsys_sim.setup

自定义的setup文件里需要指明vcs_lib下setup文件的绝对路径,且要放在与makefile脚本同目录的路径下。vcs参考手册对synopsys_sim.setup文件搜索路径给出详细解释,可以看到vcs编译工具在运行时会依照先后顺序从以下3个路径查找synopsys_sim.setup文件。

所以需要将synopsys_sim.setup文件放置在与makefile相同的目录下,vcs工具会自动搜索并识别IP库的位置。

makefile

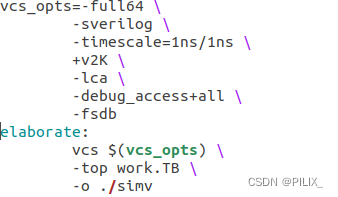

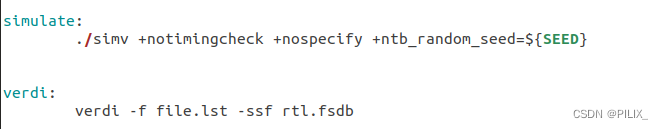

关于makefile的具体语法在这里不多介绍,可在网上自行搜索学习,大体可分为三部分:compile、 elaborate、simulate

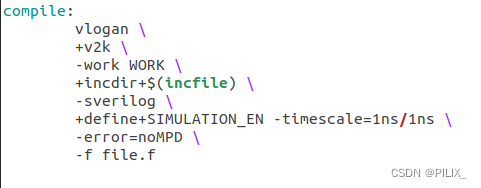

compile

compile是将硬件描述语言编译成库的过程,也正是这一过程中verilog文件可能会涉及到Xilinx的IP或者硬核,这时候就需要通过synopsys_sim.setup这个文件来指定IP库的位置。

执行如下指令即可实现compile过程:

make compile

可见生成了work文件夹。

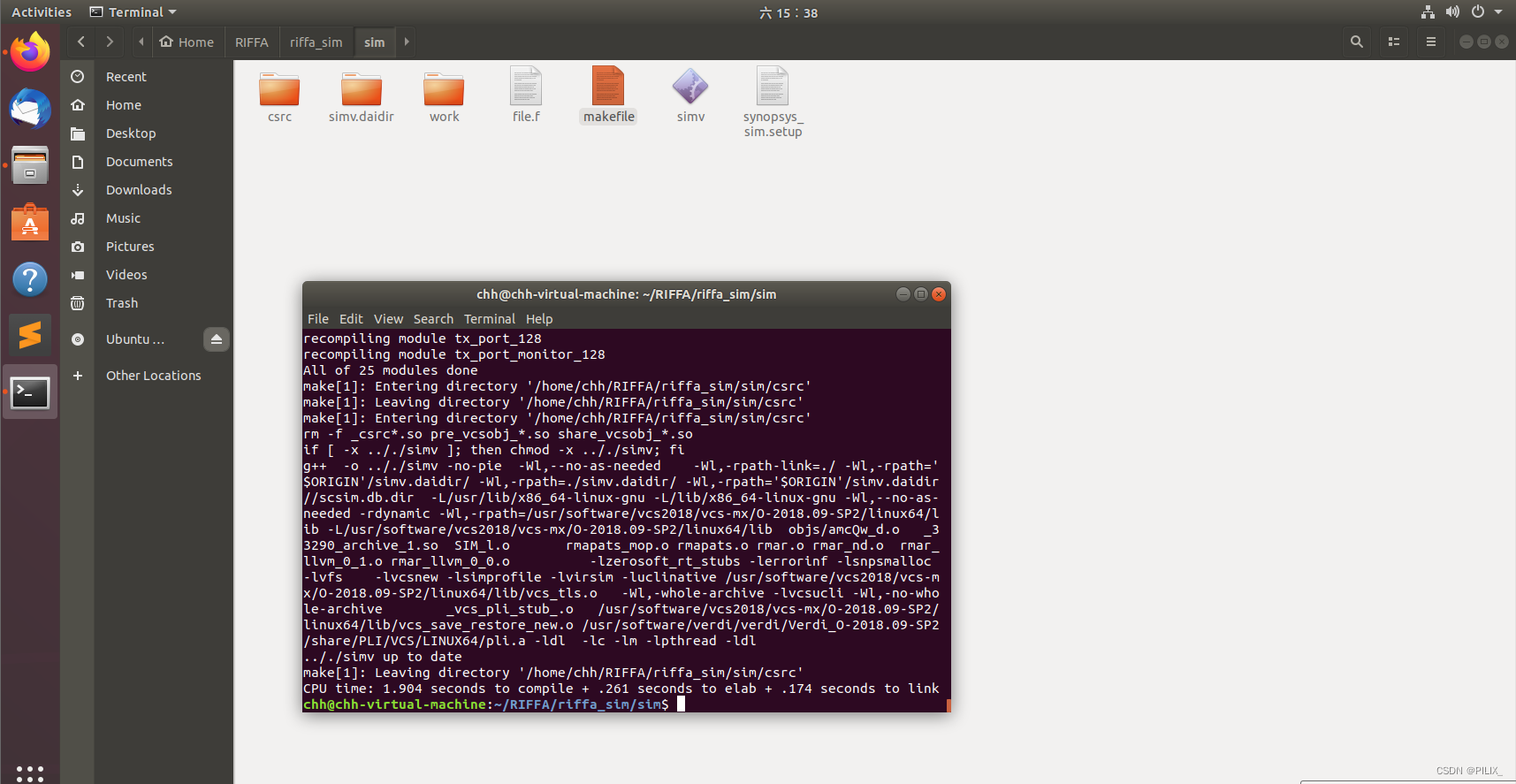

elaborate

这一步是将compile生成的库文件,以及可能用到的Xilinx IP的库文件,生成仿真的可执行文件(此处为simv文件)。具体的脚本如下,主要需要指定设计的bench顶层(此处为TB)和全局复位的glbl模块

同样执行如下指令:

make elaborate

可见生成了对应的simv可执行文件:

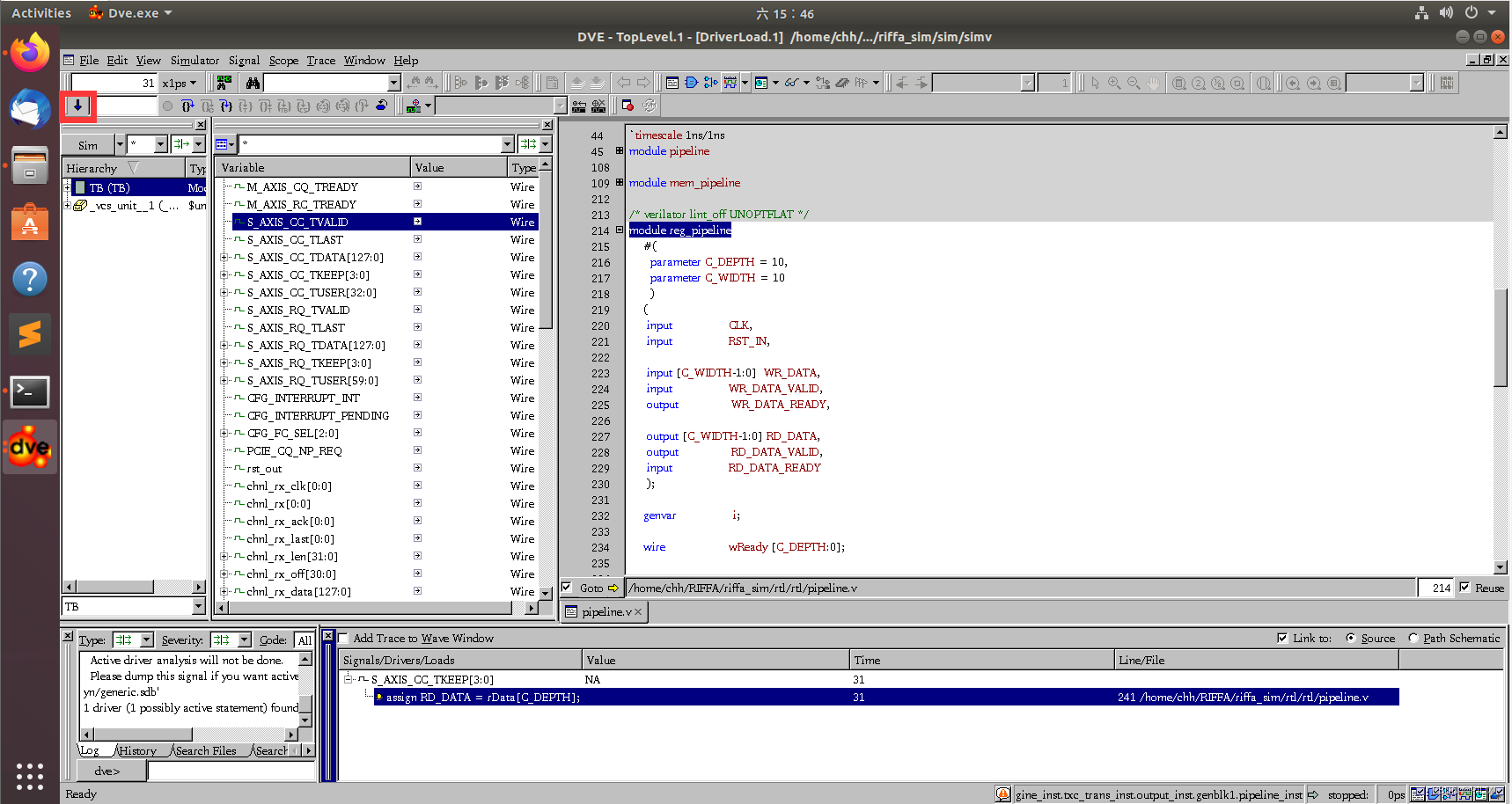

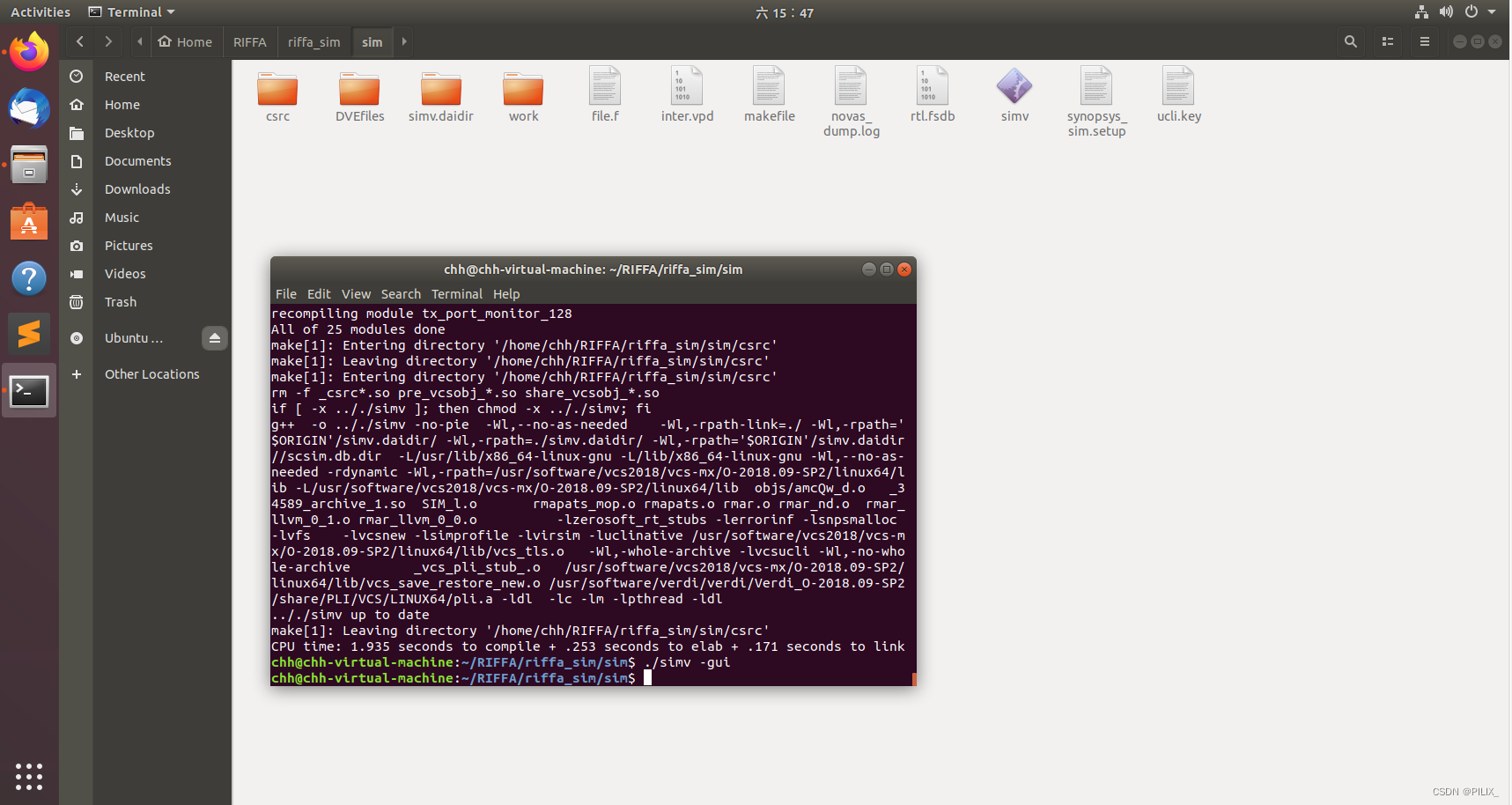

此时生成的simv文件即仿真的可执行文件,想要生成波形文件fsdb有两种方法,第一种是使用dve软件,通过以下指令:

./simv -gui

打开dve可视化界面,点击start键即可生成波形文件:

另一种方法就是在makefile中编写好simulate部分,直接生成fsdb文件,见下一部分

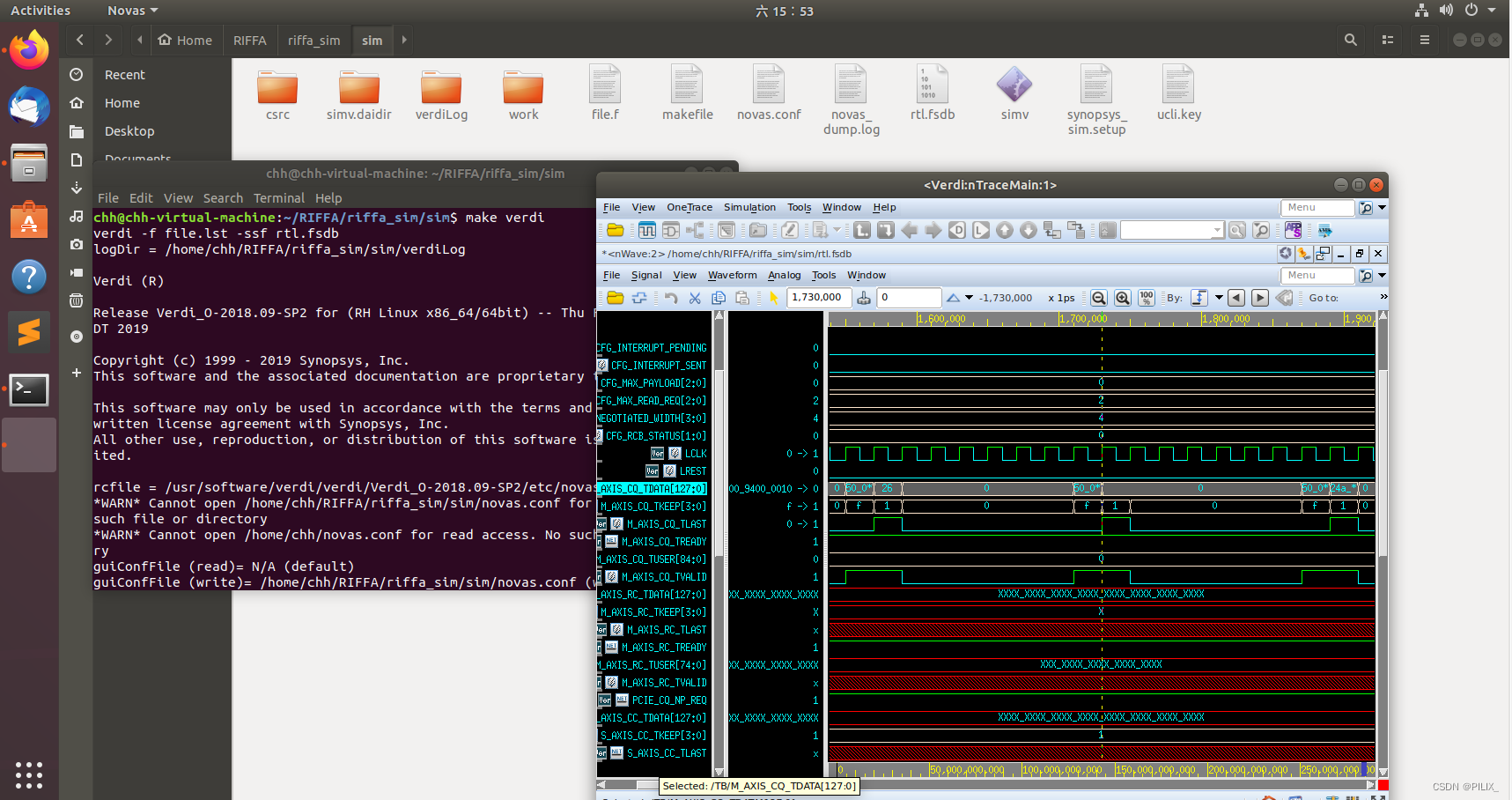

simulate+verdi

这一步就是执行上面生成的simv.o可执行文件,进行仿真。make simulate生成适用于verdi的fsdb文件:

接着再输入:make verdi 即可用verdi打开fsdb文件查看波形啦:

9037

9037

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?