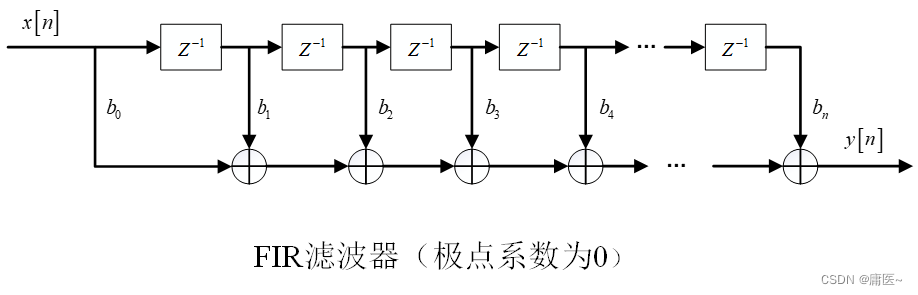

FIR IP核可配置为极点系数为0的横向滤波器结构

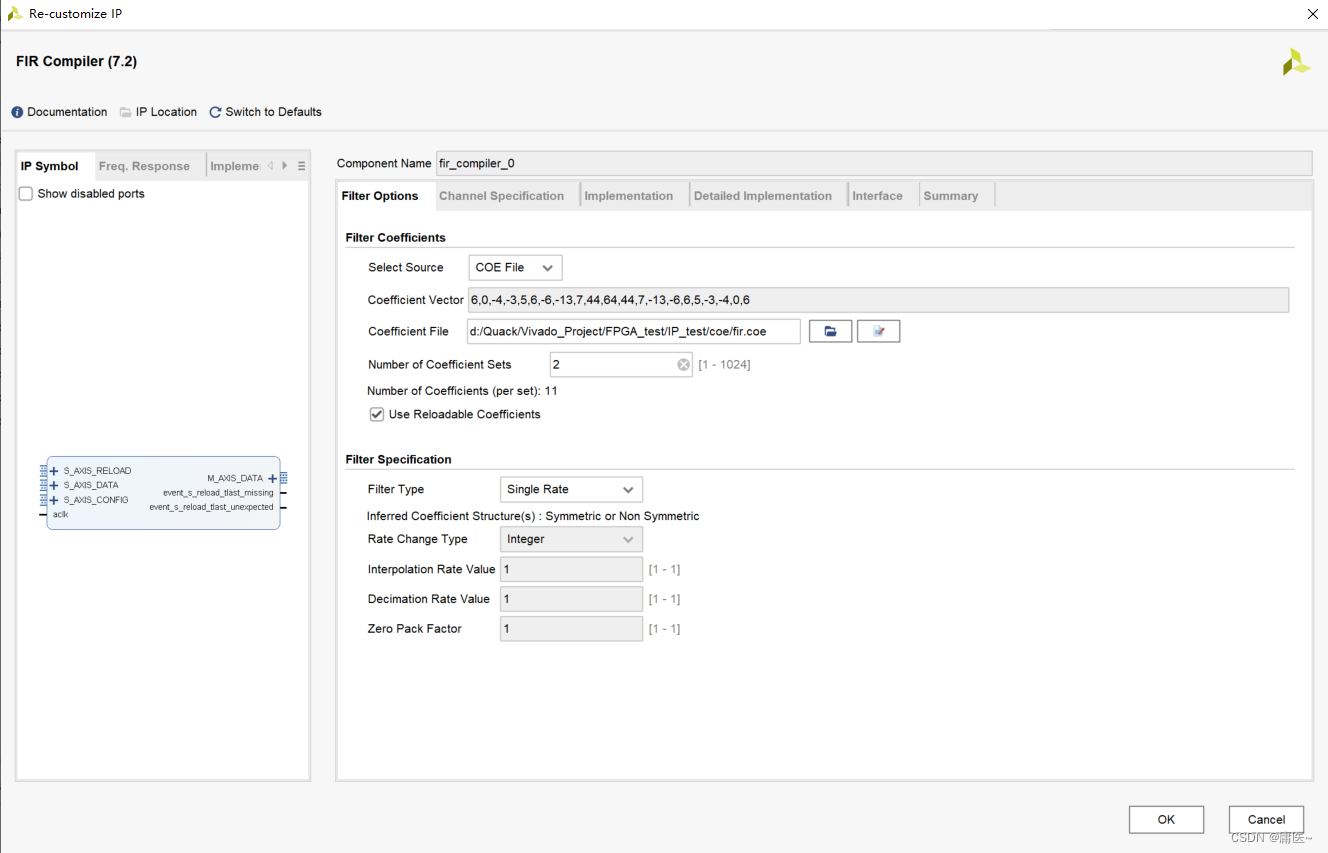

IP 核配置

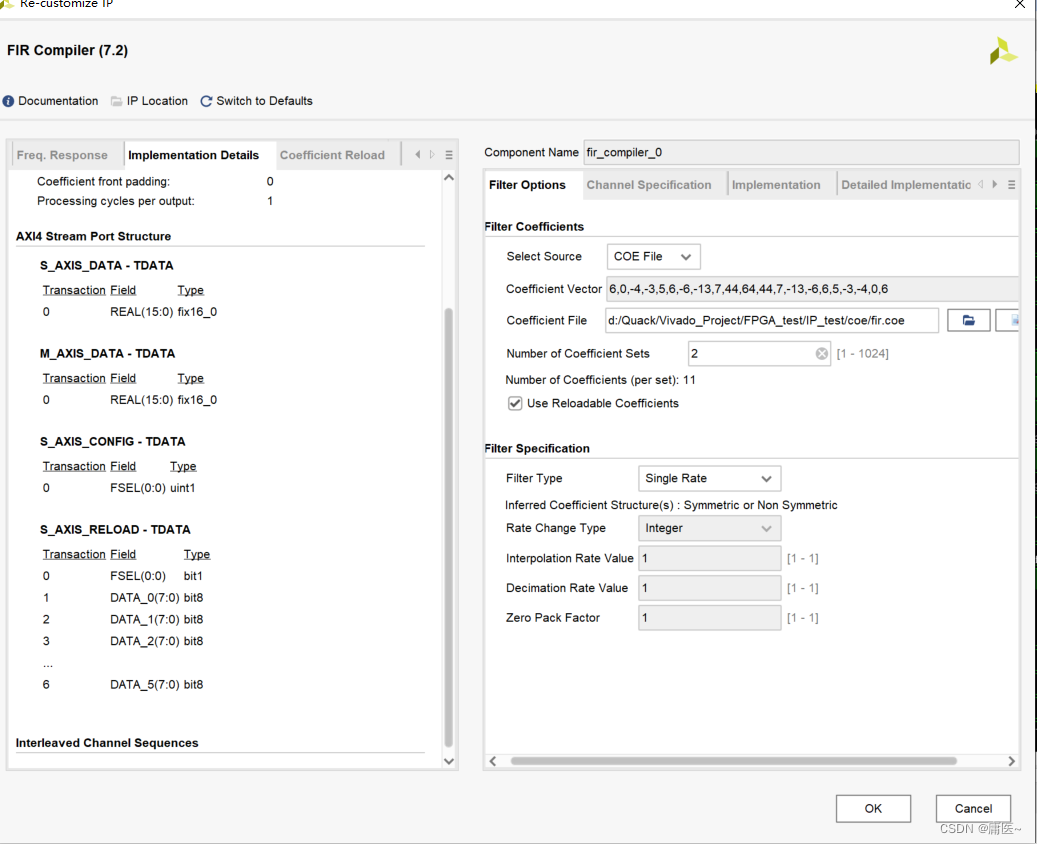

Filter coefficients

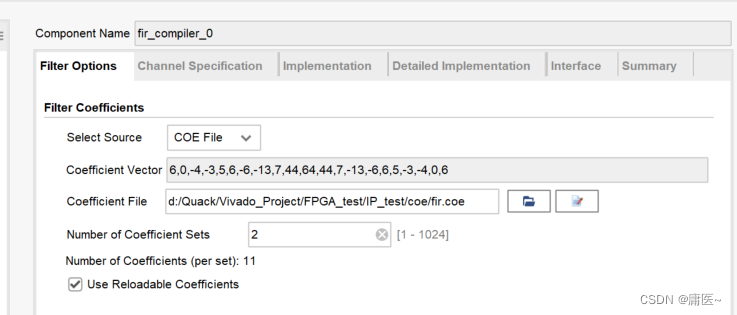

这里配置滤波器的类型,在Filter type中可将滤波器配置为单比率、抽取、插值滤波器。对于滤波器的系数,这里有两种方式,一种直接在IP中填写向量,另一中将select soure 选择为coe file,然后选择系数文件。coe文件可以包含多个滤波器系数,可在number of coefficient sets设置coe文件中包含的系数。

对于coe文件的生成可以参考以下的文章。

matlab产生FIR IP核(Xilinx)所需要的coe文件(系数文件) https://blog.csdn.net/QUACK_G/article/details/124132515?spm=1001.2014.3001.5502MATLAB中Filter Designer的用法

https://blog.csdn.net/QUACK_G/article/details/124132515?spm=1001.2014.3001.5502MATLAB中Filter Designer的用法 https://blog.csdn.net/QUACK_G/article/details/124433102?spm=1001.2014.3001.5502

https://blog.csdn.net/QUACK_G/article/details/124433102?spm=1001.2014.3001.5502

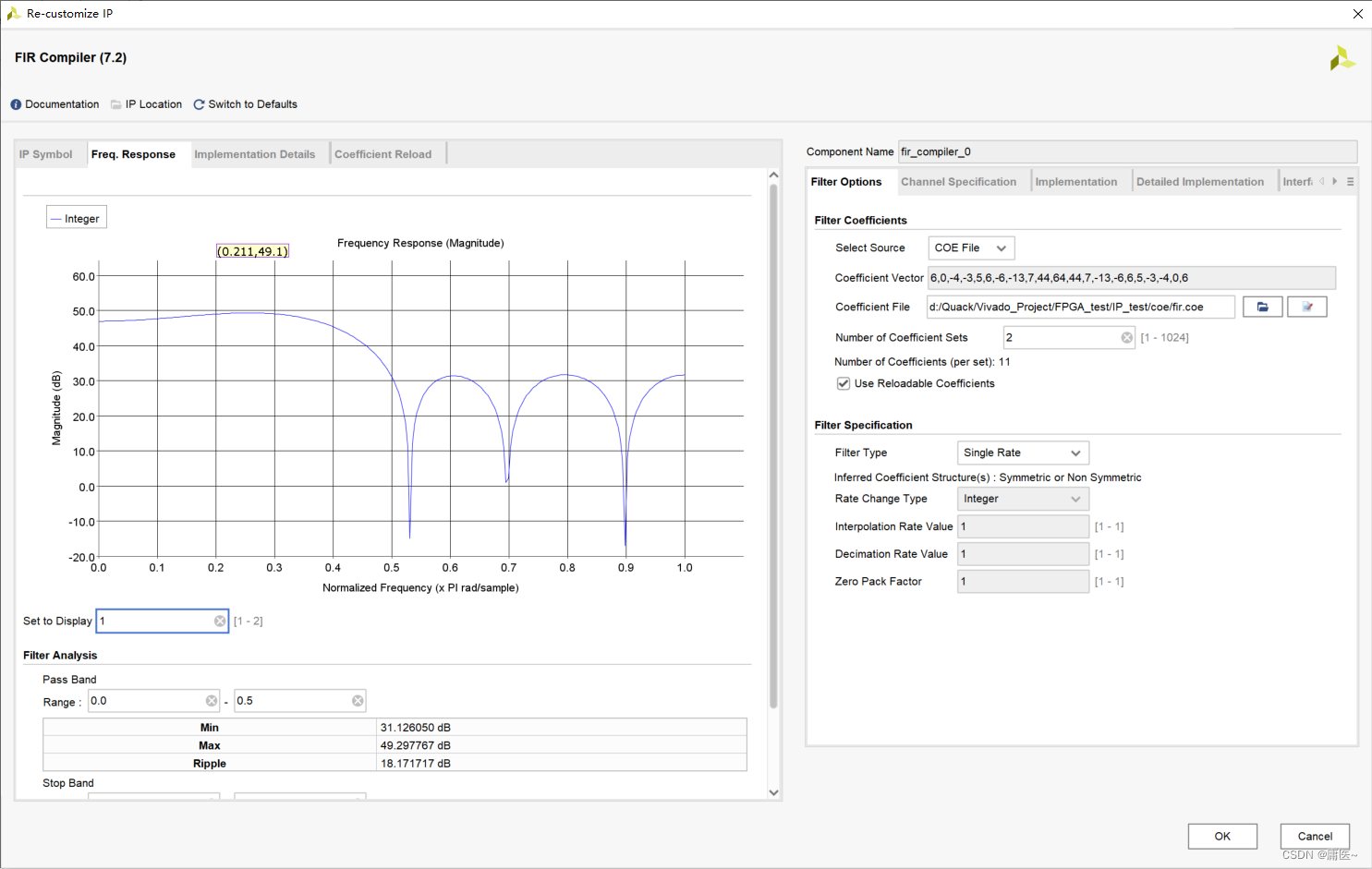

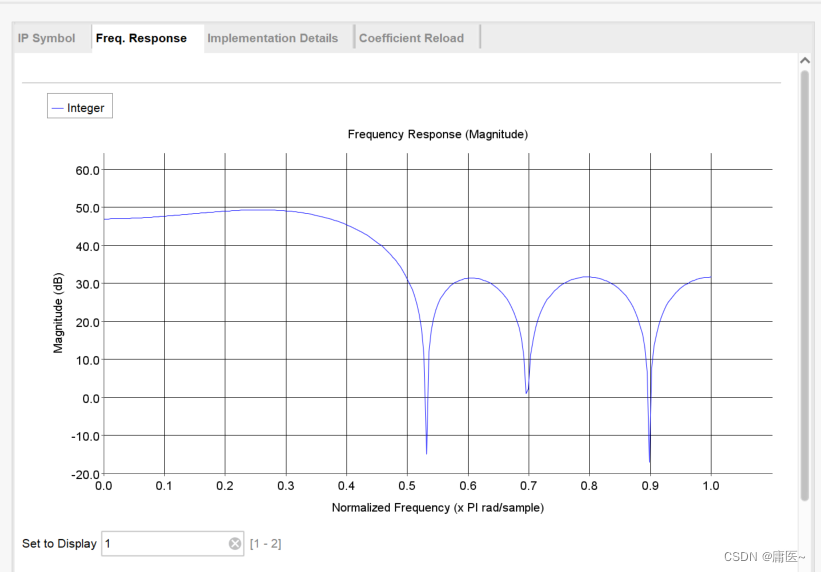

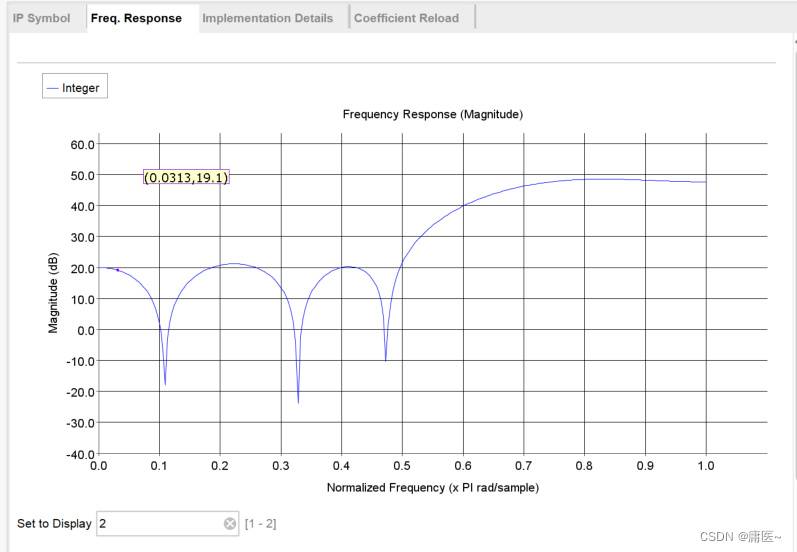

Freq.response

这里可查看滤波器的频响特性,如果系数文件中包含多个滤波器系数,可在Set to display选择不同的显示

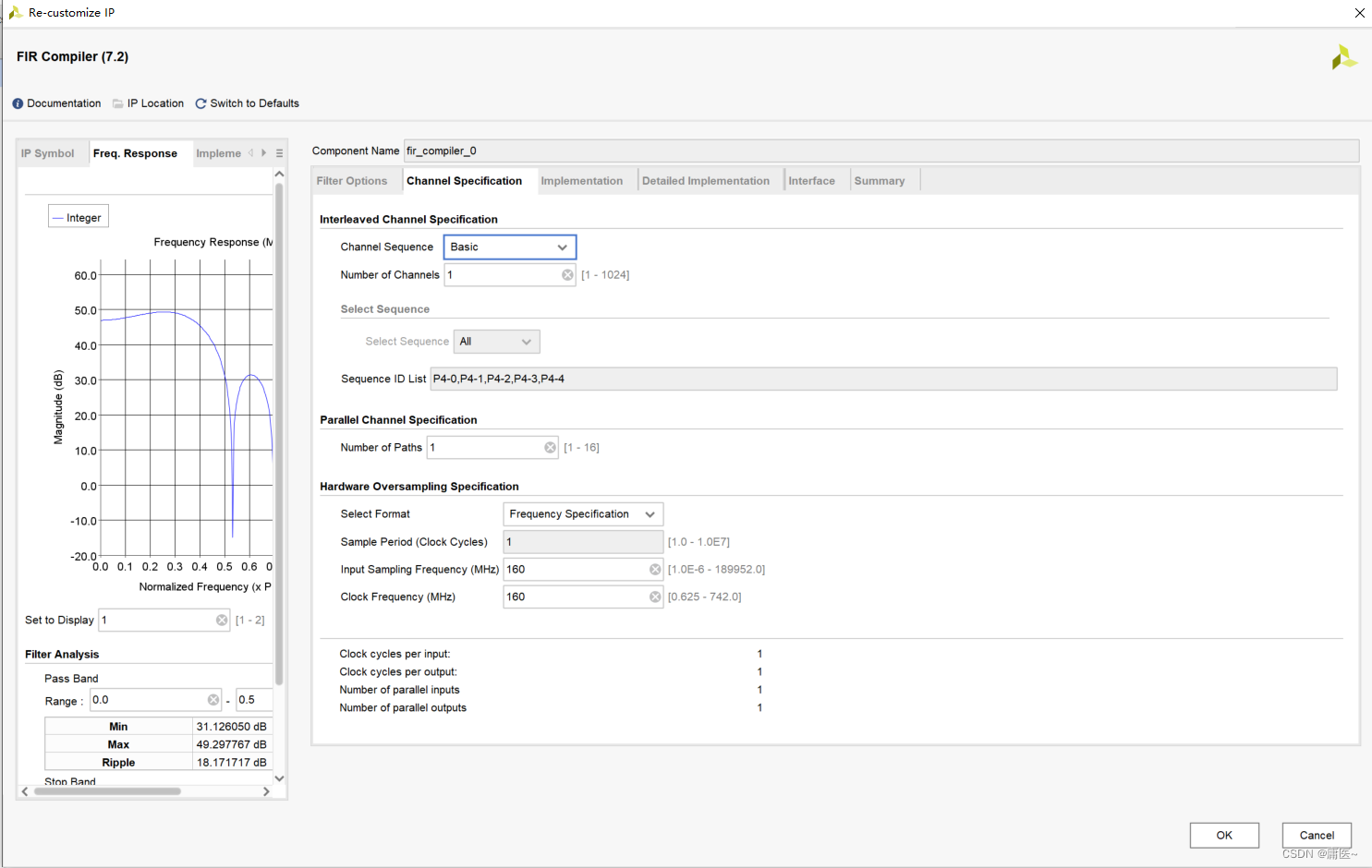

Channel specification

这里配置滤波器的通道数,IP核支持1-1024通道的滤波,下面选择采样率和时钟频率,通常来说二者的频率相同。

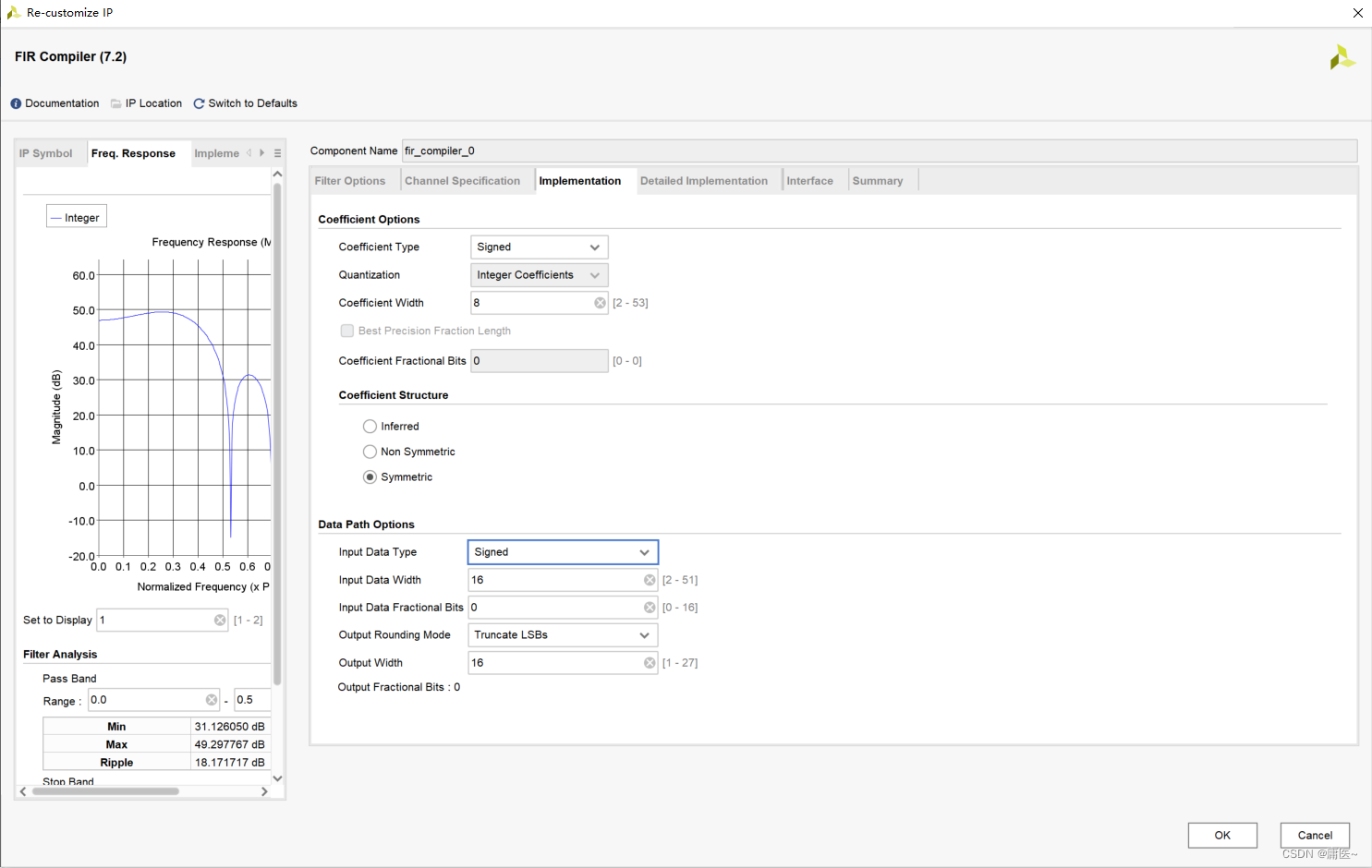

Implementation

这里选择数据和参数的位宽和滤波器结构,根据需要设置。其中symmetric为对称结构可减少资源。

其余配置可保持默认

参数重构

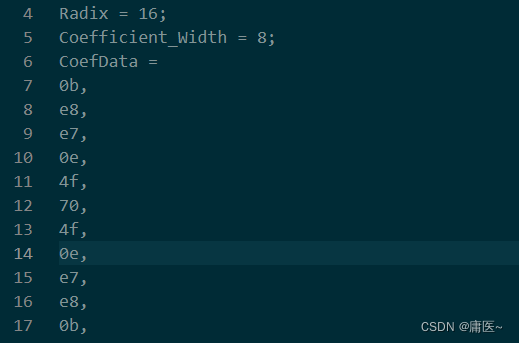

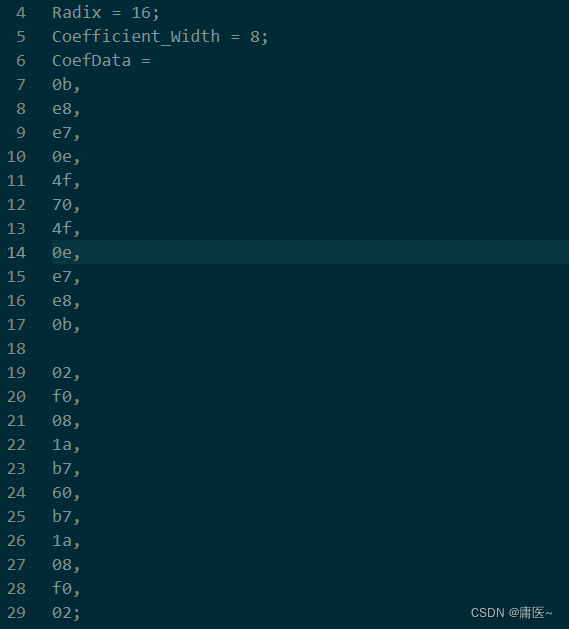

IP核提供了两种方式来重构滤波器的系数来改变滤波器的形式,一种在IP核中设置多种滤波器的形式,通过改变COE文件实现。通常来说一个coe文件中只包含一种滤波器结构的参数。

可以在当前的coe文件中,直接加入另一种结构形式的参数。这样coe文件中就有两套参数,然后在number of coefficient sets中填入数量。

这样就可以直接通过S_AIXS_CONFIG接口直接改变滤波器的形式。

另一种方式是通过reload 系数来实现滤波器形式的改变,通过勾选use reloadable coeffcients使IP核能够进行 重构参数,然后按照一定的时序进行将参数写入,进行改变滤波器结构。

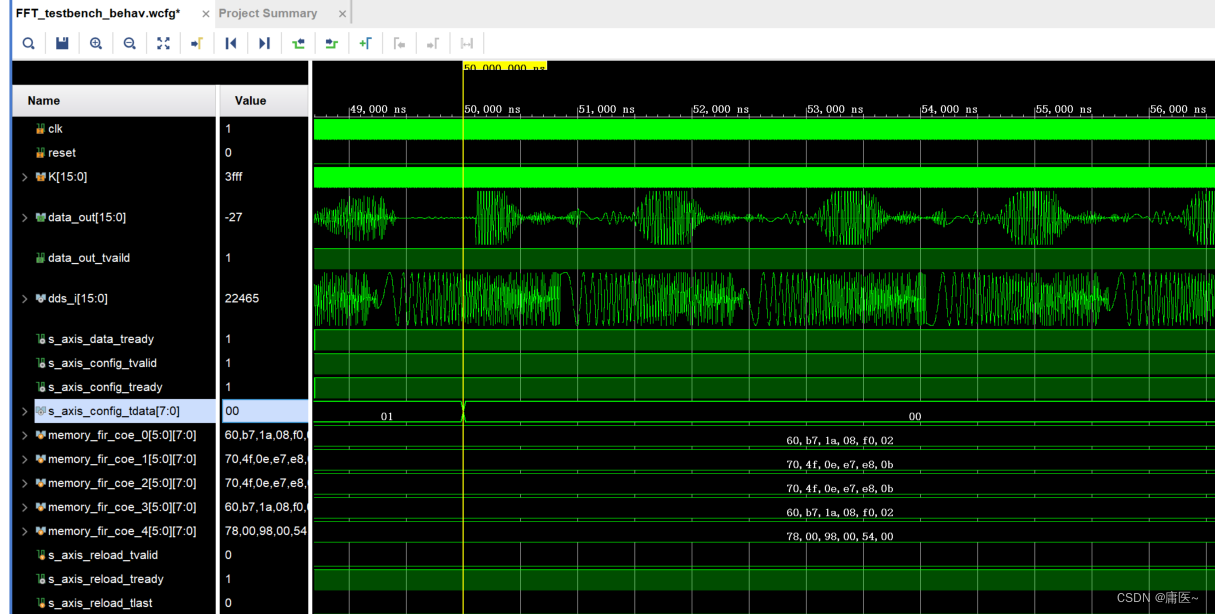

仿真验证

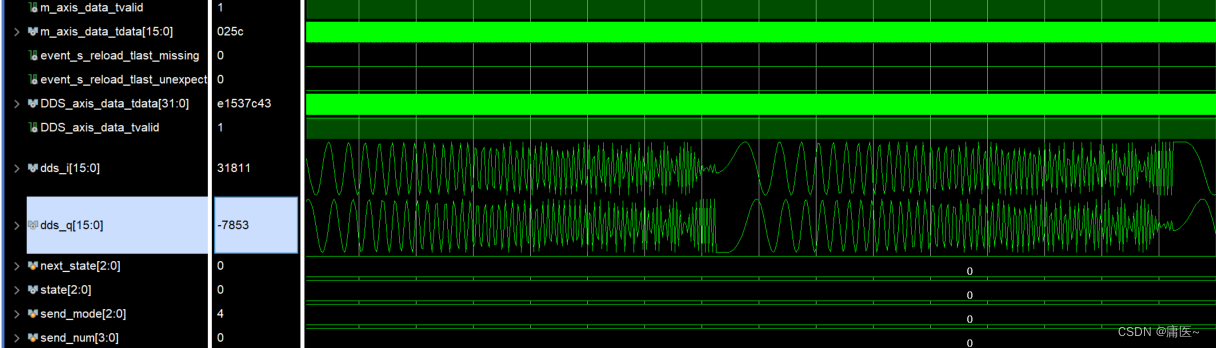

用DDSIP核产生0~80MHz的线性调频波,采样率为160M,

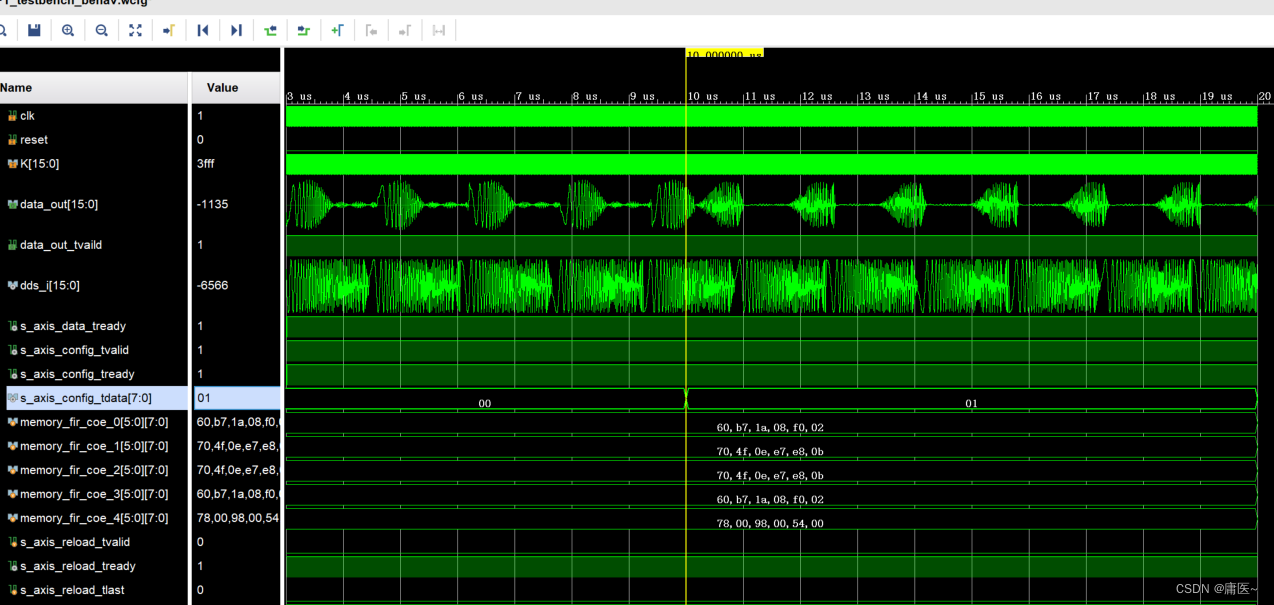

滤波器配置为参数重构模式,在coe文件中写入两套参数,mode0为低通滤波器,mode1为高通滤波器。这样可以通过config修改滤波器的形式。同时由于滤波器为参数重构模式,还可以通过reload参数改变滤波器的形式,将其配置为带通滤波器。

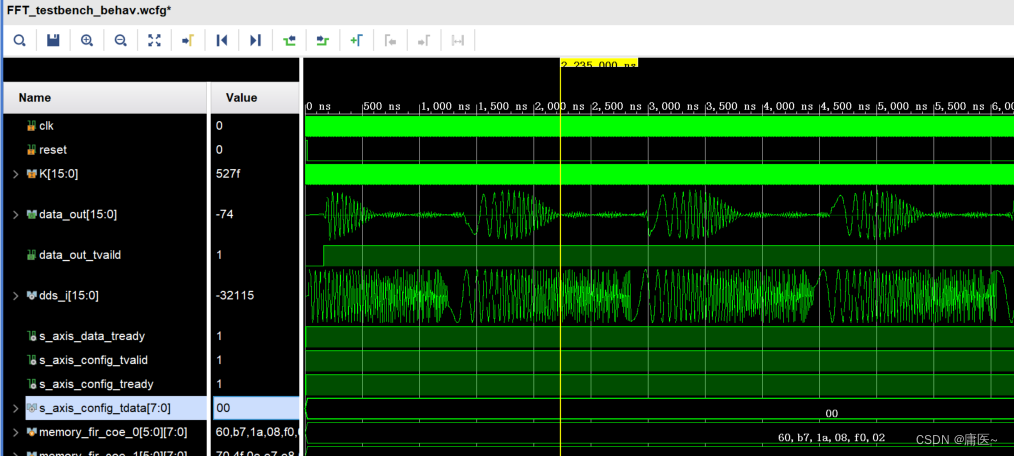

FIR滤波器的输入一个线性调频信号,config_data配置为mode0后,此时为低通滤波器模式,从波形中可以看到,高频的部分被滤波器滤掉。

config_data配置为mode1后,此时为高通滤波器模式,从波形中可以看到,低频的部分被滤波器滤掉。

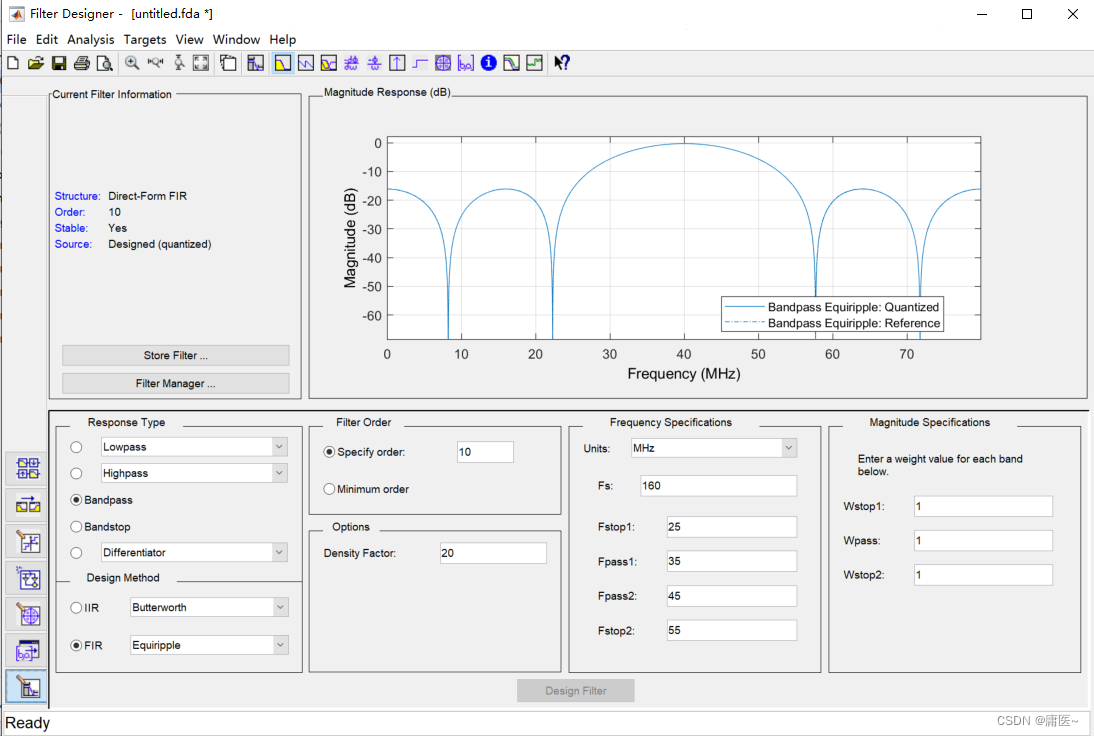

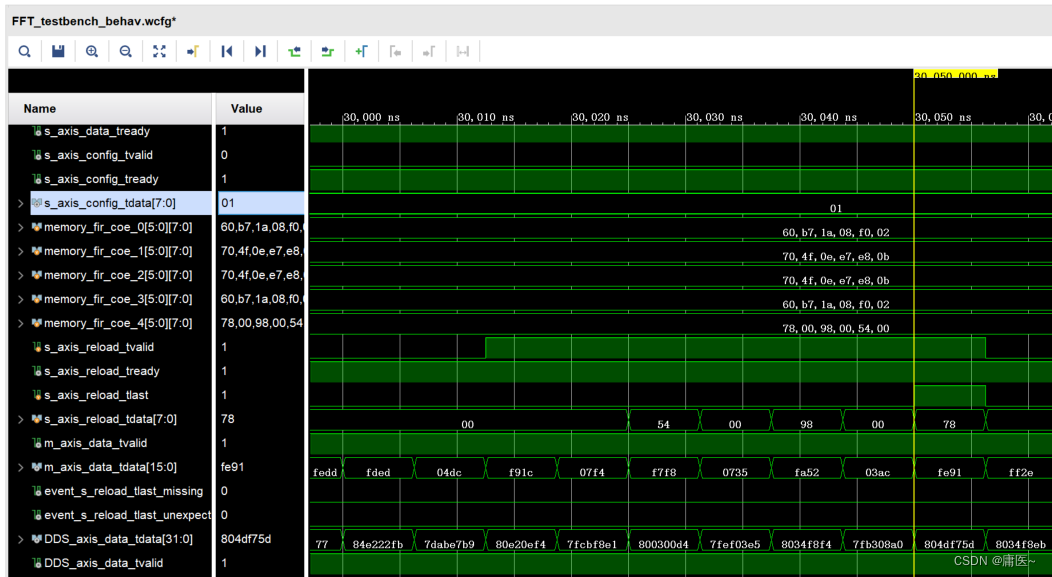

下面用reload重构系数来修改滤波器的类型,参数写入的顺序按照Inplementation Details中的S_AXIS_RELOASD-TDATA,由于在Number of coeffcient Sets设置了2种滤波器结构,因此reload参数的时候需要首先写入FSEL,选择改变哪一个config结构。

reload的时序如下所示:第一个时钟写入FSEL,后面6个时钟写入带通滤波器的系数。

进行参数重构后,mode0的滤波器类型就变为带通滤波器的形式。

2808

2808

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?