目录

前言

为了秋招,对时序分析做了一些准备,但主要是时序路径,建立时间裕量、保持时间裕量等基础性的东西,没能有一个规范的约束指导,是很难运用到实际当中的。

今天这篇博文就给出一个时序约束的大体指导,参考自:时序分析以及 AN 545: Design Guidelines and Timing Closure Techniques for HardCopy ASICs

当然前几天也写了一篇博客,是在Vivado中对时序总结进行分析的一篇科普文。

Vivado 随笔(5) Timing Summary 相关讨论(一)

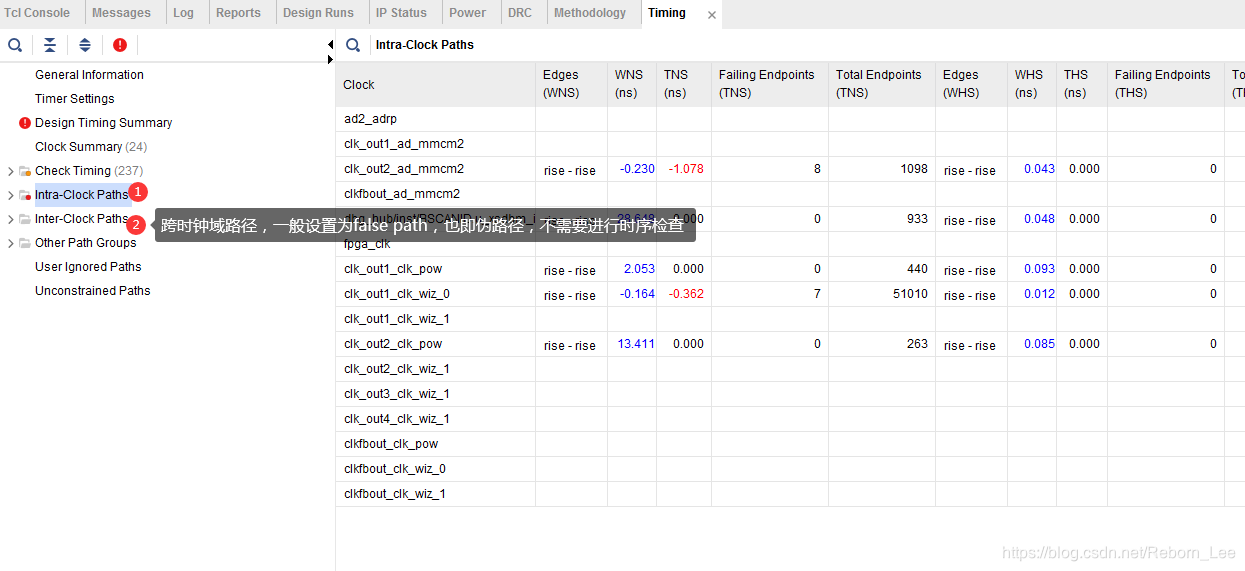

里面提到了TNS、WNS以及THS、WHS等概念,还有Intra-Clock path以及Inter-Clock path的概念。

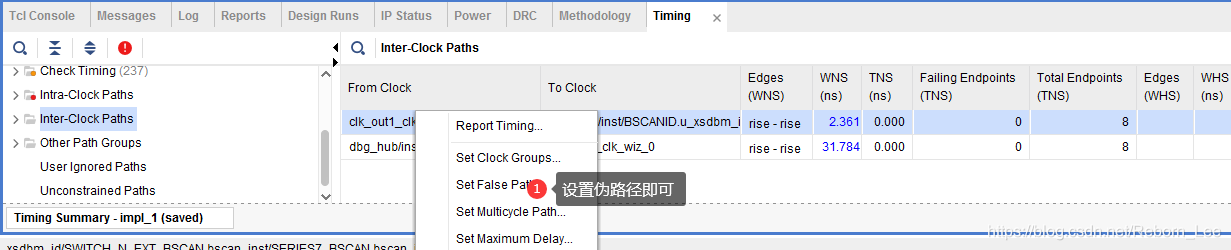

这些概念在时序分析中是必不可少的,WNS提示了最差负时序裕量,从它的正负关系可以看出设计中的时序满足与否,如果不满足,可进一步查看那些具体的路径不满足,属于Intra-Clock还是Inter-Clock path,对于Inter-Clock path,我们可以不进行时序分析,直接约束为伪路径,对于Intra-Clock path中的时序违规问题,我们是要实打实的去解决的地方。

Vivado的约束文件是XDC文件,它包含的范围大于SDC,因此,当然可以用SDC的那一套命令来约束时序。

Intra-Clock&Inter-Clock Paths

在正式进行约束之前,还是先把这些概念提出来,作为预备知识。

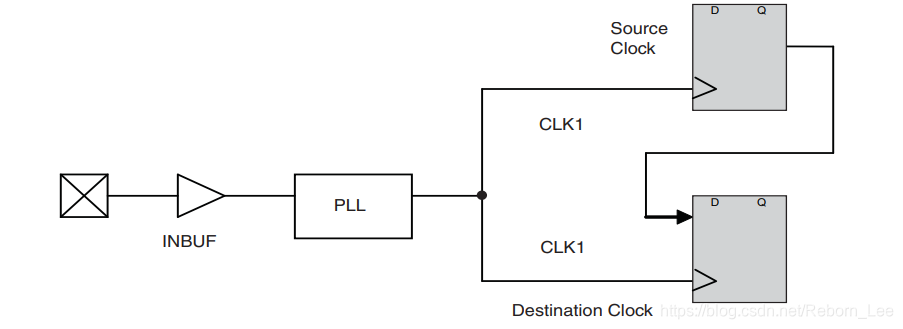

当源时钟和目的时钟来自于同一个时钟信号,这个时钟信号可以是PLL或者MMCM产生的时钟,可以是I/O clock pins等。

总之,这种路径是不存在跨时钟域问题,如下图:

数据在这种路径下传输,属于Intra-Clock Transfer。

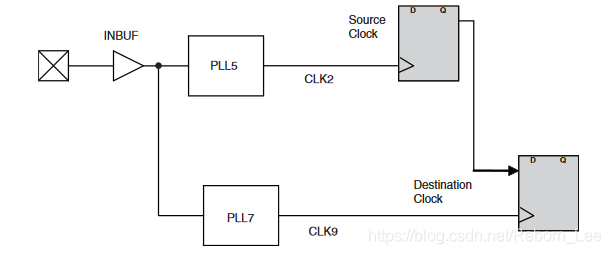

与之相对的是Inter-clock Paths,很好理解,源时钟和目的时钟来自于不同的时钟域,如下图:

在这种路径下的信号传输,属于跨时钟域传输,也叫Inter-Clock Transfer。

时序约束

主时钟约束

这里就正式进入时序约束的大门了,在FPGA时序约束中,我们可以在综合之后添加,也可以在实现之后添加。时钟是时序电路设计的心脏,因此时序约束中的第一步我们需要对我们设计中需要的时钟进行周期约束,对于时钟的约束又分为主时钟约束和再生时钟约束。

主时钟通常有两种情形:

一种是时钟由外部时钟源提供,通过时钟引脚进入FPGA,该时钟引脚绑定的时钟为主时钟:

另一种是高速收发器(GT)的时钟RXOUTCLK或TXOUTCLK。

对于7系列FPGA,需要对GT的这两个时钟手工约束;

对于UltraScale FPGA,只需对GT的输入时钟约束即可,Vivado会自动对这两个时钟约束。

可以通过如下两个Tcl命令来查看未约束的主时钟:

//确定主时钟

report_clock_networks -name mynetwork

//或者

check_timing -override_defaults no_clock

对于主时钟的约束,使用Tcl命令:

create_clock -name <name> -period <period> -waveform {<rise_time> <fall_time>} [get_ports <input_port>]| 参数 | 含义 |

|---|---|

| -name | 时钟名称 |

| -period | 时钟周期,单位为ns |

| -waveform | 波形参数,第一个参数为时钟的第一个上升沿时刻,第二个参数为时钟的第一个下降沿时刻 |

| -add | 在同一时刻源上定义多个时钟时使用 |

例如:

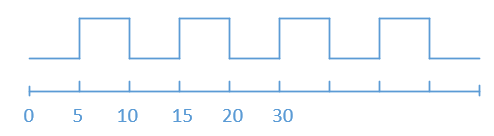

create_clock -period 10 -name clka -waveform {5 10} [get_ports clka]

当然上面只是一个例子,它约束的主时钟波形图是这样的:

如果不加属性-waveform,默认高电平位于0时刻。

这条约束主时钟的Tcl命令可以写在XDC或者SDC约束文件中,也可以直接在Tcl console中(针对Vivado)输入,运行后,Vivado会自动把这条约束添加到XDC文件中。

衍生时钟约束

衍生时钟可以是PLL或者MMCM等时钟管理资源产生的时钟,也可以是经过逻辑分析得到,例如设计一个分频器得到的时钟等。

衍生时钟又分两种情况:

- Vivado自动推导的衍生时钟

- 用户自定义的衍生时钟

首先来看第一种,如果使用PLL或者MMCM,则Vivado会自动推导出一个约束。

也就是说,不需要我们对PLL产生的时钟进行约束了。

自动推导的好处在于当MMCM/PLL/BUFR的配置改变而影响到输出时钟的频率和相位时,用户无需改写约束,Vivado仍然可以自动推导出正确的频率/相位信息。劣势在于,用户并不清楚自动推导出的衍生钟的名字,当设计层次改变时,衍生钟的名字也有可能改变。但由于该衍生时钟的约束并非我们自定义的,因此可能会没有关注到它名字的改变,当我们使用者这些衍生时钟进行别的约束时,就会出现错误。

对衍生时钟进行约束的Tcl命令为:create_generated_clock

其格式为:

create_generated_clock -name <generated_clock_name> \

-source <master_clock_source_pin_or_port> \

-multiply_by <mult_factor> \

-divide_by <div_factor> \

-master_clock <master_clk> \

<pin_or_port>参数 | 含义 :

-name | 时钟名称 -source | 产生该时钟的源时钟 -multiply_by | 源时钟的多少倍频 -divide_by | 源时钟的多少分频

从名字就能看出来,这个是约束我们在FPGA内部产生的衍生时钟, 所以参数在中有个-source,就是指定这个时钟是从哪里来的,这个时钟叫做master clock,是指上级时钟,区别于primary clock。 它可以是我们上面讲的primary clock,也可以是其他的衍生时钟。该命令不是设定周期或波形,而是描述时钟电路如何对上级时钟进行转换。这种转换可以是下面的关系:

- 简单的频率分频

- 简单的频率倍频

- 频率倍频与分频的组合,获得一个非整数的比例,通常由MMCM或PLL完成

- 相移或波形反相

- 占空比改变

- 上述所有关系的组合

延迟约束

对于这种约束使用的Tcl命令为:

set_input_delay

set_output_delay

这里暂时不做过多的说明,想要了解请看:

等理解深刻了在回来。

伪路径约束

这里简单说来,要对两种路径添加伪路径约束,一种是Inter-Clock Paths中的路径添加伪路径约束即可,另外还需要对异步复位添加伪路径约束。

具体说来:

异步复位呢?

set_false_path -from [get_ports rst_pin]多周期路径约束

这里也不多说,见链接:

写在最后

在今年的秋招一开始,我就建立了一个微信群,在CSDN发布了一条博文,召集全国各地的同行朋友们共同加入,共同讨论秋招求职笔试,面试经验,目前已经有300多人加入,各位才华横溢,让我大开眼界。

到今天11月份,从西北地区最早结束到其他各地陆续结束,但是我们曾开玩笑说,本群继续召集下一届同行,作为先行者的我们也会对你们给予应有的帮助,欢迎加入,到你们晒工资的时候,会不会再次把我们倒挂呢?拭目以待。

由于人数较多,所以加我的时候务必备注:CSDN+地区或学校+职位(意向职位)+昵称。

我的微信号是:ljs521615

888

888

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?