第3节 模块结构

3.1 模块介绍

模块( module)是 Verilog 的基本描述单位, 是用于描述某个设计的功能或结构及与其他模块通信的外部端口。

模块在概念上可等同一个器件,就如调用通用器件(与门、三态门等)或通用宏单元(计数器、ALU、 CPU)等。因此,一个模块可在另一个模块中调用,一个电路设计可由多个模块组合而成。一个模块的设计只是一个系统设计中的某个层次设计,模块设计可采用多种建模方式。

Verilog 的基本设计单元是―模块‖。采用模块化的设计使系统看起来更有条理也便于仿真和测试,因此整个项目的设计思想就是模块套模块,自顶向下依次展开。 在一个工程的设计里,每个模块实现特定的功能,模块间可进行层次的嵌套。对大型的数字电路进行设计时,可以将其分割成大小不一的小模块,每个小模块实现特定的功能,最后通过由顶层模块调用子模块的方式来实现整体功能,这就是 Top-Down 的设计思想。 本书主要以 Verilog 硬件描述语言为主,模块是 Verilog 的基本描述单位,用于描述每个设计的功能和结构,以及其他模块通信的外部接口。

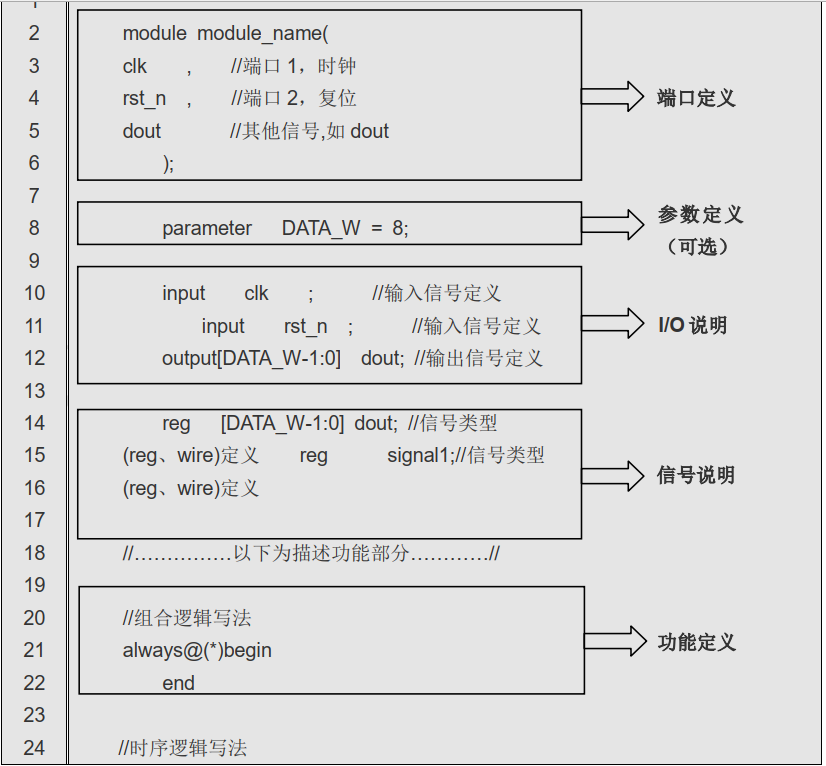

模块有五个主要部分:端口定义、参数定义(可选)、 I/O 说明、内部信号声明、功能定义。模块总是以关键词 module 开始,以关键词 endmodule 结尾。它的一般语法结构如下所示:

3.2 模块名和端口定义

第 1 至 5 行声明了模块的名字和输入输出口。其格式如下:module 模块名(端口 1,端口 2,端口 3, ……);其中模块是以 module 开始,以 endmodule 结束。模块名是模块唯一的标识符, 一般建议模块名尽量用能够描述其功能的名字来命名,并且模块名和文件名相同。

模块的端口表示的是模块的输入和输出口名,也是其与其他模块联系端口的标识。

3.3 参数定义

第 8 行参数定义是将常量用符号代替以增加代码可读性和可修改性。这是一个可选择的语句,用不到的情况下可以省略,参数定义一般格式如下:

parameter DATA_W = x;

3.4 接口定义

第 9 至 12 行是 I/O(输入/输出)说明,模块的端口可以是输入端口、输出端口或双向端口。其说明格式如下。

输入端口: input [信号位宽-1 : 0] 端口名 1;

input [信号位宽-1 : 0] 端口名 2;

……;

输出端口:output [信号位宽-1 : 0] 端口名 1;

output [信号位宽-1 : 0] 端口名 2;

……;

双向端口: inout [信号位宽-1 : 0] 端口名 1;

inout [信号位宽-1 : 0] 端口名 2;

……;

3.5 信号类型

第 14 至 17 行定义了信号的类型。 这些信号是在模块内使用到的信号,并且与端口有关的 wire和 reg 类型变量(即线网型与寄存器型)。 其声明方式如下:

reg [width-1 : 0] R 变量 1, R 变量 2 ……;

wire [width-1 : 0] W 变量 1, W 变量 2……;

如果没有定义信号类型,默认是 wire 型,并且信号位宽为 1。

3.6 功能描述

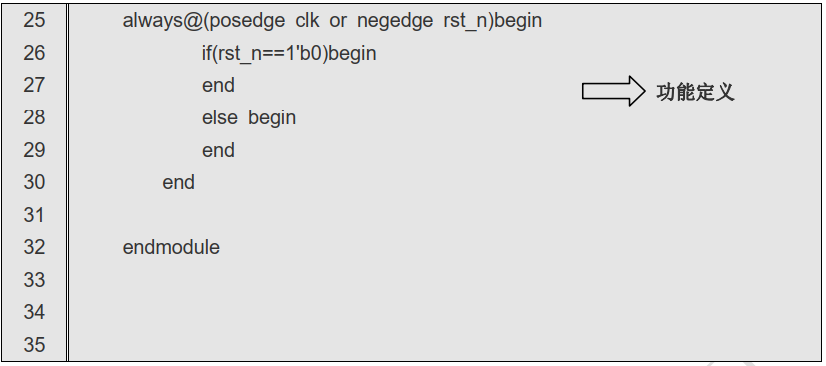

第 21 至 31 行是功能描述部分。模块中最重要的部分是逻辑功能定义部分, 有三种方法可在模块中产生逻辑。

- 用“assign”声明语句,如描

- 述一个两输入与门: assign a = b & c。 详细功能见“功能描述-组合逻辑”一节。

- 用“always”块。即前面介绍的时序逻辑和组合逻辑。

- 模块例化。详细功能见“模块例化”一节。

3.7 模块例化

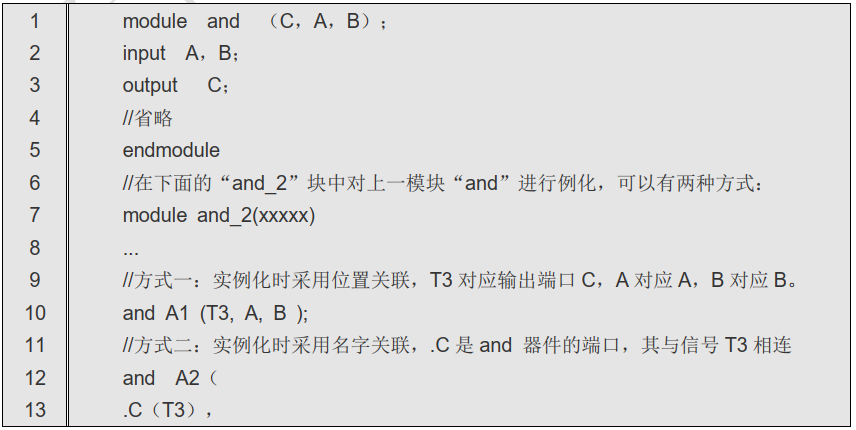

对数字系统的设计一般采用的是自顶向下的设计方式, 可将系统划分成几个功能模块,每个功能模块再划分成下一层的子模块。每个模块的设计对应一个 module , 每个 module 设计成一个 Verilog HDL 程序文件。因此,对一个系统的顶层模块采用结构化设计,即顶层模块分别调用了各个功能模块。

一个模块能够在另外一个模块中被引用,这样就建立了描述的层次。模块实例化语句形式如下:

module_nameinstance_name(port_associations) ;

信号端口可以通过位置或名称关联, 但是关联方式不能够混合使用。端口关联形式如下:port_expr / /通过位置。.

PortName (port_expr) / /通过名称。

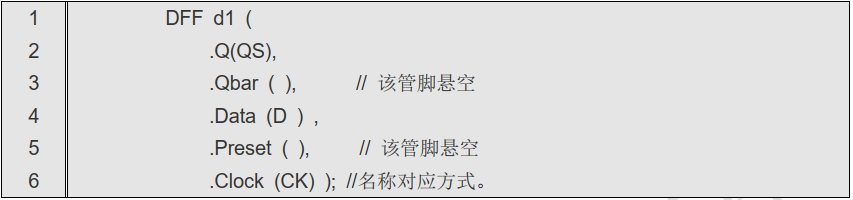

建议:在例化的端口映射中请采用名字关联,这样,当被调用的模块管脚改变时不易出错。在实例化中,可能有些管脚没用到,可在映射中采用空白处理,如:

输入管脚悬空端口的输入为高阻 Z,由于输出管脚是被悬空的,该输出管脚废弃不用。

2376

2376

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?