本文主要介绍FPGA器件的内部结构,可以让我们掌握硬件描述语言和内部单元和连线的映射关系。

其实无论是Xilinx,Altera,Lattice,还是国产 ,内部架构和开发软件都大同小异,一款用熟了,其它FPGA芯片也容易上手。

一、FPGA 组成

1、Intel/Altera FPGA

Intel/Altera FPGA组成:ALMs、LEs、RAM、DSP Blocks、Multipliers、PLLs等。

Intel/Altera的可编程逻辑单元通常被称为LE(Logic Element,逻辑单元),由一个Register和一个LUT组成。再将10个LE有机组合起来,构成更大的逻辑功能单元——逻辑阵列模块(LAB,Logic Array Block),LAB中还包含LE间的进位链、LAB控制信号、LUT级联链、局部互连线资源、寄存器级联链等连线和控制资源。

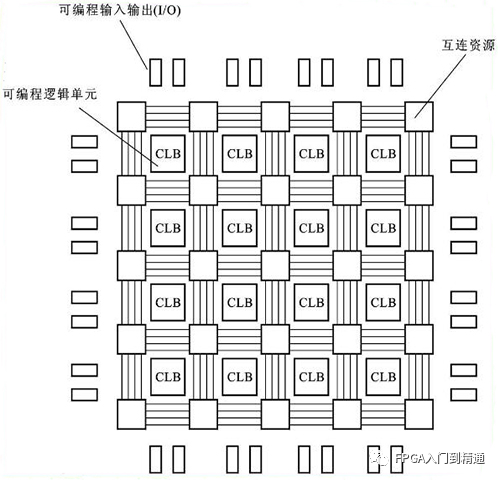

2、Xilinx FPGA

Xilinx FPGA组成:CLB(Configable Logic Block)包含Slices和DRAM。

CLB是由Slices构成的,每一个Slices基本是由LUT、进位链、MUX和寄存器组成。

Xilinx的可编程逻辑单元被称为Slice,由上下两部分组成。每部分都由一个Register和一个LUT组成,被称为LC(LogicCell,逻辑单元),两个LC间也有一些共用逻辑。可以完成LC之间的配合与级联。

3、Lattice FPGA

Lattice组成的主要可编程逻辑单元叫PFU(ProgrammableFuncTIonUnit),是由8个LUT和8~9个Register组成。

二、FPGA基本单元

1、LUT(look up table) 查找表

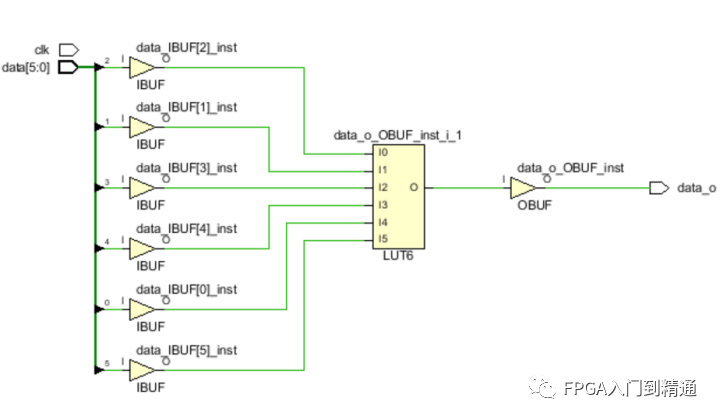

FPGA中主要用LUT代替门电路,下面编写代码看下综合后的原理图。

(1)如果逻辑表达式是“6位输入1位输出” ,综合后的结果是一个LUT6。

module lut_test(

input clk,

input [5:0] data

output data_o

);

assign data_o = data[0]&data[1]&data[2]&data[3]&data[4]&data[5];

endmodule

(2)如果逻辑表达式是“5位以内输入1位输出” ,综合后的结果都是一个LUT5。

module lut_test(

input clk,

input [5:0] data

output data_o

);

assign data_o = ((data[0]&data[1])^data[2]|data[3]&data[4]);

endmodule

2、MUX(多路数据选择器)

以四选一数据选择器(MUX4_1)为例,MUX4_1表示是有4位数据输入(D0-D3),有1位数据输出(Q),地址码则是用来选择输出。

module lut_test(

input clk,

input [1:0] addr,

input [3:0] data,

output reg data_o

);

always @(*) begin

case(addr)

'd0 : data_o = data[0];

'd1 : data_o = data[1];

'd2 : data_o = data[2];

'd3 : data_o = data[3];

endcase

end

endmodule

从图中可以看出,MUX4_1本质上还是一个LUT6,只不过它将2位地址输入和4位数据输入一起连接到LUT6的输入端。

3、进位链(半加器,全加器,多位加法器)

(1)半加器

两个输入数据位(A、B)相加,输出一个结果位(S)和进位(C),没有进位输入的加法器电路称为半加器。

(2)全加器

两个输入数据位(A、B)以及输入低位进位相加,输出一个结果位(S)和进位(C),称为全加器。

(3)多位加法器

最低位是半加器,或低位进位输入置0的全加器。再与全加器级联即可做成多位加法器。

将第1个全加器的低位进位置1,其他3个全加器级联将成为4位减法器。

4、存储单元和CLB

(1)触发器

通过检测时钟边沿(上升沿、下降沿)时,将输入给到输出。触发器是计算机记忆装置的基本单元,一个触发器能储存一位二进制代码,一个触发器可以组成一个1位的寄存器,多个触发器可以组成一个多位的寄存器

(2)锁存器

通过检测使能信号电平(高电平、低电平)来改变存储的输出状态。锁存器因为不需要时钟,所以不是时序元件,它对毛刺无过滤功能,非常敏感,容易出问题,在很多情况下都是要避免使用的。

注意:为了防止锁存器的产生,在组合逻辑一定要将判断语句给完整,如if语句必须有else、case语句加default,而时序逻辑则不需要考虑这个问题。

(3)存储单元

以xilinx 7系列为例,主要存储单元是可编程逻辑块CLB,它有两个SLICE,每个SLICE都有8个存储单元。这个存储单元,实际上是由4个触发器FF和4个触发器FF或锁存器组成)。

如上图所示,左边的4个存储单元只能作为触发器使用,但右边的4个存储单元则可以作为触发器或者锁存器使用。

5、内嵌RAM

FPGA的内嵌RAM块有BLOCK RAM 和ULTRA RAM,可以灵活配置为ROM、单端口RAM、双端口RAM、伪双端口RAM、内容地址存储器CAM、FIFO等常用存储器结构。

Xilinx常用的RAM块大小是4Kbit和18Kbit两种结构,lattice常用的RAM块大小是9Kbit,Altera常用的RAM块分别是M9KRAM(9Kbit),M-144K(144Kbit)。

以xilinx 双端口IP为例,编译后如下图所示

6、DSP48E1

dsp48E1基本结构图如下:

(1)一个预加器(加法器),实现的是A(最大位宽30)与D(最大位宽是25)的相加,输出的结果最大位宽为25,该预加器不用的时候可以选择旁路掉。

(2)一个25x18乘法器,两个乘数分别为B(最大位宽18位),以及A与D相加后结果的低25位,输出的结果为48(高5位是符号拓展位,低43位是数据位)

(3)这个功能比较多,能做加(减)法器,累加(减)法器,逻辑运算(与或非),输出最大位宽为48位数据位+4位进位。

(4)一个模式探测器,主要实现带掩膜的数据比较,上下溢出检测,计到一定数对结果进行重置功能。

(5)一个数据选择器,它的两个数据输入端分别为C和P(最大位宽48),可以决定DSP48E1做普通加法还是做累加功能。

7、布线资源

布线资源类似绘制PCB板时的连线资源,是为了能够让位于FPGA不同位置的逻辑资源块、时钟处理单元、BLOCK RAM、DSP和接口模块等资源能够相互通信,从而协调合作,完成所需功能,连线的长度和工艺决定了信号在连线上的驱动能力和传输速度。

主要有以下三种布线资源可供利用:

(1)全局性的专用布线资源:用来完成器件内部的全局时钟和全局复位/置位的布线。

(2)长线资源:完成器件Bank间的一些高速信号和一些第二全局时钟信号的布线。

(3)短线资源:完成基本逻辑单元之间的逻辑互联和布线。

(4)其它资源:在基本逻辑单元内部还存在各式各样的布线资源和专用时钟、复位等控制信号线。

8、底层嵌入功能单元

通用程度较高的嵌入功能模块,如PLL、DLL、DSP和CPU等。

Inter/Altera芯片集成的是PLL,Xilinx芯片主要集成的是DLL,Lattice的新型FPGA同时集成了PLL与DLL以适应不同的需求。

Inter/Altera芯片的PLL模块分为增强型PLL(EnhancedPLL)和快速PLL(FastPLL)。

Xilinx芯片DLL的模块名称为CLKDLL,在高端FPGA中CLKDLL的增强型模块为DCM(数字时钟管理模块)。

PLL全称为 Phase Locked Loop,即电子工程师经常挂在嘴边的锁相环,其本身也是一种反馈控制电路,可以对时钟网络进行系统级的时钟管理、偏移控制,达到时钟倍频、分频、相位偏移和可编程占空比的效果。。

9、用户可编程I/O

用户可编程I/O(User I/Os,也被称为IOE),分布在整个芯片的四周,如下图所示。

以xilinx为例, 通常 xilinx 的功能命名格式为:IO_LXXY#/IO_XX。

IO 代表用户 IO;

L 代表差分,XX 代表在当前 BANK 下的唯一标识号,Y=[P|N]表示 LVDS 信号的 P 或者 N;

# 表示 Bank 号。

如IO_L13P_T2_MRCC_12,表示这是个用户 IO,差分信号, BANK12 的第 13 对差分的 P 端口,也是全局时钟网络输入管脚(MRCC 是全局时钟网络)

除了 FPGA 的用户 IO 外,还有很多其他的功能 IO,如下载接口、模式选择接口、MRCC、电源引脚等等。

----------------------------------------------------------------------

以上就是本次分享的FPGA内部结构,希望大家阅读完后,有所收获。

本文由FPGA入门到精通原创,公众号为“FPGA入门到精通”,github开源代码:“FPGA知识库”

2103

2103

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?