远程FPGA虚拟实验平台用SystemVerilog HDL实现流水灯和移位寄存器

原理

流水灯

本实验中,流水灯仅供学习,此处对照代码察看实验图,代码详解见注释,根据代码可知流水灯实现左移。

/** The input port is replaced with an internal signal **/

wire reset = PB[0];

wire clk = PB[1];

/************* The logic of this experiment *************/

logic [7:0]q;

always @ (posedge clk or posedge reset)//注意这里在reset前需要加入上升沿判断,不加的话就是混用了

if (reset)//由于判断条件中是上升沿,所以此处需要在reset=1时进行赋值,这是对应的

q <= 1;//q作为一个八位的数,当q被赋值1时实际上是00000001

else

q <= {q[6:0], q[7]};//此处代码意为:新的q'<={q[6],q[5],q[4],q[3],q[2],q[1],q[0],q[7]},于是原本为1的q[0]被移到了新的q'的q[1]位置,实现左移

/****** Internal signal assignment to output port *******/

assign L[7:0] = q[7:0];

endmodule

移位寄存器

源代码

移位寄存器

VirtalBoard模块

实验面板:

`default_nettype none

module VirtualBoard (

input logic CLOCK, // 10 MHz Input Clock

input logic [19:0] PB, // 20 Push Buttons, logical 1 when pressed

input logic [35:0] S, // 36 Switches

output logic [35:0] L, // 36 LEDs, drive logical 1 to light up

output logic [7:0] SD7, // 8 common anode Seven-segment Display

output logic [7:0] SD6,

output logic [7:0] SD5,

output logic [7:0] SD4,

output logic [7:0] SD3,

output logic [7:0] SD2,

output logic [7:0] SD1,

output logic [7:0] SD0

);

连一堆开关线:

localparam N = 8;//传递参数N的值为8

wire reset = PB[0];

wire clk = PB[1];

wire [7:0]data = S[7:0];

wire load = S[8];

wire en = S[9];

实例化RightShifter:

logic [N-1:0] q;//要搞个q

RightShifter #(N) RS0(.Clk(clk), .Reset(reset), .iLoad(load), .iEnable(en), .iLeftIn(q[0]), .iD(data), .oQ(q));//实例化,注意iLeftIn的值在这里给

连一下灯:

/****** Internal signal assignment to output port *******/

assign L[7:0] = q[7:0];

endmodule//->整个模块结束

RightShifter模块

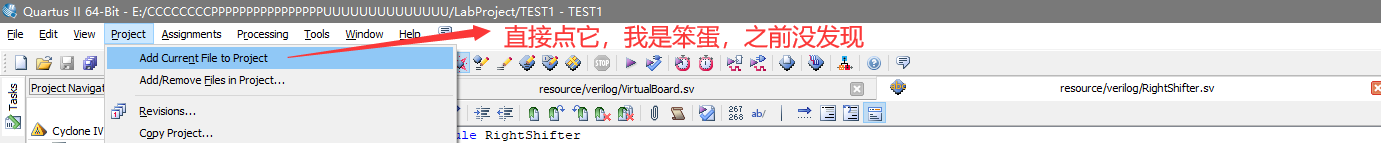

这次有更快的加文件方法,写完RightShifter.sv文件之后保存,然后直接如图操作。(对,之前我一直没意识到这个方法)

该模块代码如下:

module RightShifter

#(parameter N = 4)//实验文件要求默认取值为4

(

input wire Clk,

input wire Reset,

input wire iLoad,

input wire iEnable,

input wire iLeftIn,

input wire [N-1:0] iD,

output reg [N-1:0] oQ

);

always @ (posedge Clk or posedge Reset) begin

if (Reset)//优先度最高

oQ <= 0;

else if (iLoad)//优先度第二

oQ <= iD;

else if (iEnable)//优先度第三

oQ[N-1:0] <= {iLeftIn , oQ[N-1:1]};//以N为8举例,意为:新的oQ'<={iLeftIn,oQ[7],oQ[6],oQ[5],oQ[4],oQ[3],oQ[2],oQ[1]},又因为iLeftIn在virtualboard模块实例化的时候赋值是q[0],所以实现右移

end

endmodule

测试/保存/提交

老规矩,保存的时候还是建议把RightShifter.sv放在工程文件夹内的resource\verilog文件夹,方便找。

根据上次实验的经验,老师说不管实验平台显示得几分,都要提交记录,所以就老老实实提交。

2167

2167

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?