FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是标配了。从PCI到PCI Express, 从ATA到SATA,从并行ADC接口到JESD204, 从RIO到Serial RIO,…等等,都是在借助SerDes来提高性能。SerDes是非常复杂的数模混合设计,用户手册的内容只是描述了森林里面的一棵小树,并不能够解释SerDes是怎么工作的。SerDes怎么可以没有传输时钟信号?什么是加重和均衡?抖动和误码是什么关系?各种抖动之间有什么关系?本篇小文试着从一个SerDes用户的角度来理解SerDes是怎么设计的, 由于水平有限,一定有不够准确的地方,希望对刚开始接触SerDes的工程师有所帮助。

Contents

2.1串行器解串器(Serializer/Deserializer) 6

2.7 SerDes收发Driver及差分接口转换... 19

1. SerDes 的价值

1.1并行总线接口

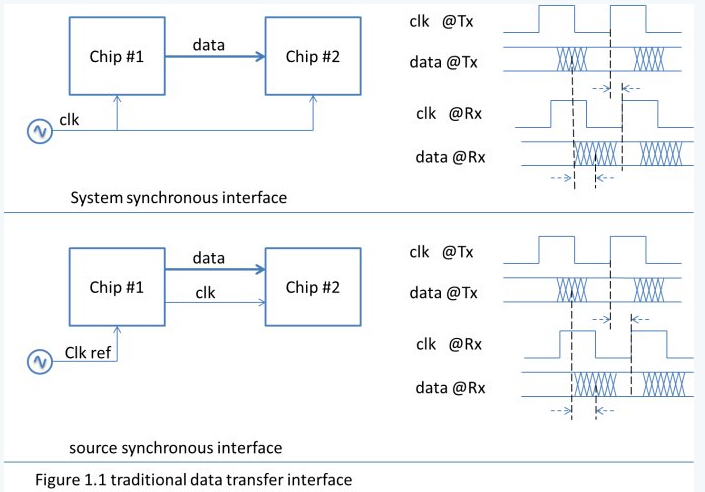

在SerDes流行之前,芯片之间的互联通过系统同步或者源同步的并行接口传输数据,图1.1演示了系统和源同步并行接口。

随着接口频率的提高,在系统同步接口方式中,有几个因素限制了 有效数据窗口宽度 的继续增加。

l

l

l

虽然可以通过在目的芯片(chip #2)内用PLL补偿时钟延时差(clock skew),但是PVT变化时,时钟延时的变化量和数据延时的变化量是不一样的。这又进一步恶化了数据窗口。

源同步接口方式中,发送侧Tx把时钟伴随数据一起发送出去, 限制了clock skew对有效数据窗口的危害。通常在发送侧芯片内部,源同步接口把时钟信号和数据信号作一样的处理,也就是让它和数据信号经过相同的路径,保持相同的延时。这样PVT变化时,时钟和数据会朝着同一个方向增大或者减小相同的量,对skew最有利。

我们来做一些合理的典型假设,假设一个32bit数据的并行总线,

a)发送端的数据skew = 50 ps

b)pcb走线引入的skew = 50ps

c)时钟的周期抖动jitter = +/-50 ps

d)接收端触发器采样窗口 = 250 ps

可以大致估计出并行接口的最高时钟 = 1/(50+50+100+250) = 2.2GHz (DDR)或者1.1GHz (SDR)。

利用源同步接口,数据的有效窗口可以提高很多。通常频率都在1GHz以下。在实际应用中可以见到如SPI4.2接口的时钟可以高达DDR 700MHz x 16bits位宽。DDR Memory接口也算一种源同步接口,如DDR3在FPGA中可以做到大约800MHz的时钟。

要提高接口的传输带宽有两种方式,一种是提高时钟频率,一种是加大数据位宽。那么是不是可以无限制的增加数据的位宽呢?这就要牵涉到另外一个非常重要的问题-----同步切换噪声(SSN)。

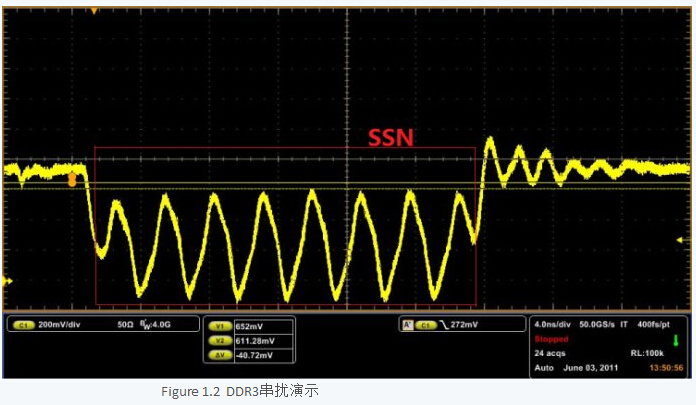

这里不讨论SSN的原理,直接给出SSN的公式 SSN = L *N* di/dt。L是芯片封装电感,N是数据宽度,di/dt是电流变化的斜率。随着频率的提高,数据位款的增加,SSN成为提高传输带宽的主要瓶颈。图1.2是一个DDR3串扰的例子。图中低电平的理论值在0V,由于SSN的影响,低电平表现为震荡,震荡噪声的最大值达610mV,因此噪声余量只有1.5V/2-610mV=140mV。

因此也不可能靠无限的提高数据位宽来继续增加带宽。一种解决SSN的办法是使用差分信号替代单端信号,使用差分信号可以很好的解决SSN问题,代价是使用更多的芯片引脚。使用差分信号仍然解决不了数据skew的问题,很大位宽的差分信号再加上严格的时序限制,给并行接口带来了很大的挑战。

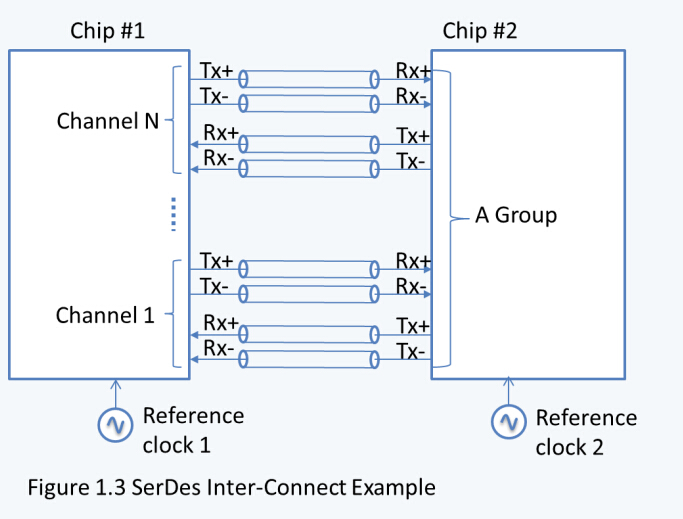

源同步接口的时钟频率已经遇到瓶颈,由于信道的非理想(channel)特性,再继续提高频率,信号会被严重损伤,就需要采用均衡和数据时钟相位检测等技术。这也就是SerDes所采用的技术。SerDes(Serializer-Deserializer)是串行器和解串器的简称。串行器(Serializer)也称为SerDes发送端(Tx),(Deserializer)也称为接收端Rx。Figure1.3是一个N对SerDes收发通道的互连演示,一般N小于4。

可以看到,SerDes不传送时钟信号,这也是SerDes最特别的地方,SerDes在接收端集成了CDR(Clock Data Recovery)电路,利用CDR从数据的边沿信息中抽取时钟,并找到最优的采样位置。

SerDes采用差分方式传送数据。一般会有多个通道的数据放在一个group中以共享PLL资源,每个通道仍然是相互独立工作的。

SerDes需要参考时钟(Reference Clock),一般也是差分的形式以降低噪声。接收端Rx和发送端Tx的参考时钟可以允许几百个ppm的频差(plesio-synchronous system),也可以是同频的时钟,但是对相位差没有要求。

作个简单的比较,一个SerDes通道(channel)使用4个引脚(Tx+/-,Rx+/-), 目前的FPGA可以做到高达28Gbps。而一个16bits的DDR3-1600的线速率为1.6Gbps*16 = 25Gbps,却需要50个引脚。此对比可以看出SerDes在传输带宽上的优势。

相比源同步接口,SerDes的主要特点包括:

l

l

l

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5758

5758

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?