从小父亲就教育我,做一个对社会有用的人!

目录

3.2.1 Four-beat wrapping burst, WRAP4

3.3.2 Four-beat incrementing burst, INCR4

本文内容来自于《AMBA AHB Protocol Specification》

Chapter1 Introduction

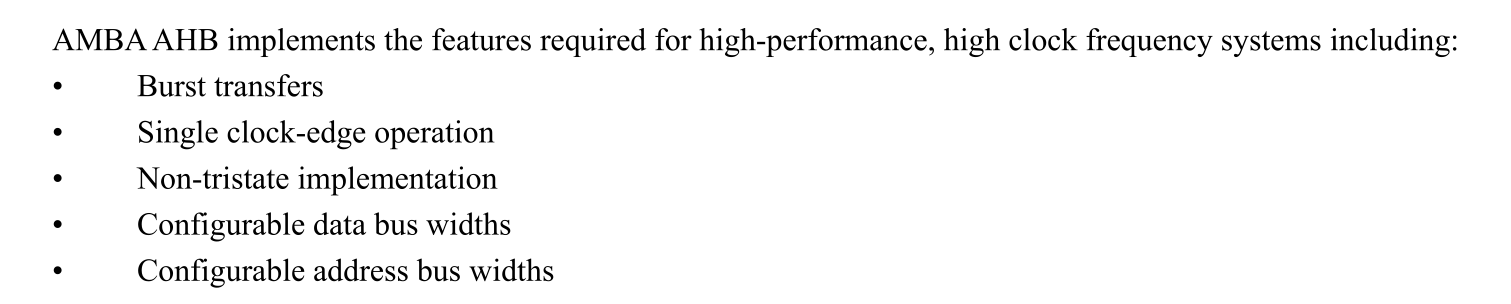

1.1 AHB Block Diagram

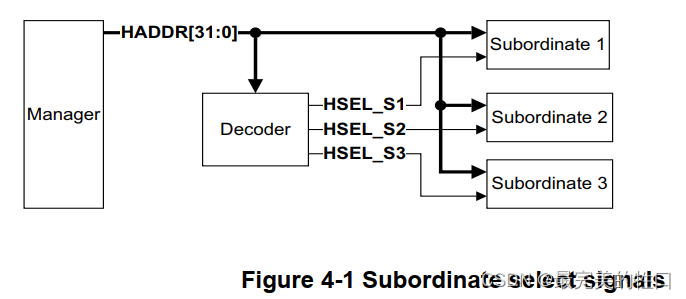

从这幅图可以看到,master是主动发起者,slave是被动响应者。

•Decoder监控Master 的地址选择到对应的Slave

•Multiplexor将对应的slave的输出路由回Master

1.1.1 master

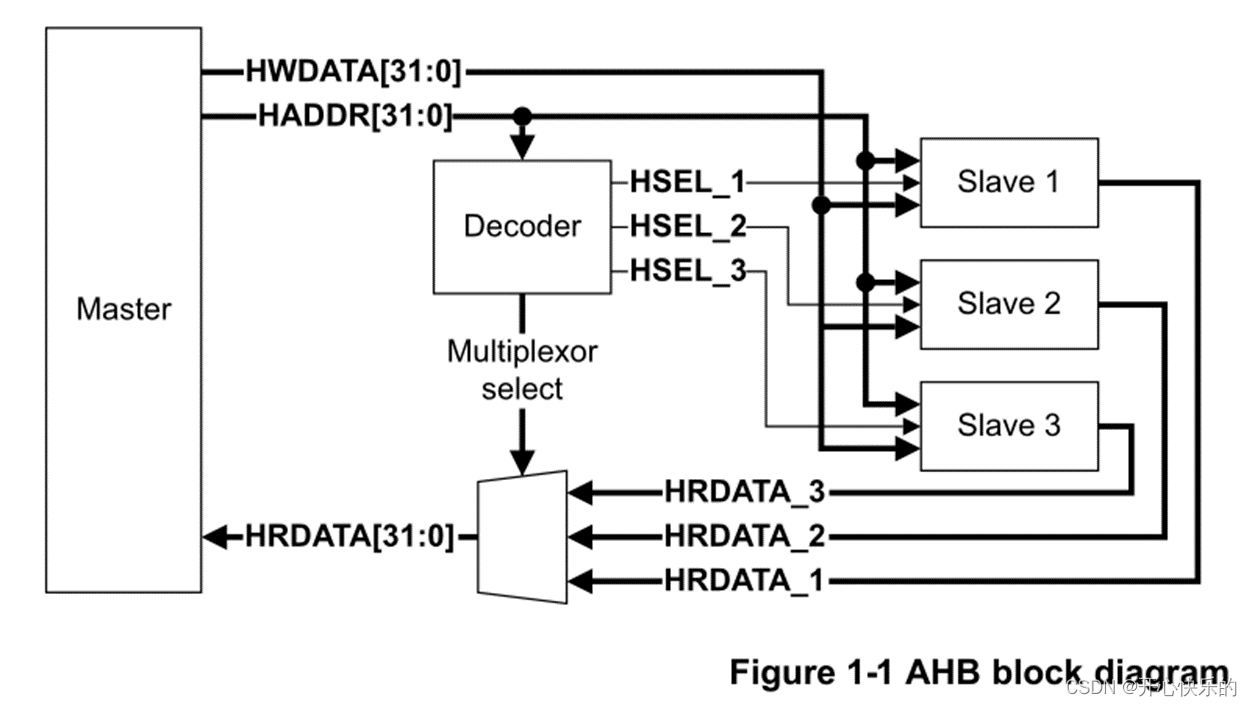

A Manager provides address and control information to initiate read and write operations. Figure 1-2 shows a Manager interface.

Manager提供地址和控制信息,用于初始化读写操作。

Figure 1-2 manager interface

从图1-2可以看到的是,左面的信号是slave 反馈给master的信号;右边的信号是master发送给slave的信号。

1.1.2 slave

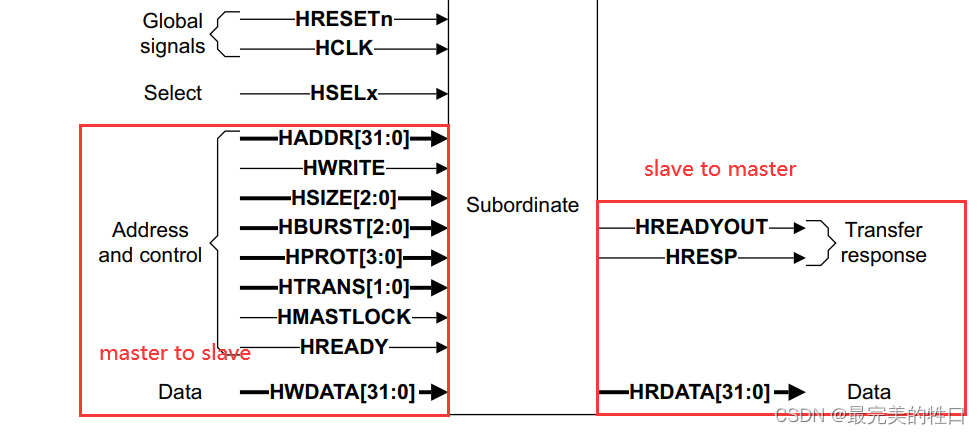

A Subordinate responds to transfers initiated by Managers in the system. The Subordinate uses the HSELx select signal from the decoder to control when it responds to a bus transfer.

Figure 1-3 Subordinate interface

从图1.3可以知道的是,左边的信号是master给slave的,右边的信号是slave反馈给master的信号。

1.1.3 interconnect

(略)

1.2 revisions

(略)

1.3 operation

The Manager starts a transfer by driving the address and control signals. These signals provide information about the address, direction, width of the transfer, and indicate if the transfer forms part of a burst. Transfers can be:

- Single.

- Incrementing bursts that do not wrap at address boundaries.

- Wrapping bursts that wrap at particular address boundaries.

| The write data bus moves data from the Manager to a Subordinate, and the read data bus moves data from a Subordinate to the Manager. |

Every transfer consists of:

Address phase :One address and control cycle.

Data phase :One or more cycles for the data.

A Subordinate cannot request that the address phase is extended and therefore all Subordinates must be capable of sampling the address during this time. However, a Subordinate can request that the Manager extends the data phase by using HREADY. This signal, when LOW, causes wait states to be inserted into the transfer and enables the Subordinate to have extra time to provide or sample data.

The Subordinate uses HRESP to indicate the success or failure of a transfer.

=======================================================================

Chapter2 Singal Descriptions

All AHB-Lite and AHB5 signals are prefixed with the letter H to differentiate them from other similarly named signals in a system design.

2.1 Global signals

Each component uses a single clock signal, HCLK. All input signals are sampled on the rising edge of HCLK. All output signal changes must occur after the rising edge of HCLK.

The reset signal, HRESETn, is the only active LOW signal in the protocol and is the primary reset for all bus elements. The reset can be asserted asynchronously, but is deasserted synchronously after the rising edge of HCLK.

2.2 master signals

Table 2-2 lists the protocol signals generated by a Manager.

=========================

2.2.1 Burst operation

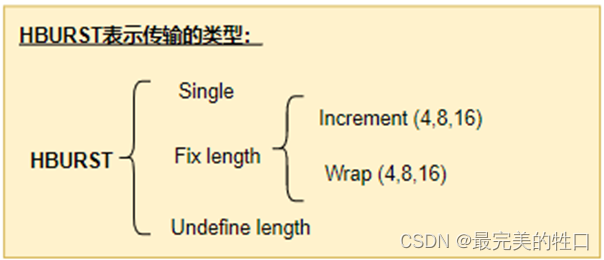

Bursts of 4, 8, and 16-beats, undefined length bursts, and single transfers are defined in this protocol. It supports incrementing and wrapping bursts:

- Incrementing bursts access sequential locations and the address of each transfer in the burst is an increment of the previous address.递增的突发访问顺序位置,突发中每个传输的地址是前一个地址的增量。

- Wrapping bursts wrap when they cross an address boundary. The address boundary is calculated as the product of the number of beats in a burst and the size of the transfer. The number of beats are controlled by HBURST and the transfer size is controlled by HSIZE.

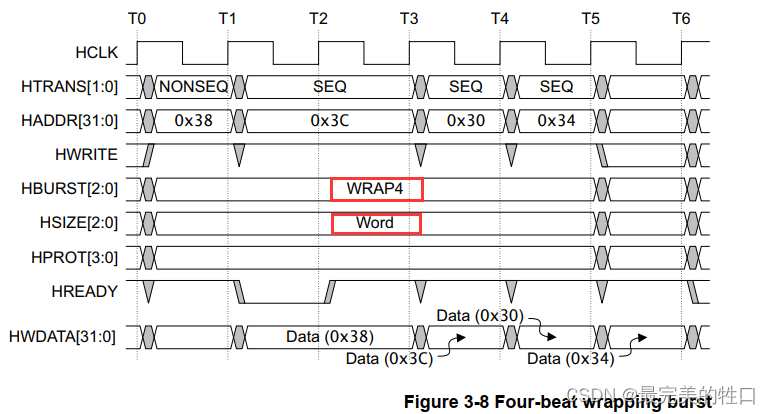

For example, a four-beat wrapping burst of word (4-byte) accesses wraps at 16-byte boundaries. 4个WORD! Therefore, if the start address of the burst is 0x34, then it consists of four transfers to addresses 0x34, 0x38, 0x3C, and 0x30.

Four-beat incrementing burst, INCR4

Managers must not attempt to start an incrementing burst that crosses a 1KB address boundary.

HBURST[2:0] controls the burst type. Table 3-4 lists the possible burst types.

====================================== ==================================

这两个信号就不细讲了。用到的地方不多。

=========================================================================

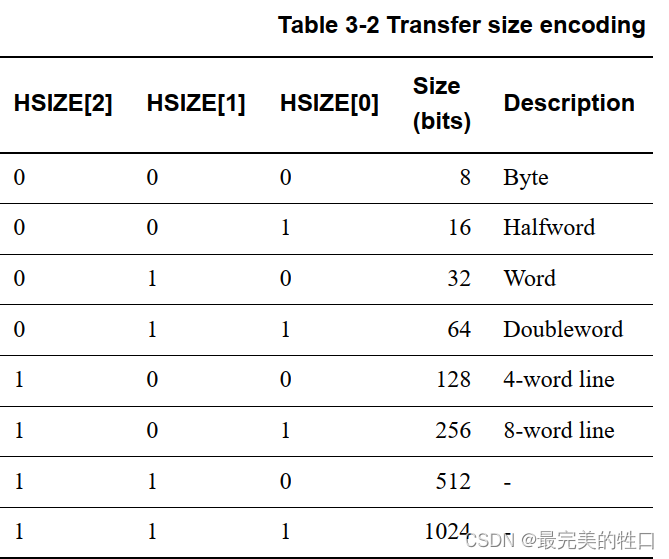

2.2.2 Transfer size

HSIZE[2:0] indicates the size of a data transfer. Table 3-2 lists the possible transfer sizes.

它主要的功能就是决定数据传输的位宽。通常HSIZE都是‘h2,32bit传输用的多一些。

NOTE: The transfer size set by HSIZE must be less than or equal to the width of the data bus. For example, with a 32-bit data bus, HSIZE must only use the values 0b000, 0b001, or 0b010.

=======================================================================

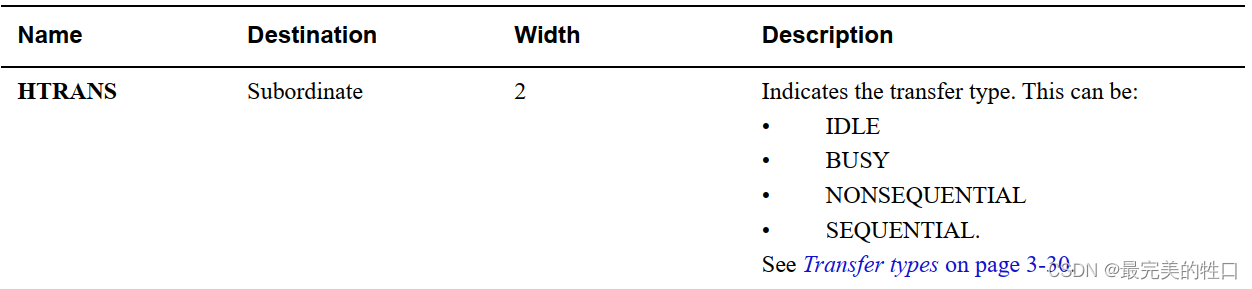

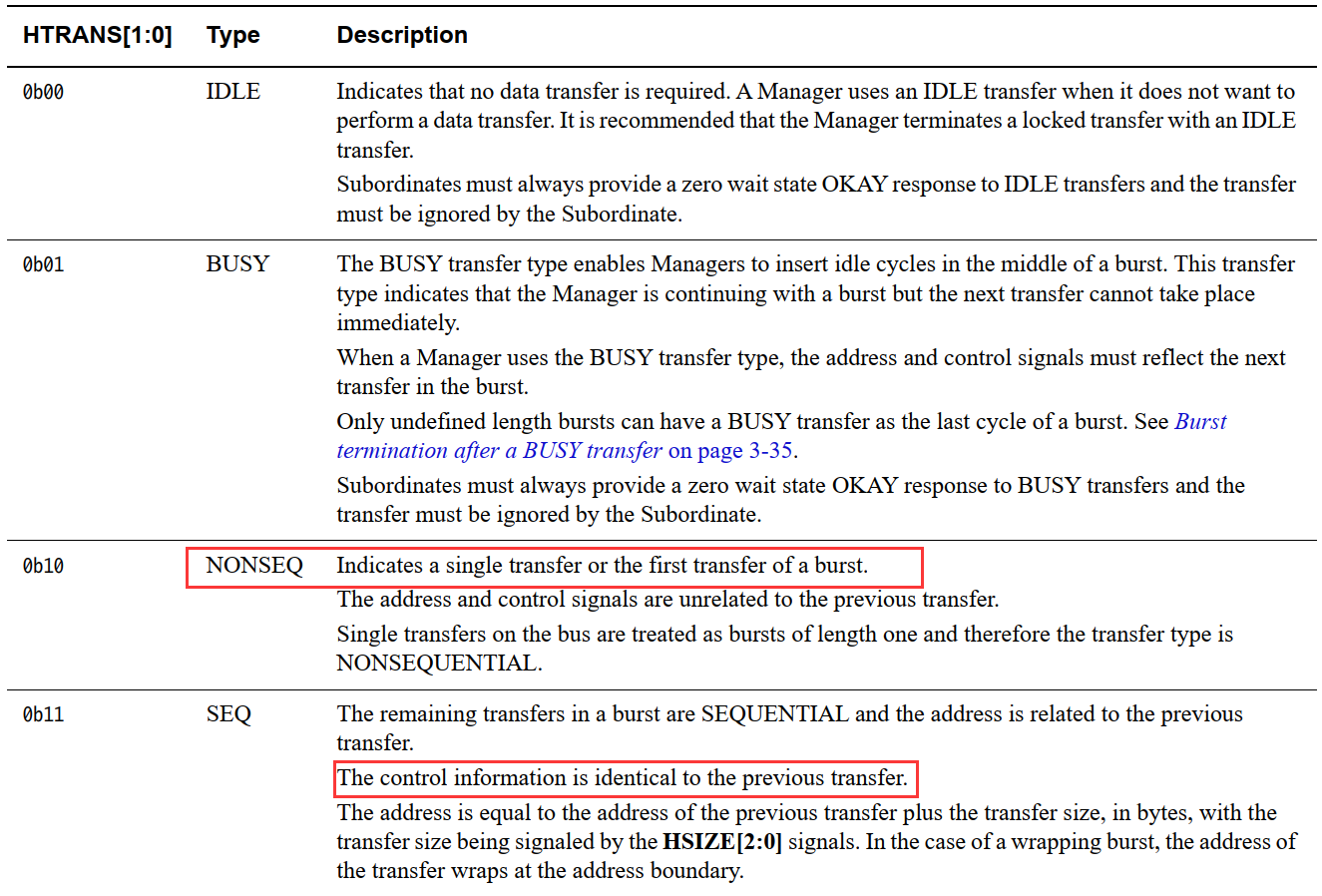

2.2.3 Transfer types

Table 3-1 lists the transfers that can be classified into one of four types, as controlled by HTRANS[1:0].

========================================================================

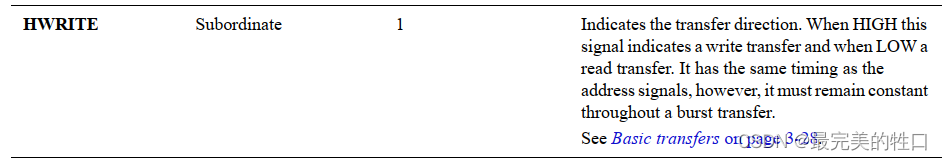

2.2.4 WRITE and WDATA

=========================================================================

=========================================================================

2.3 Slave Signal

Table 2-3 lists the protocol signals generated by a Subordinate (slave).

2.3.1 HRDATA and HREADYOUT

=========================================================================

2.3.2 HRESP

2.4 Decoder signals

2.5 Multiplexor signals

Table 2-5 lists the protocol signals generated by the multiplexor.

Chapter3 Transfers

3.1 Basic transfer

A transfer consists of two phases:

Address Lasts for a single HCLK cycle unless it is extended by the previous bus transfer.

Data Might require several HCLK cycles. Use the HREADY signal to control the number of clock cycles required to complete the transfer.

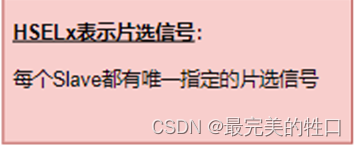

HWRITE controls the direction of data transfer to or from the Manager. Therefore, when:

• HWRITE is HIGH, it indicates a write transfer and the Manager broadcasts data on the write data bus, HWDATA.

• HWRITE is LOW, a read transfer is performed, and the Subordinate must generate the data on the read data bus, HRDATA.

3.1.1 no wait

The simplest transfer is one with no wait states, so the transfer consists of one address cycle and one data cycle.

Figure 3-1 shows a simple read transfer and Figure 3-2 shows a simple write transfer.

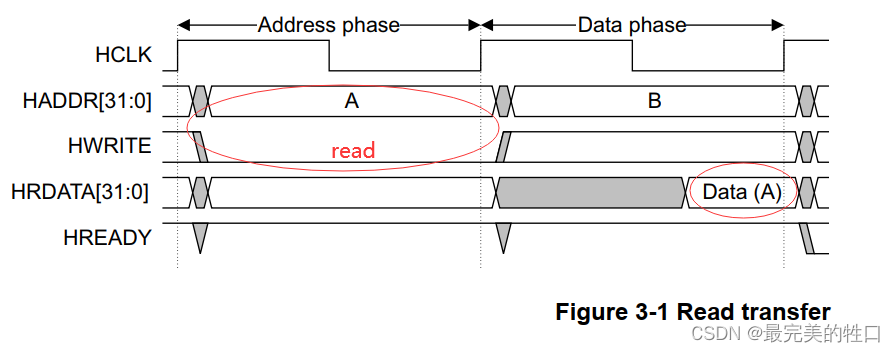

3.1.2 with wait

Figure 3-3 shows a read transfer with two wait states.

Figure 3-4 shows a write transfer with one wait state.

下面再看看这幅图很有帮助:

•在采集到hclk的上升沿后,master开始驱动地址和控制信号

•Slave在第二个上升沿后采集到地址和控制信息

•Slave会驱动HREADYOUT 来response, Master会在第三个上升沿采集到这个response,传输结束

Figure Transfer with no wait state

下面再详细说一下:

原因:从机未必处于就绪状态等待时的读写:

写:要保持写的状态直至传输完成

读:只有当Hready为高时,slave才会获取有效值

Figure AHB transfer with wait

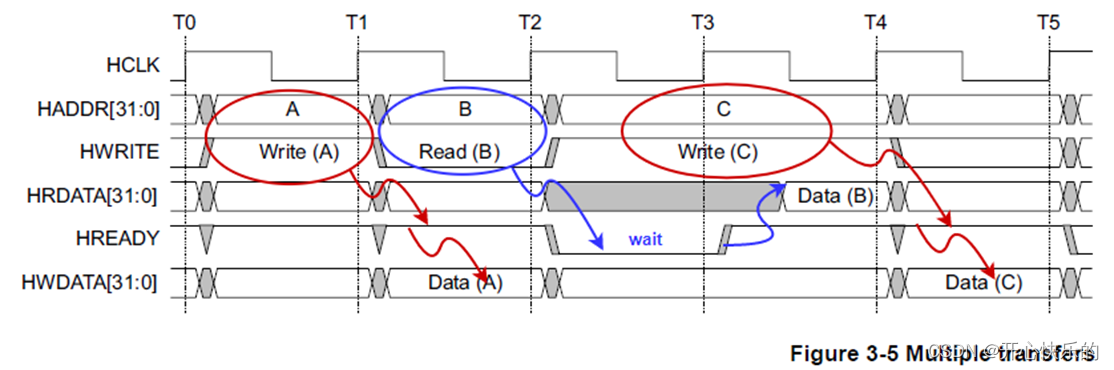

3.1.3 multiple transfer

When a transfer is extended in this way, it has the side-effect of extending the address phase of the next transfer.

Figure 3-5 shows three transfers to unrelated addresses, A, B, and C with an extended address phase for address C

Figure 3-6 shows the use of the NONSEQ, BUSY, and SEQ transfer types.

T0-T1 The 4-beat read starts with a NONSEQ transfer.

T1-T2 The Manager is unable to perform the second beat and inserts a BUSY transfer to delay the start of the second beat.

The Subordinate provides the read data for the first beat.

T2-T3 The Manager is now ready to start the second beat, so a SEQ transfer is signaled. The Manager ignores any data that the Subordinate provides on the read data bus.

T3-T4 The Manager performs the third beat.

The Subordinate provides the read data for the second beat.

T4-T5 The Manager performs the last beat.

The Subordinate is unable to complete the transfer and uses HREADYOUT to insert a single wait

state.

T5-T6 The Subordinate provides the read data for the third beat.

T6-T7 The Subordinate provides the read data for the last beat.

Table 3-1 Transfer type encoding

3.2 Burst examples

3.2.1 Four-beat wrapping burst, WRAP4

Figure 3-8 shows a write transfer using a four-beat wrapping burst, with a wait state added for the first transfer.

Because the burst is a four-beat burst of word transfers, the address wraps at 16-byte boundaries, and the transfer to address 0x3C is followed by a transfer to address 0x30.

3.3.2 Four-beat incrementing burst, INCR4

Figure 3-9 shows a read transfer using a four-beat incrementing burst, with a wait state added for the first transfer. In this case, the address does not wrap at a 16-byte boundary and the address 0x3C is followed by a transfer to address 0x40.

到底是如何回环的呢?

8-beat 8*4=32B-->0x20

起始地址是0x34, 下一个是0x38,下一个是0x3c,下一个是0x40???

0x40=64/32,可以被整除,那么64-32=32. (0x20)就是下一个地址!

既然都说了回环,相信你已经有了答案。

0x34,0x38,0x3c,0x20,0x24,0x28,0x2c,0x30.

关于AHB总线回环突发 wrap burst模式地址的理解_为什么ahb wrap要回环-CSDN博客

3.3 AHB接口Overview

如果你和我一样,曾经分不清AHB master和slave,请看下面的这几张图。

如果我们把UVM验证环境看作一个agent,RTL要是做MASTER的话,agent就可以理解为SLAVE.可以看RTL代码中AHB的接口怎么定义。

AHB MASTER

站在验证角度,如果RTL作为SLAVE的话,uvm agent就可以理解为MASTER. AHB VIP的输出给RTL的输入。

AHB SLAVE

如果大家对STRB信号不熟悉的话,可以参考这篇文章!写的非常清晰。

https://blog.csdn.net/weixin_52162715/article/details/131339011

欢迎大家一起讨论学习!需要相关文档资料的同学可以给我发邮件!

lixingyi09@qq.com

振兴中华

9664

9664

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?