目录

方法task和函数function

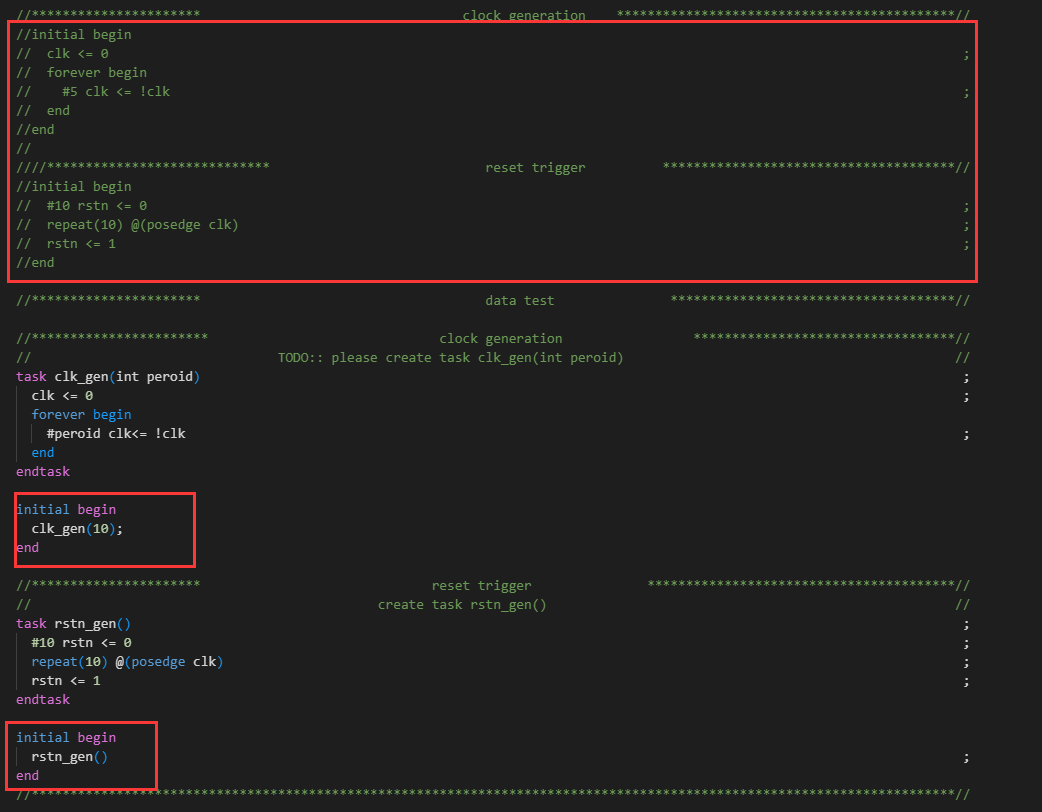

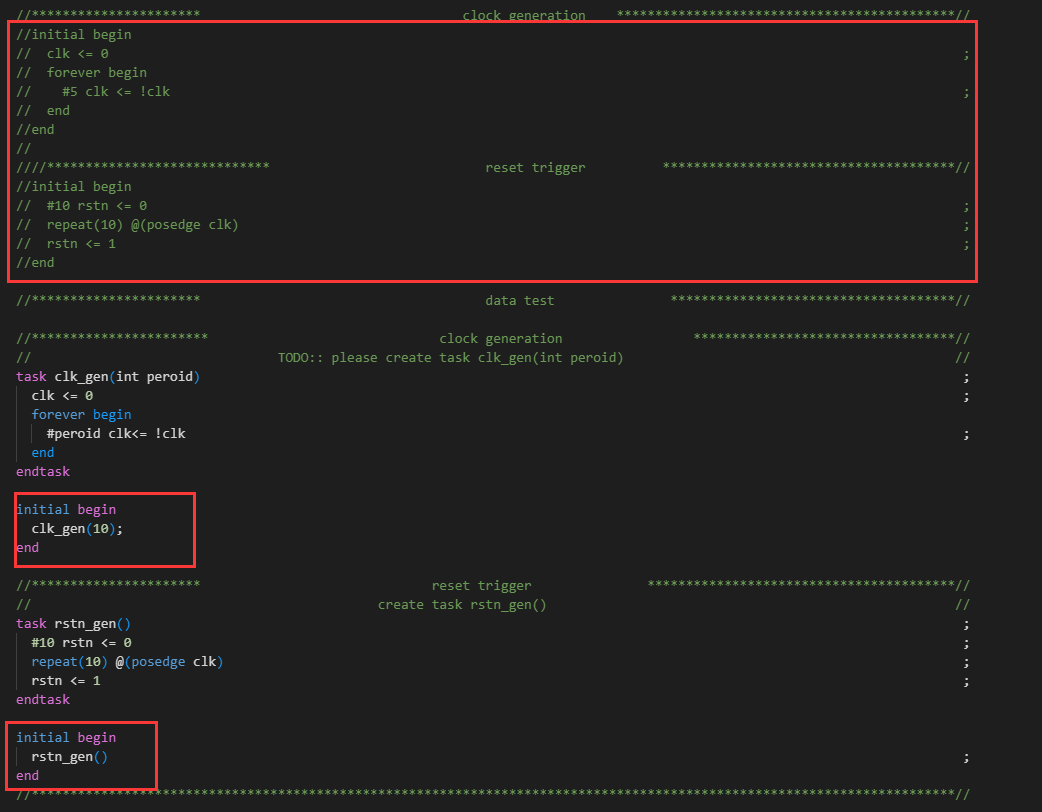

首先要明白一个事情!Task任务,是消耗时间的,函数function是不消耗时间的!

这样写看着是不是很高大上呢?此外,如果我们想修改时钟周期怎么办呢?这时我们可以在task clk_gen(int period),然后再initial的clk_gen()中我们可以传入参数clk_gen(10)。这时就不能在继续延迟#5ns了!要替换成#period

本文介绍了System Verilog中的任务task和函数function的区别,task会消耗时间,而function则不会。同时讲解了如何在task中调整时钟周期。此外,还阐述了接口在连接DUT与VIP中的作用,以及System Verilog中return语句在控制流程中的重要性。

本文介绍了System Verilog中的任务task和函数function的区别,task会消耗时间,而function则不会。同时讲解了如何在task中调整时钟周期。此外,还阐述了接口在连接DUT与VIP中的作用,以及System Verilog中return语句在控制流程中的重要性。

目录

首先要明白一个事情!Task任务,是消耗时间的,函数function是不消耗时间的!

这样写看着是不是很高大上呢?此外,如果我们想修改时钟周期怎么办呢?这时我们可以在task clk_gen(int period),然后再initial的clk_gen()中我们可以传入参数clk_gen(10)。这时就不能在继续延迟#5ns了!要替换成#period

1387

1387

546

546

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?