背景

基于Xilinx的7系列FPGA,

在通过文档《ug474_7Series_CLB.pdf》学习7系列CLB过程中,

对7系列CLB中的移位寄存器(Shift Registers)进行展开学习,遂就有了此文。

系列目录与链接

基于Xilinx的7系列FPGA,笔者在对CLB进行学习、研究时,归纳并总结出了以下博文:

1、分篇1:《7系列 之 查找表(Look-Up Table,LUT)》

2、分篇2:《7系列 之 存储单元(Storage Elements)》

3、分篇3:《7系列 之 多路复用器(Multiplexers)》

4、分篇4:《7系列 之 进位逻辑(Carry Logic)》

5、分篇5:《7系列 之 分布式RAM(Distributed RAM)》

6、分篇6:《7系列 之 7系列 之 移位寄存器(Shift Registers)》

7、总纲 :《7系列 之 可配置逻辑块(7 Series Configurable Logic Block,CLB)》

说明1:本系列基于文档文档《ug474_7Series_CLB.pdf》而写,翻译和感悟,会出现中英文混合的情况。

说明2:虽然文中会出现一些原文的部分截图,但非常支持并推荐道友们去看原汁原味的官方文档

说明3:在查阅相关资料过程中,发现一些关于相关知识点的介绍零零散散,本系列会对其进行整合,力求详尽。

说明4:如果文章有误,欢迎道友们指出、讨论,笔者也会积极改正,希望一起进步!

Table of Contents

Ch.1: 7系列中的SLICEL & SLICEM

1.1 ··· Slice的构成

-

Slice是 Xilinx 公司定义的基本逻辑单位

-

每个Slice中都包含:

1、 4个 6输入查找表(6-inputs look-up tables,LUT6)

2、 8个 存储单元(storage elements )

3、 3个 数据选择器(wide-function multiplexers)

4、 1个 进位链(carry logic) -

每个Slice都使用这些单元来提供逻辑、算术和ROM功能。

-

一些Slices支持两个额外的功能:用分布式RAM来存储数据、用32位寄存器来进行数据移位(移位寄存器)。

支持这两个额外功能的Slices称为SLICEM,其它的Slices被称为SLICEL。

1、大约三分之二的Slices是SLICEL(L:Logic),剩余的是SLICEM(M:Memory)。

2、数量比:SLICEL :SLICEM = 2 :1

1.2 ··· SLICEL & SLICEM

- SLICEL结构:

- SLICEM结构:

由上述两个图可以看出,SLICEM和SLICEL的大体结构相同。但是,SLICEM中每个LUT6的输入多了一个DI信号,并且CE信号中引入了WE控制。(两者区别,笔者并未在图中标出,不过仔细对比下两者的结构示意图,还是可以看出来的。)

同时,继续放大 xc7a100tfgg676-2 (active) 在Vivado的Device视图并对比,可以发现SLICEM和SLICEL在Device视图上明显的区别就在于两者的LUT有所不同。

上图,是对 SLICE_X30Y78(SLICEM)的Device视图中的LUT6放大截图。

上图,是对 SLICE_X31Y78(SLICEL)的Device视图中的LUT6放大截图。

将上述两种LUT的结构进行对比,可得:

1、 相同点:都具有地址输入线(A1-A6),两个输出口(O5-O6)。

2、不同点:SLICEM的LUT6具有写地址输入线(WA1-WA8),写数据端(DI1 DI2),写使能端(WE),而SLICEL的LUT6没有。

这是由于以上的不同,才使得:

SliceL的LUT只具有存储数据的能力,只能作为ROM使用;

而SliceM的LUT还具备了数据写入的功能,可以作为分布式RAM或移位寄存器使用。

Ch.2: 7系列中的移位寄存器(Shift Registers)

-

移位寄存器(Shift Registers),仅在SLICEM中可用(Available in SLICEM Only)。

-

寄存器移位寄存器(Registers),

– 由一个或者多个触发器组合起来构成,可以存储一位或者N位二进制数据。 -

移位寄存器移位寄存器(Shift Registers),

– 则可以在移位脉冲作用下,将数据数据依次逐位右移或左移,并进行输出;

– 且数据的输入输出方式,既可以并行,也可以串行。

2.1 ··· 移位寄存器的应用

移位寄存器的应用:延迟或延迟补偿、同步FIFO和内容可寻址内存(CAM)。

2.2 ··· 移位寄存器

2.2.1 ··· 移位寄存器

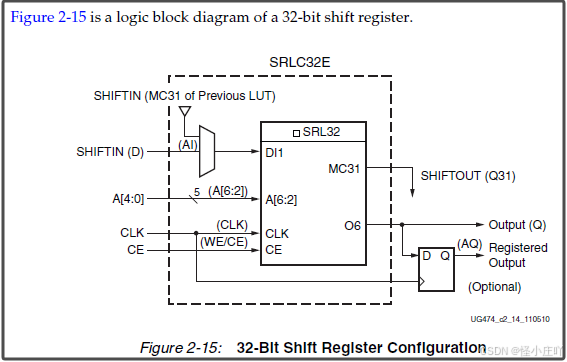

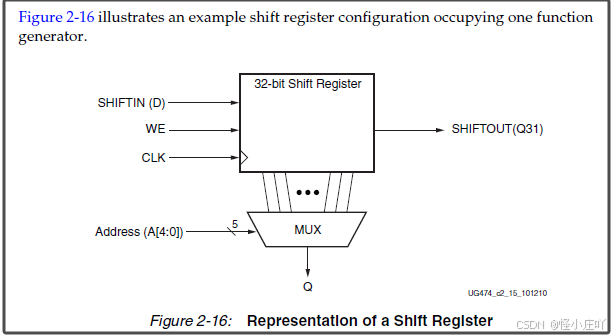

CLB中的SLICEM可以只使用一个LUT6配置出一个32位的移位寄存器,

而不使用Slice中的触发器( available flip-flops ),每个LUT可以将串行数据延迟1到32个时钟周期。SLICEM中的4个LUT级联,则可以实现最大延迟周期为128的延迟。

也可以把多个SLICEM中的移位寄存器进行级联,以获取更大的延迟或移位。

但是,Slices之间没有直接连接以实现更长的移位寄存器。

此图中,需要注意的是,SHIFTIN(D)和SHIFTOUT (Q31)为接连端口。

SHIFTIN(D)可以连接上一级的SHIFTOUT (Q31),SHIFTOUT (Q31)可以级联下一级的SHIFTIN(D)。但无法通过它们直接完成Slice之间的级联。

由级联产生的可编程延迟可用于平衡数据流水线的时序。

它支持最高32位的移位输出,可以选择普通数据(D)输入,也可以选择由上一级SRLC32E的SHIFTOUT作为输入。如果想用SRLC32E做12位移位输出,只需要将A[4:0]设置为5’d12,移位输出结果在SHIFTOUT口输出,与此同时O6也将会输出地址5’d12的结果,相当于一个32x1单端口DRAM(这地址是对于SRLC32E外部接口A[4:0]来说的,对于SRL32内部来说它是将高5位地址A[6:2]设为5’d12)。特别注意:SRLC32E只能在同一时钟域使用,不能做跨时钟域打拍使用,因为它内部移位操作不是用32个级联的触发器来做的,而是将上一级的电荷转移到下一级,如果第一级发生出现亚稳态,它将会一直传递到最后一级。(《FPGA从入门到精通(3) - DRAM》)

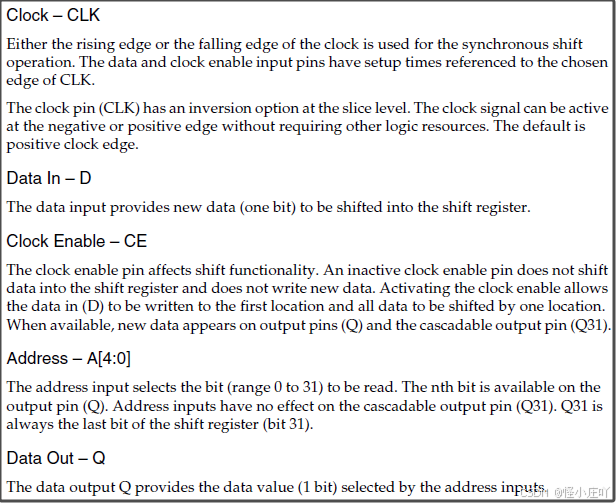

2.2.2 ··· 移位寄存器功能

移位寄存器的功能如下:

1、写操作:带有写使能(WE)的,与时钟(CLK)同步的同步写

2、通过Q31端口来固定的读取所移的数据位

3、动态读取:

– 3.1、5位地址总线,A[4:0]。

– 3.2、通过改变地址输入,在LUT的O6可以读取32位数据(O6,对应在原语上的Q)。

– 3.3、此功能对于创建较小的移位寄存器(小于32位)非常有用。

– 3.4、可以通过使用一个存储元件或触发器来实现同步读取数据

4、移位寄存器不支持复位/置位

其中,需要注意的是:

1)、LUT的最低位地址会被置1,也就解释了为什么6位地址输入的LUT会被配置成1到32个周期的移位寄存器,而不是1到64个周期的移位寄存器。同时,意味着五位地址的数值决定着移位长度。

2)、如果要进行同步读取数据,则将输出O6连接到一个FF中。(可以提升性能,但会增加一个时钟周期的延迟)

3)、移位寄存器不支持置位或复位,但在配置后可将其初始化为任何值。

2.3 ··· 移位寄存器的级联

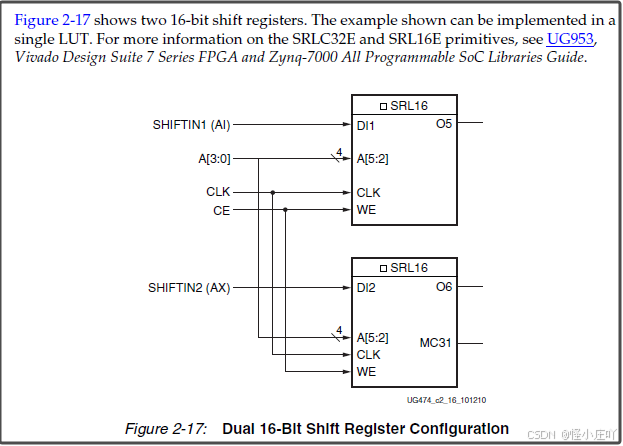

关于 SRLC32E 和 SRL16E,要看UG953。

上图中,除了SRL16的SHIFTIN不一样,其他端口都是共输入,尤其是地址位。所以,在这里,笔者认为,使用一个LUT6来实现两个SRL16也不是不行。(毕竟,一个LUT6可以看成两个LUT5嘛。)

上图中,除了SRL16的SHIFTIN不一样,其他端口都是共输入,尤其是地址位。所以,在这里,笔者认为,使用一个LUT6来实现两个SRL16也不是不行。(毕竟,一个LUT6可以看成两个LUT5嘛。)

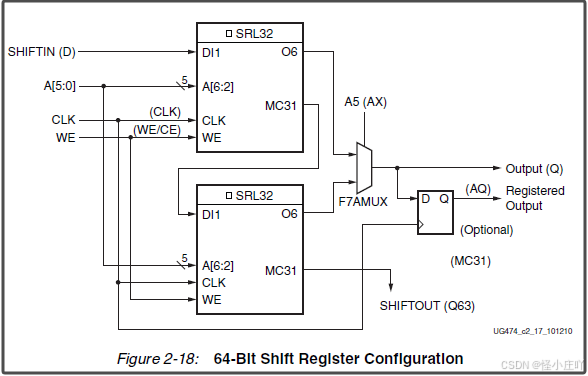

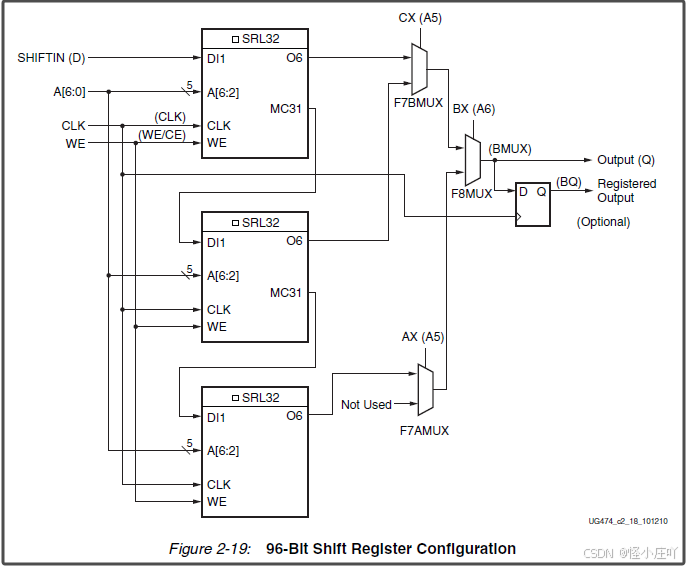

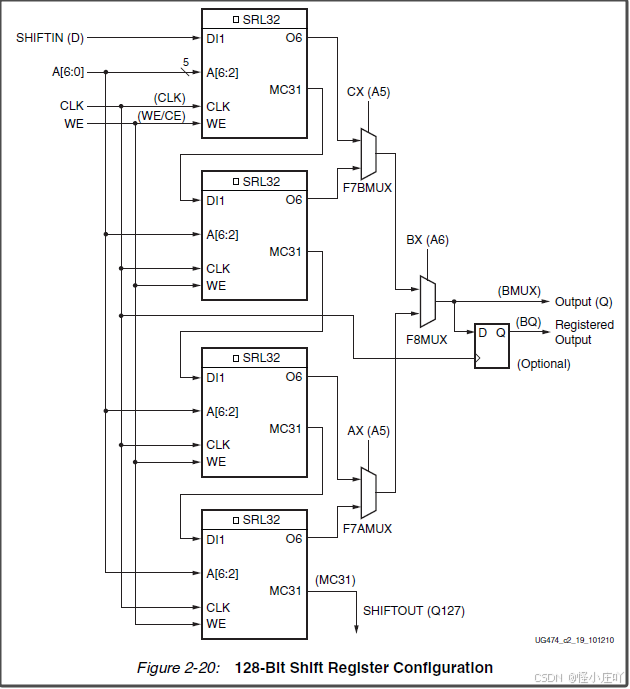

图2-18、2-19、2-20,展示了使用一个SLICEM时基于SRL32E的级联配置示意图,

上一级的MC31输出引脚直接连接到下一级的DI1输入引脚。

由于shift register chaining 和F7AMUX、F7BMUX and F8MUX multiplexers的存在,

在一个SLICEM中可实现128位的移位寄存器的可寻址访问。

可以通过多个SLICEM中实现长度超过128位的移位寄存器。

但是,不同SLICEM之间不能直接相连来实现它。

2.4 ··· 移位寄存器数据流

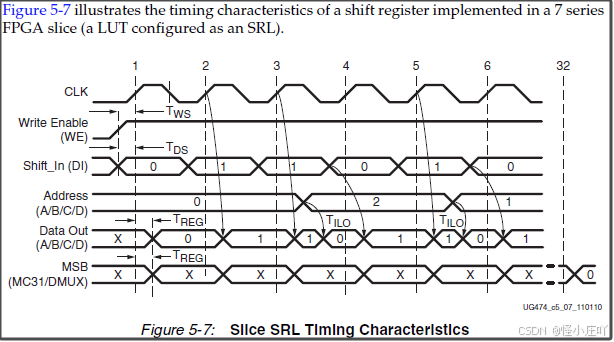

2.4.1 ··· 移位操作

2.4.2 ··· 动态读取操作

在动态读操作时,(移位长度不固定)

1、输出Q由5位地址决定

2、每当一个新地址到达时,在经过访问LUT的时间延迟后,输出Q变化

3、读操作是异步的,独立于时钟和时钟使能信号

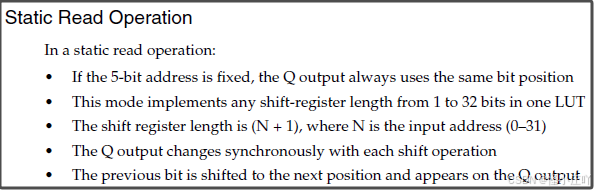

2.4.3 ··· 静态读取操作

在静态读操作时,(移位长度固定)

1、当5位地址固定时(地址固定意味着移位长度固定),输出Q使用相同的比特位

2、该模式在一个LUT中实现了从1到32位的任何移位寄存器长度

3、移位寄存器长度为(N + 1),其中N为输入地址(0-31)

4、输出Q与每一次的移位操作是同步的

5、前一位被移到下一个位置,并出现在Q输出上

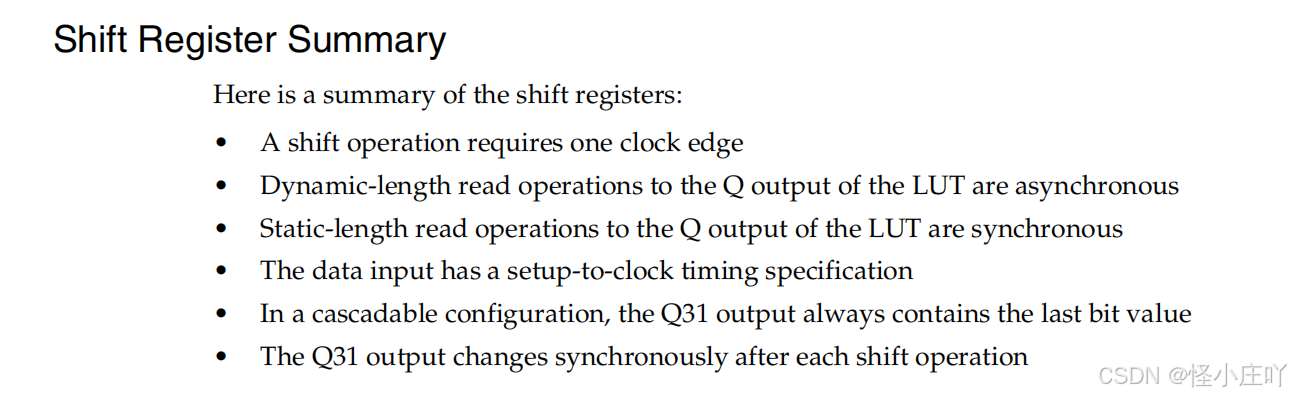

2.5 ··· 总结

这个移位寄存器的总结还不错,也简单易懂,直接放截原图了。

Ch.3: 补充

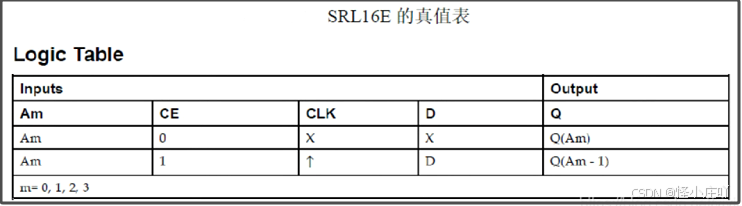

3.1 ··· SRL16E

3.1.1 ··· SRL16E真值表

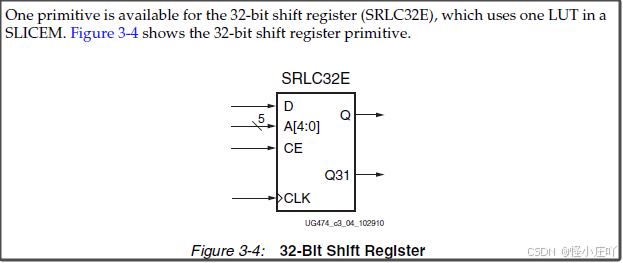

3.2 ··· SRLC32E

3.2.1 ··· 原语(Primitive)

官方文档ug474上有给出SRLC32E的原语

且端口说明如下:

看了一下,感觉和章节“1.2 ··· Shift register functions”中的内容大差不差。

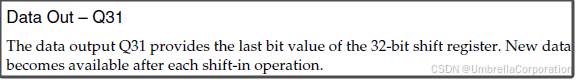

3.2.2 ··· SRLC32E的结构图

3.2.3 ··· 官方verilog原语描述

// SRLC32E: 32-bit variable length cascadable shift register LUT (Mapped to a SliceM LUT6)

// with clock enable

// 7 Series

// Xilinx HDL Language Template, version 2019.1

SRLC32E #(

.INIT(32'h00000000) // Initial Value of Shift Register

) SRLC32E_inst (

.Q(Q), // SRL data output

.Q31(Q31), // SRL cascade output pin

.A(A), // 5-bit shift depth select input

.CE(CE), // Clock enable input

.CLK(CLK), // Clock input

.D(D) // SRL data input

);

// End of SRLC32E_inst instantiation

3.3 ··· 移位寄存器应用

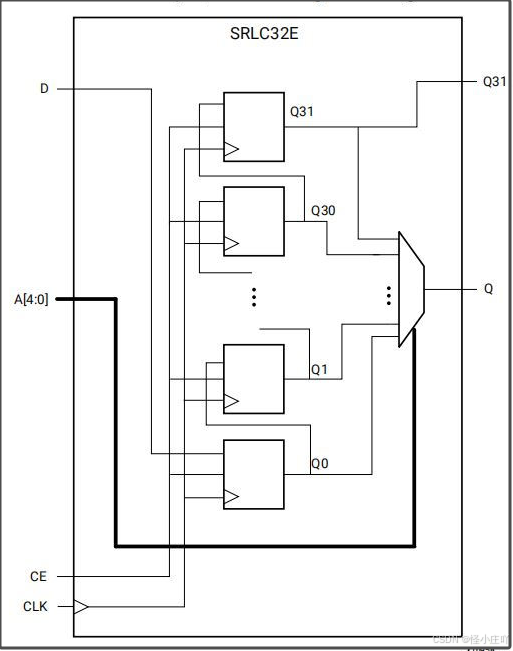

3.3.1 ··· 同步移位寄存器(Synchronous Shift Registers)

移位寄存器原语不使用同一个Slice中的可用寄存器。

为了实现一个完全同步的读写移位寄存器,输出引脚Q必须连接到一个触发器。

如下图所示,移位寄存器和触发器都共用同一个时钟。

3.3.2 ··· 静态长度移位寄存器(Static-Length Shift Registers)

可级联的32位移位寄存器实现了任何静态长度模式的移位寄存器,

不需要专用的多路复用器(F7AMUX、F7BMUX和F8MUX)。

下图,展示了一个72位移位寄存器。

只有最后一个SRLC32E原语需要将其地址输入与0b00111绑定。

另外,移位寄存器的长度可以限制为71位(地址与0b00110绑定),

并且可以使用一个触发器作为最后一个寄存器。

(在SRLC32E基元中,移位寄存器的长度 = 地址输入 + 1 )。

3.5 ··· 代码示例

在《FPGA原理与结构(5)——移位寄存器(Shift Registers)》中有看到Xilinx提供的代码示例:

- 32位移位寄存器verilog代码:

// 8-bit Shift Register

// Rising edge clock

// Active high clock enable

// Concatenation-based template

//

// File: HDL_Coding_Techniques/shift_registers/shift_registers-0.v

module v_shift_registers_0 (clk, clken, SI, SO);

parameter WIDTH = 32;

input clk, clken, SI;

output SO;

reg[WIDTH-1:0] shreg;

always @(posedge clk)begin

if (clken)

shreg = {shreg[WIDTH-2:0], SI};

end

assign SO = shreg[WIDTH-1];

endmodule

- 32位动态移位寄存器verilog代码:

// 32-bit dynamic shift register.

// Download:

// File: HDL_Coding_Techniques/dynamic_shift_registers/dynamic_shift_registers_1.v

module dynamic_shift_register (CLK, CE, SEL, SI, DO);

parameter SELWIDTH = 5;

input CLK, CE, SI;

input[SELWIDTH-1:0] SEL;

output DO;

localparam DATAWIDTH = 2**SELWIDTH;

reg [DATAWIDTH-1:0] data;

assign DO = data[SEL];

always @(posedge CLK)begin

if (CE == 1'b1)

data <= {data[DATAWIDTH-2:0], SI};

end

endmodule

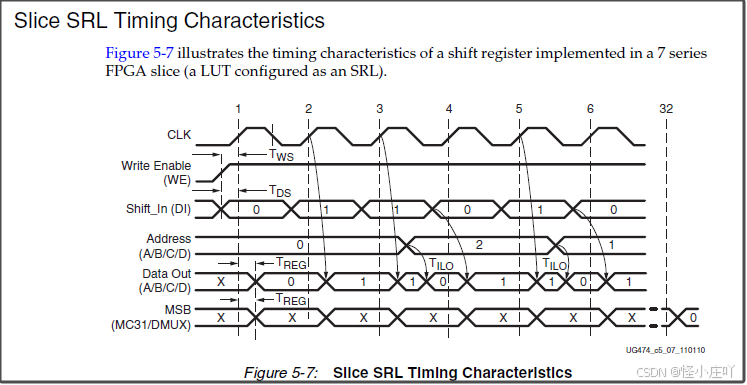

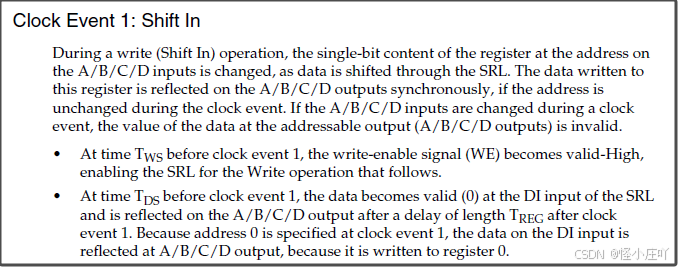

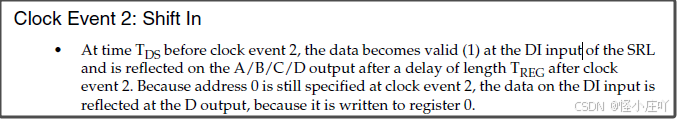

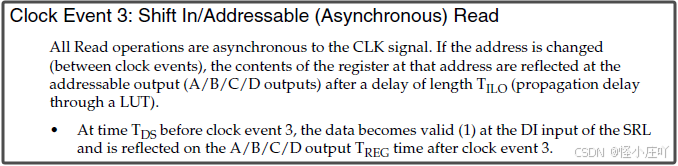

3.6 ··· Slice SRL时序特性(Timing Characteristics)

具体过程的原文如下,感兴趣的话,可以读读:

参考文献

1、《ug474_7Series_CLB.pdf》

2、《FPGA原理与结构(5)——移位寄存器(Shift Registers)》

3、《FPGA原理与结构(1)——可配置逻辑块CLB(Configurable Logic Block)》

4、《浅谈XILINX FPGA CLB单元 之 分布式RAM (Distributed RAM Available in SLICEM Only、RAM128X1D、Verilog原语描述)》

5、《浅谈XILINX FPGA CLB单元 之 移位寄存器(移位寄存器、SRLC32E、SRL16E)》

6、《FPGA从入门到精通(3) - DRAM》,这篇挺好

503

503

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?