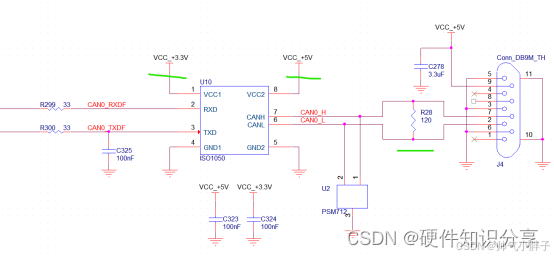

测试CAN物理层和数据链路层时,归结到最底层 ,在默认原理图没有问题的前提下,最好先检查一下PCBlayout。避免最底层的设计失误,导致物理层,和数据链路层测试结果出现偏差。

也可以在测试中发现问题后,返回来排查layout是否合规。

| 设计要求 | 解释 | 检查要求 |

| CANH和CANL在PCB上的长度应该相同 | 也就是对称性的要求 | 分别量取CAN_H和 量取 |

| 信号线长度尽可能短 | 以增强抗干扰性。在某些情况下,可以放宽对阻抗控制的要求, 适当加粗走线以提高信号的稳定性。 | 尽可能短?该如何判断 |

| 信号线应以最小距离对称布置 | 以减小信号之间的串扰。 串扰水平取决于两条走线之间的长度和距离 | 最小距离怎么判断? |

| 信号线不得有90度角。相反,应该使用两个45°代替 | 这在各种PCB设计指南中都是强烈要求的, 因为高频和高速的信号传输线需要保持特性阻抗一致, 并且在传输线的角部使用90°角路由,将改变线宽。 90°角处的线宽约为正常线宽的1.414倍。 因为线宽变化,会引起信号反射。 同时,拐角处的额外寄生电容也将导致耗时的信号传输,延迟影响 | 检查CAN总线上,有没 有90°的 |

| 信号线不应使用过孔 | 过孔本身会带来寄生电容和寄生电感,过孔打的越多所带来的 寄生电容和寄生电感的值也越大。 所以,这就是为什么很多 数据手册上面会写我们布线时过孔的数量不能超过多少个, 一般我们的高速信号线采取不能超过三个过孔的原则, 能不打孔就不打孔 | 按照要求检查 穿孔数量<规定数 |

| 信号线不能相互交叉 | 可能会产生电磁干扰(EMI)和串扰(crosstalk),从而导致 信号失真和噪声。 为了避免这些问题,通常会采用以下方法 来避免线交叉: 使用地平面层和电源平面层来隔离信号线, 以减少EMI和串扰的影响。 将信号线排列在同一层,并使用 交错排列(serpentine routing) 或差分线路(differential routing)来避免线交叉。 | |

| 在总线收发芯片和连接器之间不得放置其他IC芯片 | 目视检查 | |

| 共模电感应放置在收发器附近 | 具体参数,如不得>多少mm, 具体参照layout设计标准 | 如果没有具体标准, 至少应该以“收发器”和 “连接器”之间为参考, 本例中共模电感不能 距离连接器更近。 这也算一个评判标准 |

| 终端电阻应放置在收发器附近 | 具体参数,如不得>多少mm, 具体参照layout设计标准 | 同上 |

| 电容应放置在连接器附近 | 具体参数,如不得>多少mm, 具体参照layout设计标准 | 同上 |

| 齐纳二极管应放置在连接器附近 | 具体参数,如不得>多少mm, 具体参照layout设计标准 | 同上 |

| CAN控制器和总线收发器之间的RxD和TxD线应较短 | ||

| RxD和TxD线不能交叉 | ||

| 避免TxD与Vcc短路 | ||

| 避免RxD与GND短路 | ||

| 避免RxD和TxD短路 | #NAME? |

2595

2595

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?