说在开头:关于赫兹

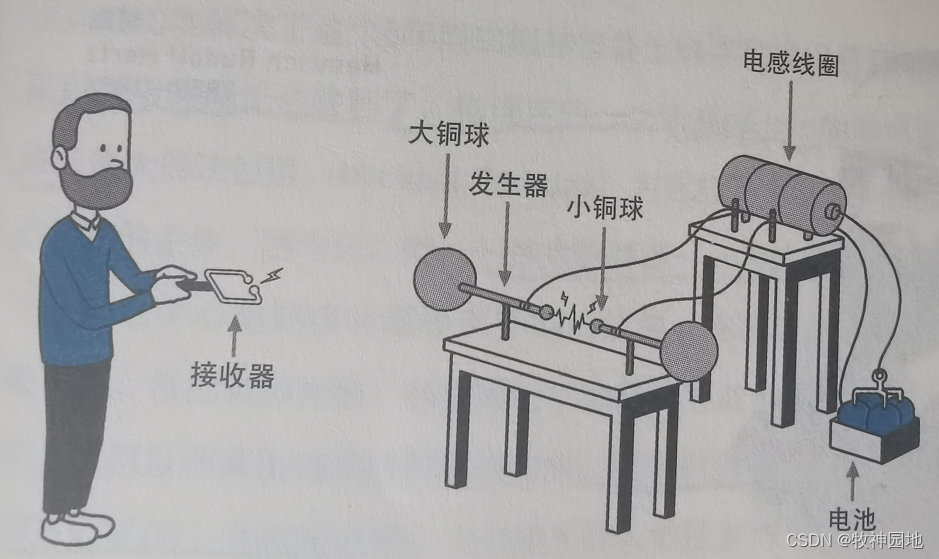

30岁的海因里希.鲁道夫.赫兹站在卡尔斯鲁厄大学的一间实验室里,专心致志地摆弄他的仪器。赫兹的装置很简单:一个电火花发生器,有两个大铜球作为电容,并通过铜棒连接到两个相隔很近的小铜球上;导线从两个小球上伸展出去,缠绕在一个大感应线圈的两端,然后又连接到一个电池上,将这套装置连成一个整体。

赫兹全神贯注的注视着两个几乎紧挨在一起的小铜球,然后合上了电路开关,顿时无形的电流穿过装置里的感应线圈,开始对铜球电容进行充电,赫兹注视着他的装置,在心里想象着电容两端电压不断上升的情形,他知道:当电压上升到2万伏特左右,两个小球之间的空气将会被击穿,电荷就可以从中穿过,往来于两个大铜球之间,从而形成一个高频的振荡回路。果然过了一会,随着细微的响声,两个铜球之间发出一束蓝色的电花(如果是我,就会被这束电花吓晕);赫兹赶紧跑到窗口,将窗帘拉上,同时关掉实验室的灯。

他这次实验的目的,不是要看这个装置如何产生火花短路,而是为了求证那虚无缥缈的“电磁波”的存在。那东西看不见摸不着,是啥玩意啊?如果麦克斯韦是对的,那么每当发生器火花放电的时候,在两个铜球之间会产生一个振荡的电场,同时引发一个向外传播的电磁波。在不远处的长方形铜环,接口处也各镶嵌了一个小铜球,那是电磁波的接受器。如果电磁波真的存在,那么接收器会感应出一个振荡电动势,从而在接收器的开口处也同样激发出电火花。赫兹睁大了双眼,忍不住要大叫了起来,他刚刚似乎看见在两个铜球之间产生了一个微弱的火花。一次,又一次,赫兹终于确定不是幻觉。整个接收器是一个隔离系统,没有电池也没有任何能量来源,赫兹不断重复这放电过程,每一次火花都听话地从接收器上被激发出来。

麦克斯韦胜利了,物理学的一个新高峰:电磁理论终于被建立了起来。赫兹为这座大厦封了顶。麦克斯韦的预言得到了证实:原来电磁波一点都不神秘,我们平时见到的光就是电磁波的一种,只不过普通的频率正好落在某一波段范围内,而被我们眼睛所感知而已。赫兹终于给争论已久的光本性问题,定下了一个似乎不可推翻的定论。电磁波的反射、衍射和干涉实验很快就做了出来,这些实验进一步地证实了电磁波和光波的一致性。

赫兹是那种纯粹的科学家,把真理的追求当做人生最大的价值。1887年10月,基尔霍夫大师在柏林去世,赫兹的老师亥姆霍兹强烈推荐他成为那个职位的继任者,但是赫兹拒绝了,在他看来柏林的喧嚣并不适合他,1894年年仅37岁的赫兹英年早逝,离开了这个奇妙的世界。而赫兹的名字已经成为了“频率”这物理量的单位,被每个人不断提起。

19世纪末,物理学征服了世界,它的力量控制着一切人们所知的现象。牛顿力学制定了从宇宙天体到地上物体的运动规律,在光学方面,波动已经统一了天下,而电磁理论更是将它扩大到了整个电磁世界;在热力学方面,热力学三大定律已基本建立;而在克劳修斯、范德瓦尔斯、麦克斯韦、玻尔兹曼等天才的努力下,分子运动论和统计力学也被成功的建立起来。而且这些理论都是彼此相符而相互包容,成为了一个经典物理的大同盟。物理学家们开始相信,这个世界所有的基本原理都已经被发现了,物理学已经尽善尽美,它已走到了自己的极限和尽头,再也不可能有任何突破性的进展了。普朗克的导师甚至劝他不要再浪费时间去研究这个高度成熟的体系。

19世界末的物理学天空中闪烁着金色的光芒,象征着经典物理帝国的全盛时代,这样伟大的时期在科学史上是空前的。但这个统一而又强大的帝国注定只是昙花一现,终究会像泡沫一样被破灭。(参考自:曹天元-上帝掷骰子吗)

四,电源分配网络设计

首先电源分配网络电阻非常重要:它决定着电源分配网络的通流能力,我们必须保证在最大负载电流下提供给器件的电压不超过其允许的DC电压范围。

——举个栗子:3.3V电源,电源电压范围:2.97V~3.63V。

其次电源分配网络阻抗的设计主要分成两部分:耦合电容设计和寄生电感设计。

我们接下来将从电容和电感两部分出发,详细分析如何实现一个良好的电源分配网络阻抗。

- 板级滤波电容设计

对于硬件工程师来说,最直观的解决电源噪声最重要的解决途径就是叠积木:放置更多更大的旁路/耦合电容,一个10uF不够,那就放两个或改成47uF;一个100nF解决不了,那就再加一个10nF。

那到底是不是加的越多越好么?如果板上已有100nF电容我们是加相同容值的100nF还是10nF更好,或则还是加100nF、10nF无所谓呢?

1. 1 电容并联谐振

首先,无论是电源模块或是某一个滤波电容器,都不可能提供从低频到100MHz全频段的低阻抗;我们从去耦电容模型的阻抗曲线可以清楚看到,电容器在低频和高频时(相对于自谐振频率点)都会呈现出高阻抗特性。

我们要设计实现电源分配网络阻抗曲线的策略就是:选择合适容值和个数的电容器,实现单板电源网络阻抗低于目标阻抗。

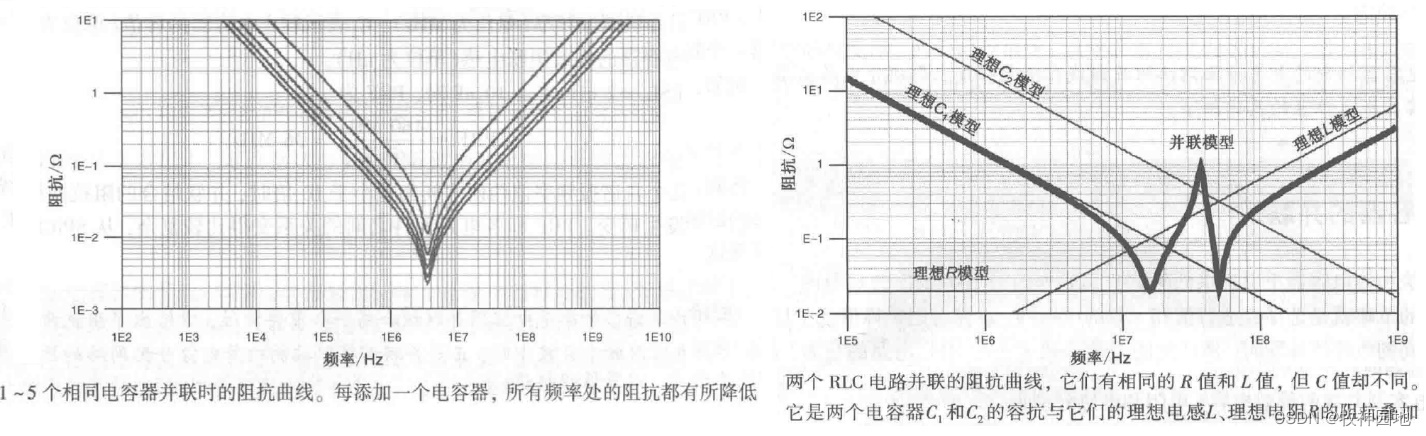

1. 如下左图所示,多个相同电容并联时产生的阻抗等效于RLC电路的行为,等效电容:Cn=n*C;等效电阻:ESRn=(1/n)*ESR;等效电感:ESLn=(1/n)*ESL;我们看到此时自谐正频率点保持不变,阻抗随频率的曲线趋势保持不变,形成整体电容的阻抗曲线下移的效果。

2. 如下右图所示,当两个不同电容器容值并联时,在各自谐振频率处有相同低阻抗下冲,在谐振频率之间有一个新的特性(阻抗的峰值),称为并联谐振峰值,发生在并联谐振频率(PRF)处;

两个不同容值的电容并联出现了一个奇怪的现象:并联谐振峰值;按理来说两个并联的阻抗至少比单个阻抗要更低(阻抗并联效应),但并联谐振峰值比两个电容正常阻抗值还要高;为什么会出现这个奇怪的谐振尖峰呢?

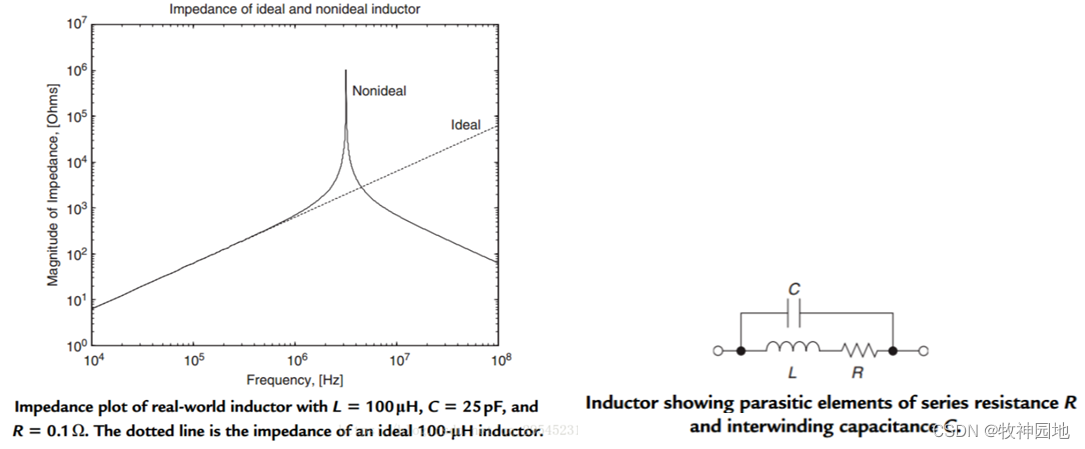

我们再来回顾一下电容模型的阻抗曲线:在自谐振频率点为界,电容在自谐振点左侧(低频)呈现容性,而在自谐振点的右侧(高频)呈现感性。大家再重新理解一遍:在自谐振点的右侧,该电容其实应该看成是一个电感。

理解了这个问题后,那么我们就可以来理解并联谐振峰值了,如下图是电感模型的阻抗曲线,看起来是不是跟并联谐振非常眼熟?的确,并联谐振峰值就是:大容值电容的寄生电感(ESL)和小容值电容并联组合起来的一个模型。

并联谐振频率是电容并联组合的一个重要特性,它给出了阻抗曲线的峰值位置,电容器较少时会制约单板电源分配网络的性能;并联谐振频率的值很难准确计算,它取决于:大电容C1的ESL1,小电容C2的容值和它们的ESR。如果两个电容的自谐振频率值相差很远,那么并联谐振频率值可以粗略的有下式决定: PRF ≈ (1/2)π*1/√(C2*ESL1) = 160MHz/√(C2*ESL1);并联谐振阻抗峰值粗略计算: Zpeak ≈ (L1/C2)*(1/(ESR1+ESR2))。

那如何有效降低并联谐振峰值阻抗呢?

1. 我们从并联谐振阻抗峰值计算公式上可得到:

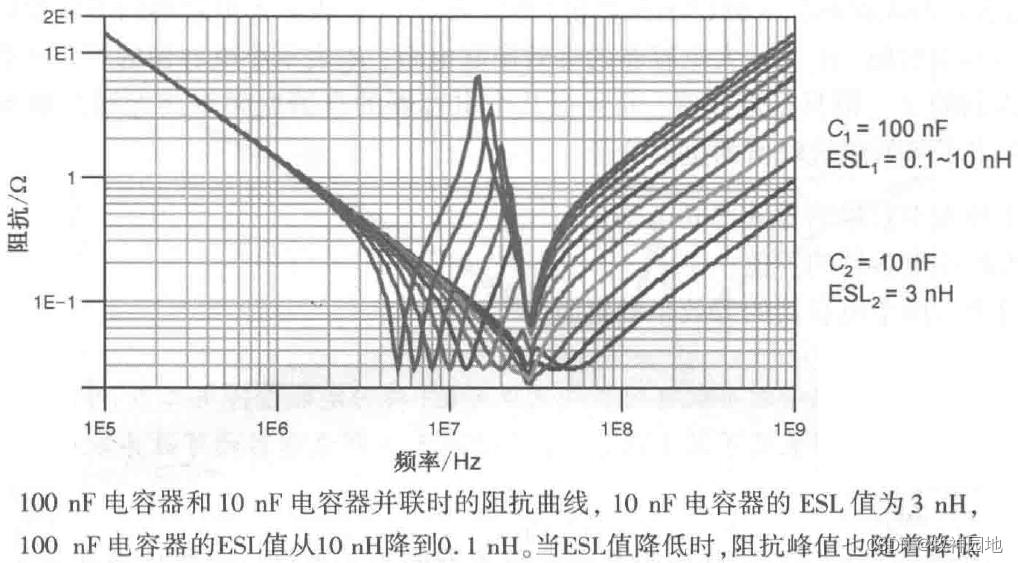

1, 减小较大电容器的等效串联电感;如下图所示;

2, 增大较小电容器的容值;

3, 增大两个电容器的等效串联电阻。

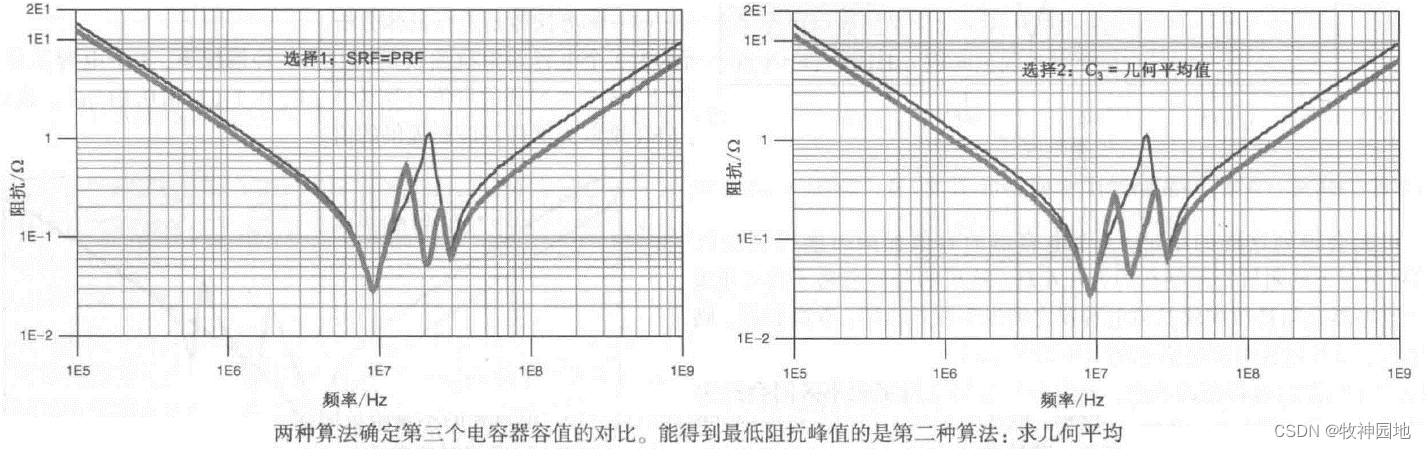

2. 并联谐振阻抗峰值也可以通过添加一个自谐振频率介于它们之间的电容加以降低:

1, 自谐振频率和并联谐振频率一致;

2, 自谐振频率值取为处于其他两个电容器自谐振频率值之间的某个值。

如下图所示,当每个电容器ESL相同时,设计添加一个容值为其它两个电容容值的几何平均的电容,以得到最低的阻抗峰值:C3= C1*C2。

从上述分析我们可以得到结论:

1. 当电源平面上滤波电容较少时,电容容值相差越大时,其并联谐振峰值阻抗就越大;

1, 可以通过减小大电容的ESL,增大小电容的容值C解决;

2, 或则可以通过增加一个几何平均容值电容来解决。

1.2 电容容值及数量的选择

在单板电源分配网络设计中:最重要的不是阻抗曲线有多低而是有多高,因为阻抗的高峰值会导致故障,所以单板电源分配网络应尽量控制高峰值。

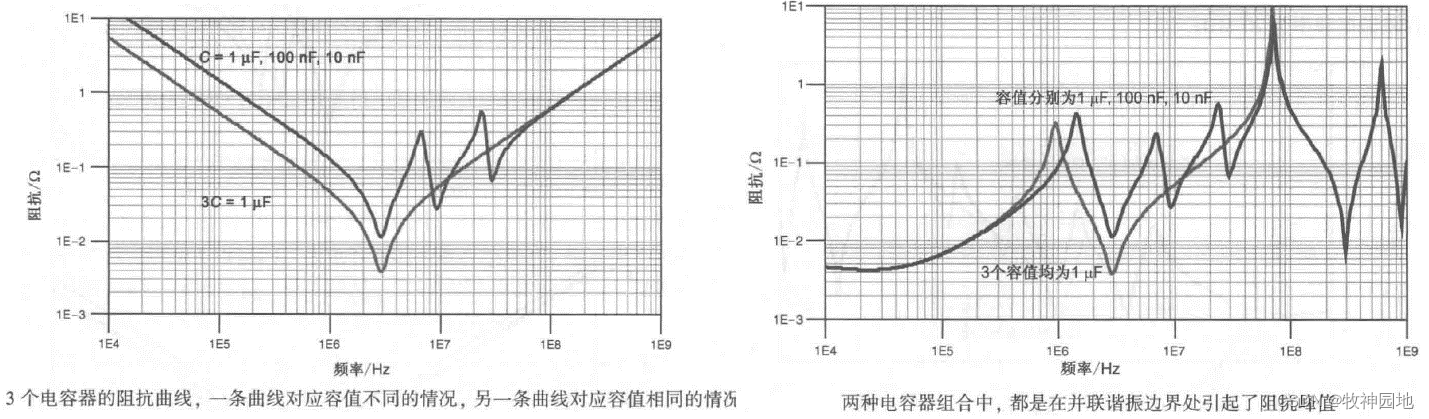

如下左图为3个相同容值1uF电容和1uF,100nF,10nF电容两种情况的阻抗曲线对比(无电源模块和平面电容的作用)。

如下右图为带电源模块,平面电容(边上5inch,厚度4mil)的综合仿真阻抗曲线:

1. 在低频时,滤波电容电感和小型陶瓷电容容值之间的相互作用,造成1MHz附近产生阻抗峰值,并联低ESL滤波电容来降低峰值(15nH->5nH);

——此时阻抗峰值在70MHz附近,如果该频率附近没有最坏情况电流,就不会引起问题。

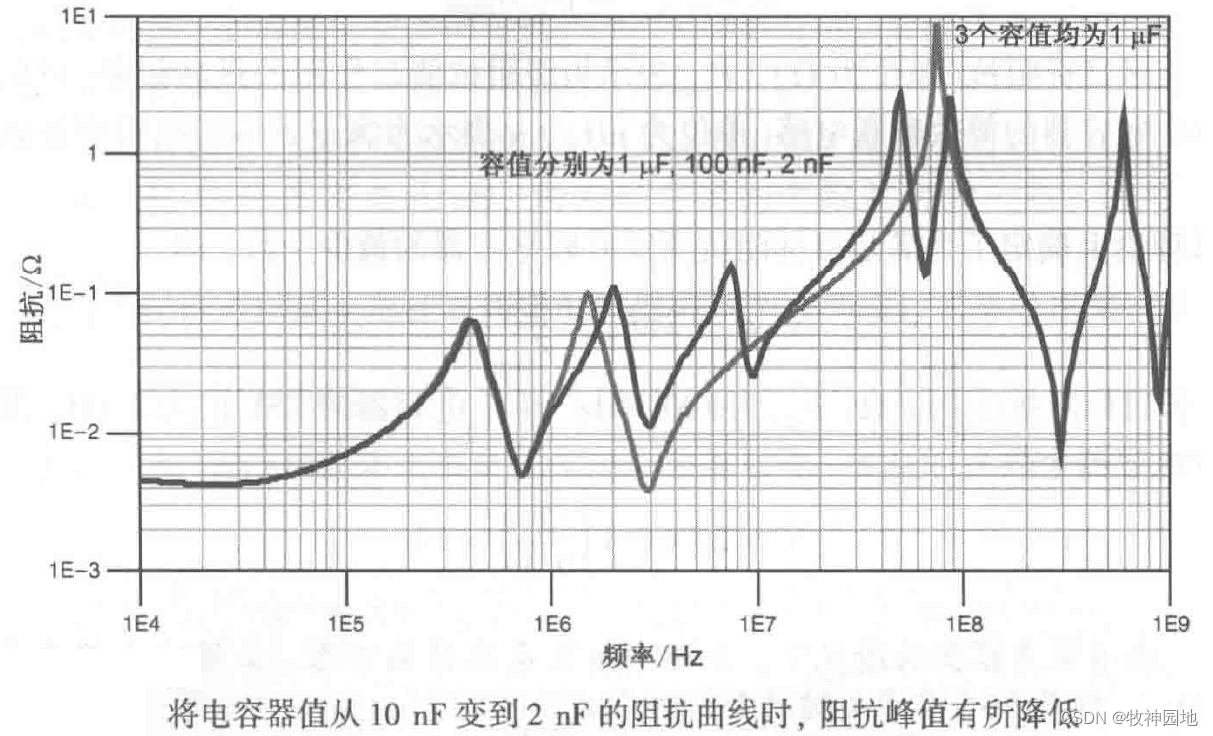

2. 如果70MHz处的阻抗峰值对单板工作造成影响;如下图所示,将1个电容值的自谐振频率调整到并联谐振频率(10nF->2nF),可以改善阻抗曲线,降低峰值阻抗(从10->2.5ohm),使噪声减小为原来的1/4。

——重新复习一遍电源分配网络设计准则:最重要的不是阻抗曲线有多低而是有多高!此时1uF、100nF、2nF的组合好于3个1uF的滤波方案。

电容数量的估算:在高频段时电容器组合可以获得的最低阻抗由其等效串联电感的并联值决定;假设ESL值相同,那么2π*ƒmax*(ESL/n) < Ztarget —> n > 2π*ƒmax*(ESL/Ztarget);在不考虑容值的情况下,减少所需电容个数,必须减小单个电容的ESL值。

重要的结论:如果平面电容容值远小于耦合电容容值,那么在高频时并联谐振阻抗峰值取决于耦合电容的并联感抗(ESL)与平面电容容值,与耦合电容容值无关,所以选用10nF或是100nF有同样ESL的电容,对高频峰值阻抗影响不大。

1.3 电容设计综合选择

一组电容在高频时的阻抗与并联后的电感有关(电容模型高频段),平面电容的容值和耦合电容的并联寄生电感决定了板级最高频率处的并联谐振阻抗峰值;通过挑选电容的容值可以补偿并联谐振,修整阻抗曲线,从而降低这组电容组合阻抗。

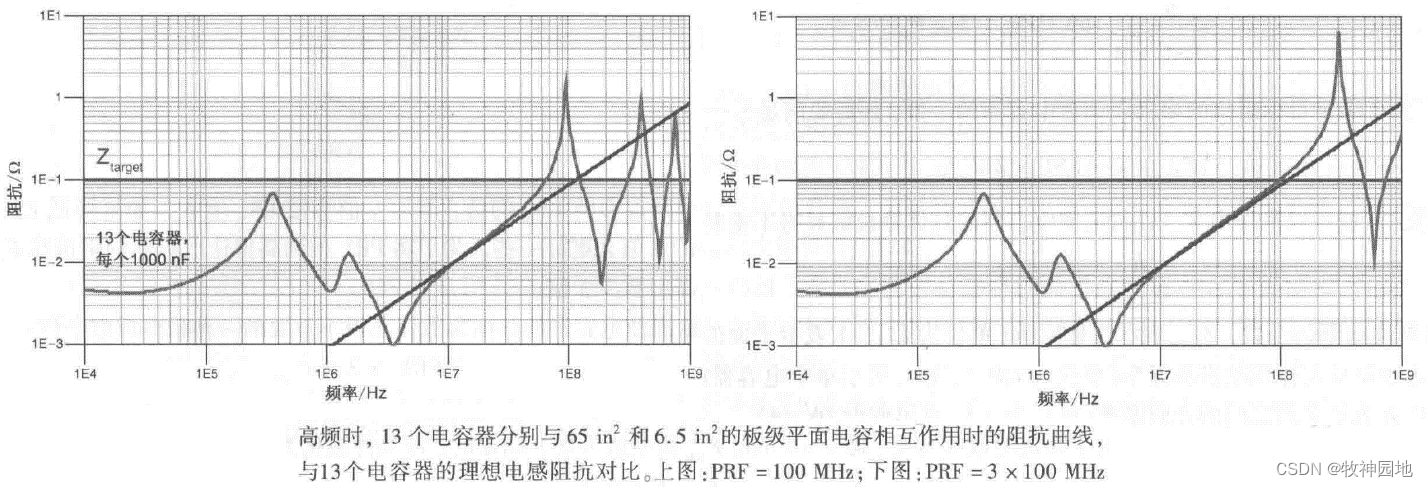

如下图所示,要求在0.1GHz(1E8)处达到0.1ohm目标阻抗,理论上的电容数量: n> 2π*Fmax*(ESL/Ztarget) = 2π*0.1*(2/1) = 13;理论上电容器的寄生电感与平面电容相互作用的PRF计算式为:PRF = 160MHz/√(C2*ESL1) =√[h/(1/n*ESL*A)] *160MHz;我们需要PRF > Fmax,那么有如下几种方法:1,增大n值;2,增加h;3,减小ESL值;4,减小A值。

同时为使PRF推到高得让电容的阻抗在ƒmax处低于目标阻抗,通常需要:PRF > 3 * ƒmax(经验值)。在Fmax处为了满足目标阻抗的要求而调整电容的个数,需要满足Ztarget=1/n * ESL * 2π * ƒmax;推导出:h/Ztarget > 56 *ƒmax。并联谐振频率足够大时,只需考虑电容并联ESL(电容数量)而不用关注电容容值大小。

由于板级电源分配网络只需要考虑100MHz以内(具体根据器件要求)频段的阻抗设计需求,所以从这个角度来分析:我们只需将高频段并联谐振频点推到3*ƒmax以上,那么就能保证在使用最少滤波电容的前提下(n = 2π*ƒmax*(ESL/Ztarget)),满足单板板级电源分配网络的设计。

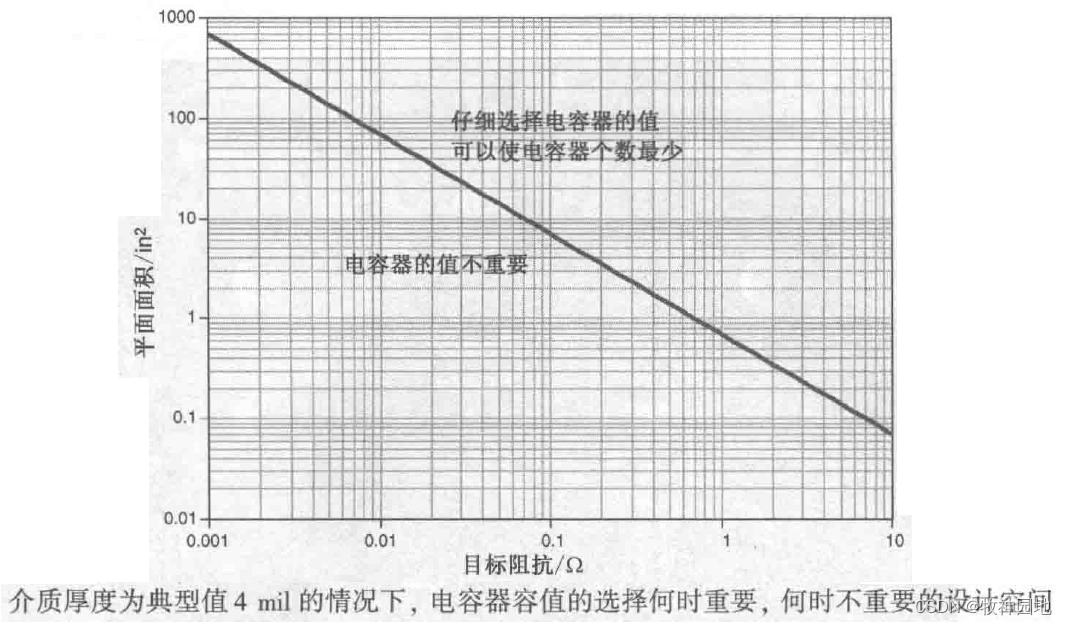

在典型应用情况下:h=4mil,ƒmax典型值为0.1GHz;推导的结论简化为:Ztarget * A < 0.7;电源平面面积设计空间与电容容值选择要求如下图所示:电源平面越大,那么越要选择合适的电容值用于压制并联谐振阻抗峰值。

1. 根据如上计算结论:Ztarget * A < 0.7,若目标阻抗为0.1ohm,那么只要平面面积小于7in²,电容器的容值就无所谓了;

2. 当平面面积大于7in²,平面的PRF推至0.1GHz附近,并使电容器组合的阻抗升高,这种情况下为了使用最少电容器,需要优化容值来修整阻抗曲线。

- 板级电源分配网络电感设计

电源分配网络电感是电源不能及时送达芯片(die)的根本原因,也是单板电源分布系统设计复杂的根源。单板电源分配网络路径上的电感:在PCB电源回路上,电容管脚上,芯片管脚上,过孔上等等;只要有电流流过的地方,那就一定会有电感!

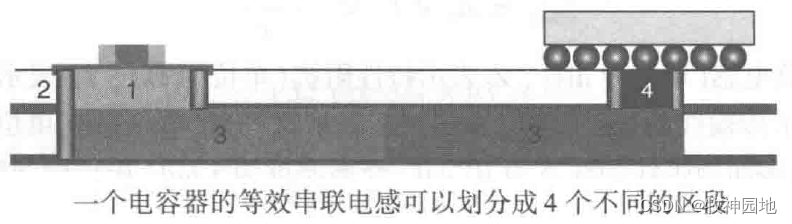

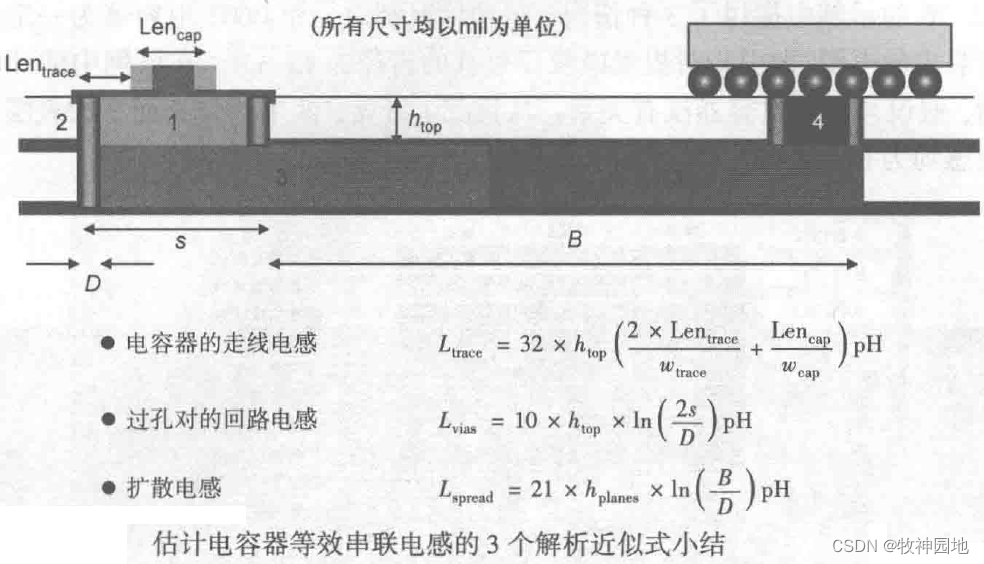

单板电源分配网络电感的组成如下图所示,球栅阵列封装焊盘流到电容器的完整电源及回流路径;电容器的等效串联电感值与路径设计有关,总共分为4部分:

1. 表面走线与平面腔顶层的回路电感,类似传输线的回路电感,其感值大小与回路面积成正比;

2. 电容器焊盘到腔平面几个过孔的回路电感,过孔电感大小与过孔的长度成正比;

3. 电容器过孔到球栅阵列过孔之间的扩散电感;

4. 封装下平面腔到封装引脚/焊球的回路电感。

2.1 回路电感模型

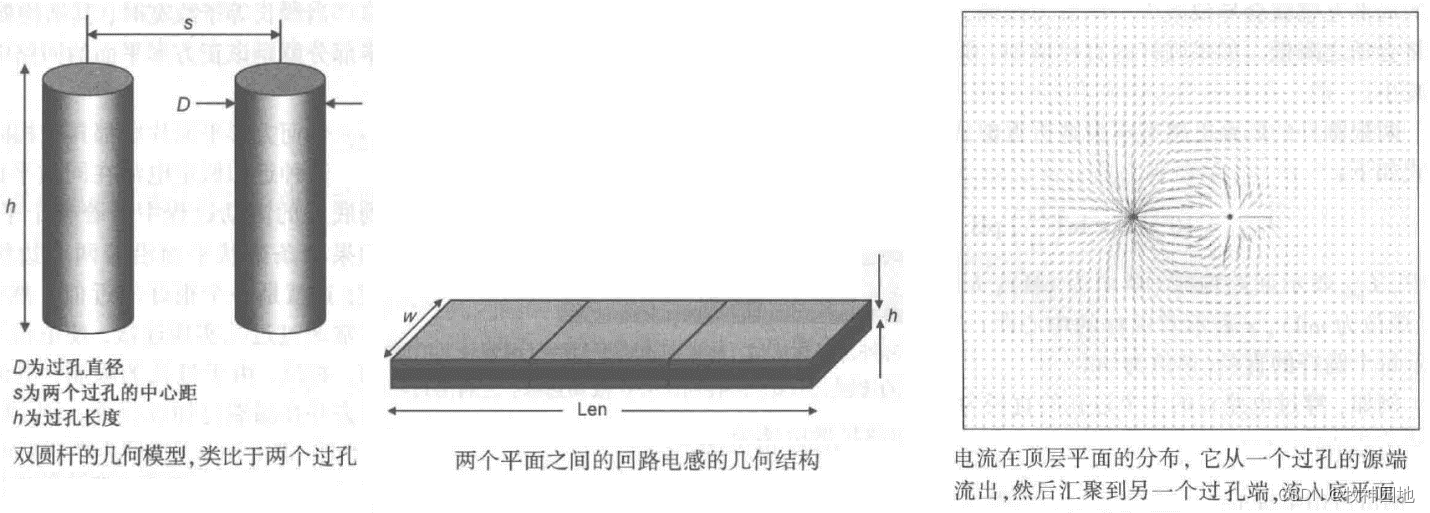

对如下少数几何结构的回路电感进行解析式近似求解:

1. 任何均匀的传输线,假设信号远端短路:LLOOP =Z0*TD=Z0*Len/v=50*Len/6=8.3nH/in*Len;

2. 双圆杆结构(如下左图,过孔),末端短路连接:LLOOP=10*h*ln(2s/D)pH;经验法则:一对过孔的回路电感值,粗略计算:21pH/mil;

3. 一对较长的中间有薄介质的宽导线:LLOOP=(32pH/mil*h)*Len/w pH;当线长等于线宽时,其结构是一个正方形,并且Len/w的比率为1,即每个方块的回路电感是:Lsquare = 32pH/mil * h;任何方形平面之间的介质越薄,方块回路电感越低;

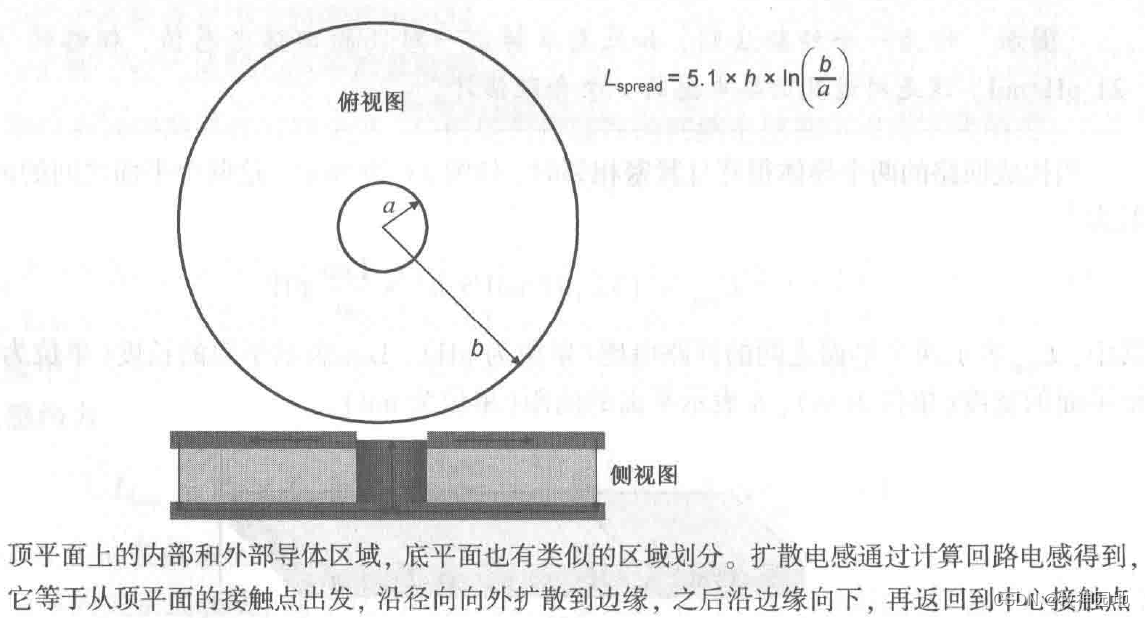

4. 平面上两个过孔接触之间的扩散电感:Lvia-via=21*h*ln(B/D)pH;

——其中:h:过孔之间介质厚度;B:过孔的中心距;D:过孔的直径;

——假设:过孔直径为10mil,相距1in,平面对间介质厚度h=10mil,那么: Lvia-via=21*10*ln(1000/10)=967pH ≈ 1nH;

5. 电流在同质平面上从顶层回到底层的流动过程中沿着整个平面均匀分布;如果两条带状平面沿着两个边缘实现整体对接,是一个很好的近似,但是平面通常通过过孔实现连接,使电流不能均匀流动,如下图所示为平面上两个过孔之间电流流动的情况;

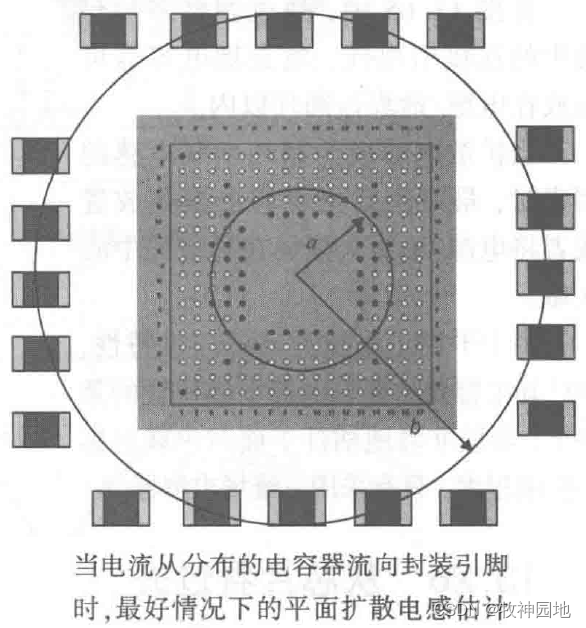

6. 电流从中心圆环接触点向对称的外层圆环接触点流动,然后向下流到底部平面,经内环接触点收缩后再返回;Lspread=5.1*h*ln(b/a)pH;假设过孔内半径5mil,外半径1in,平面介质厚度10mi,那么扩散电感为: Lspread=5.1*10*ln(1/0.005) ≈ 270pH。

2.2 电感的优化-电容安装优化

从上一节回路电感近似解给出了重要依据:

1. 减少电容器焊盘到过孔之间的走线回路电感,有3个重要设计调节方案:

1, 表层到电源/地腔顶平面的高度要短;

2, 表层走线要宽;

3, 表层走线要短。

2. 减少过孔的电感,有以下3个设计调节方案:

1, 表层到电源/地腔顶平面的高度要短;

2, 使用孔径很大的过孔;

3, 过孔之间尽量接近。

3. 减少平面回路扩散电感,有以下3个调节方案:

1, 电源/地腔之间的介质厚度要薄;

2, 使用孔径很大的过孔,或与腔有接触的多过孔;

3, 将电容器尽量靠近被去耦的封装。

总结如下几项对总回路电感影响最大的:

1. 表层到电源/地腔顶平面的高度要短:减小过孔电感和走线回路电感;

2. 电源/地腔之间的介质厚度要薄:减小平面回路扩散电感;

3. 表层走线要宽:减小走线回路电感;

4. 表层走线要短:减小走线回路电感。

- 板级电源谐振

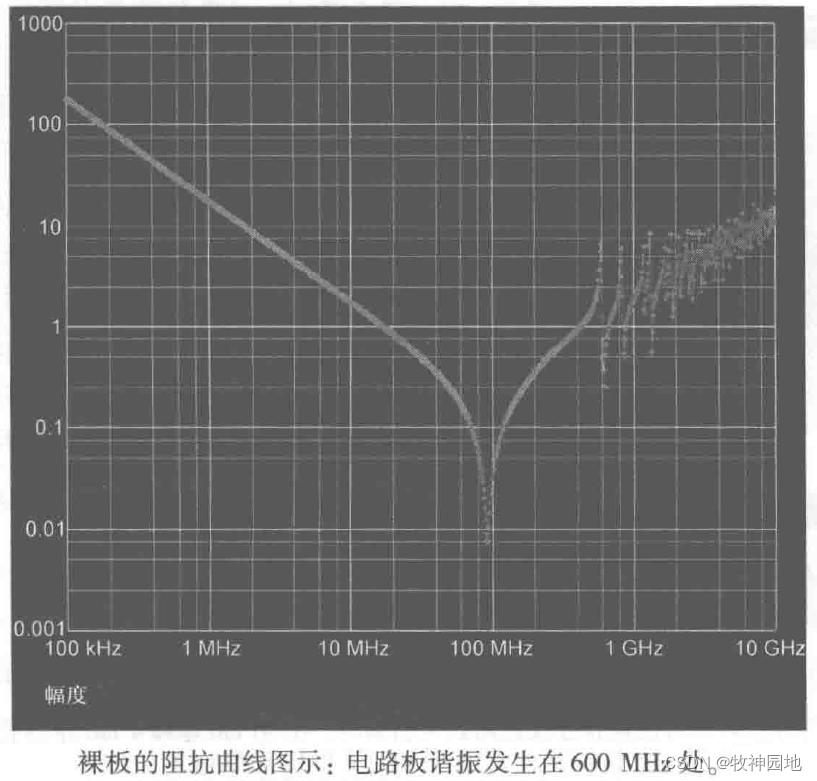

单板电源平面在整体上可以看成是一个LC的结构,所以在特定频率下会发生LC振荡,而在低于电容等效串联电感与平面电容并联谐振点的低频段范围,我们可以将平面看成集总元件与电容等效串联电感相互作用。当平面边沿长度等于波长的几分之一时,单板谐振特性会体现在阻抗曲线中:第一个谐振频率为波长的1/2:Len = 1/2*λ = 1/(2*DK )*C/ƒres = 1/2*v/ƒres =3/ƒres。

)*C/ƒres = 1/2*v/ƒres =3/ƒres。

——举个栗子,如下图为一个10in*10in尺寸的裸板阻抗仿真曲线,单板在低频时呈容性,计算第一个谐振频率点约为300MHz;由于电容的扩散电感取决于电容器与滤波器件的相对位置,如果探测点放在单板中间,那么扩散电感将会减半,第一个并联谐振频率点会是原来的2倍:600MHz。

对于器件管脚侧的电源滤波电容来说:

1. 去耦电容器距离芯片封装越远,扩散电感越大,总的串联电感就越大;

2. 当扩散电感远小于电容器的寄生电感,那么电容器的位置就不大重要,反之电容器距离远近就非常重要。

举个栗子:如果过孔直径是10mil,电容器与芯片相距1in,那么扩散电感:Lvia-via = 21*h*ln(B/D) = 21*h*ln(1/0.01) = 100pH;

1. 当介质厚度h较小时,扩散电感小,只有电容寄生电感很小才重要;

2. 当介质厚度h较大时,扩散电感大,电容寄生电感较小时电容位置就非常重要。

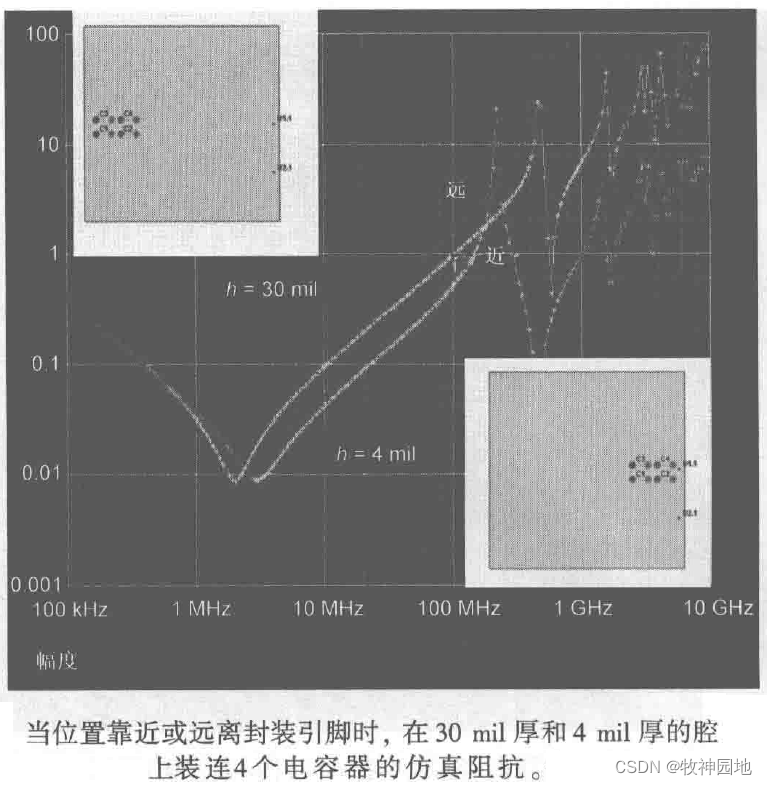

如下图为两个不同电容配置单板状况的阻抗曲线,都放置了4个相同的电容,每个电容器寄生电感为5nH;

1. 平面厚度为30mil,扩散电感为3nH,比4个电容并联寄生电感要大,电容放置远/近对阻抗曲线影响很大;

2. 平面厚度为4mil,扩散电感为0.4nH,比电容寄生电感小很多,电容位置对阻抗曲线变化很小。

所以,电容位置的重要性取决于扩散电容相较于电容本身寄生电感的大小:如果电源地平面距离很小,那么放远一点影响也不大,但电源地平面距离很大,那么需要尽量靠近器件电源管脚放置。

减小扩散电感的设计方法:

1. 在平面层间采用薄的介质;

2. 采用多层平面并联;

3. 使电源/地腔靠近板的顶层;

4. 电容沿着封装圆周长走向分布尽量开一些,如下图所示;

5. 封装下面单板底层放置一些电容。

那么,去耦电容是放在器件的同面不经过过孔滤波好,还是放在器件的背面直接打孔后滤波更好呢?这个涉及到了具体电源地平面间距,过孔长度,器件电源管脚与耦合电容距离等问题,在不同的条件下,会有不同的结论。但是一般来说:有足够多电容的情况下,最好在器件同层以及背面都放置一些去耦电容,以达到最好的滤波效果。

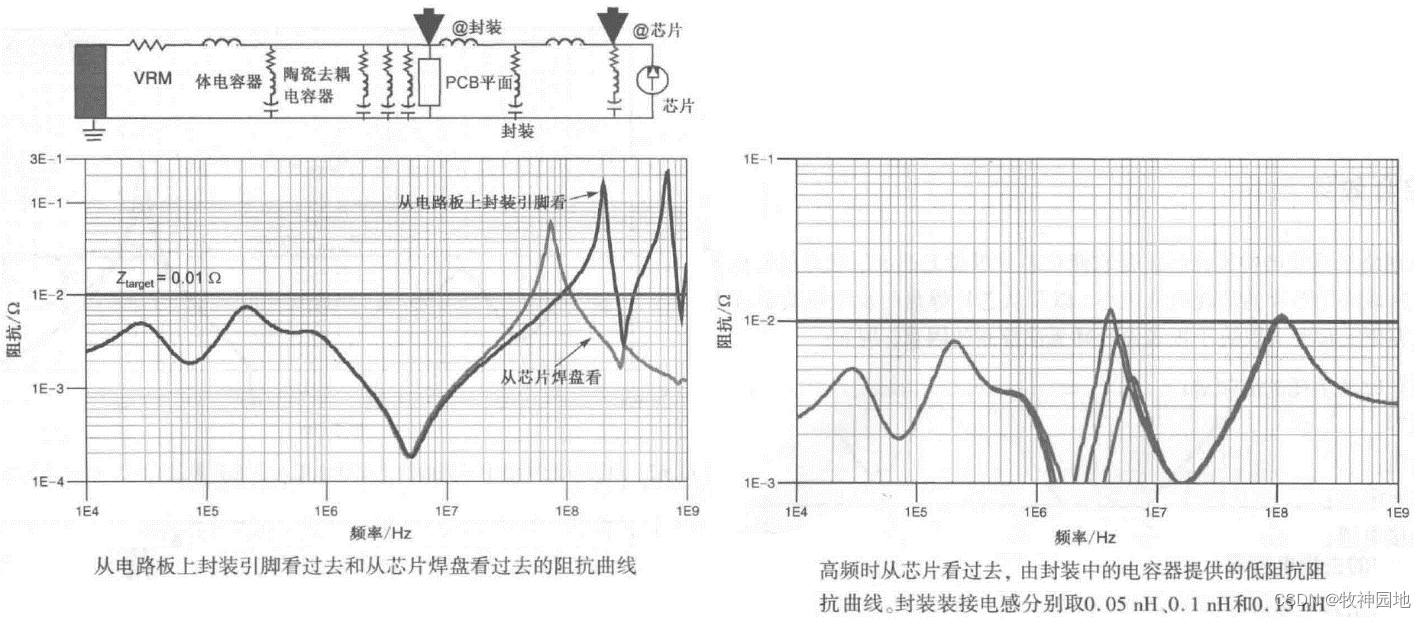

- 电源分配网络综合设计

电源分配网络的最终目的是要实现:提供芯片(die)管脚上电源的稳定供应。电源分配网络最重要的性能指标是:芯片(die)焊盘上把电压噪声保持在多低的电平上;这取决于:

1. 芯片对该电源消耗的电流大小;

2. 从芯片焊盘(die)向电源模块方向的阻抗曲线(满足目标阻抗);但有很多板级电源分配网络设计所无法控制的因素:

1, 芯片运行时所消耗的电流频谱;

2, 片上电容;

3, 片上电阻;

4, 芯片装接电感;

5, 封装装接电感;

6, 封装中的去耦电容。

所以板级设计中我们尽量寻找芯片和封装模型并纳入板级电源分配网络设计中,这是非常重要的;但是事实是:除了少数大器件可能会提供板级电源要求及模型外,大部分器件没有这方面信息。

如果封装中的去耦电容足够大,那么对板级去耦的需求会大大降低;而封装装接(管脚寄生)电感和目标阻抗大小决定了芯片看过去阻抗的最高频率。举个栗子,装接电感为0.1nH,那么Fmax = Ztarget/(2πLpkg) = 0.01/(2π*0.1) = 16MHz;所以我们可以看器件封装中如果采用了去耦电容及较大封装装接电感,那就意味着对板级去耦电容的降低。

实际上,一些对电源滤波要求较高的器件,一般会在器件资料中给出相应的参考设计(原理图,PCB),这通常是已经经过器件厂家验证过的相对安全的电源分配网络设计方案。我们可以参考并根据自己需求进行优化。

写在最后

个人认为单板硬件中最重要的设计就是:电源系统;同时这部分也是最容易出问题的。如何保证电源的安全可靠,是一个重要的课题。当然电源分配网络只是电源系统设计的其中一部分,电源系统还包括了更多的内容。正如我们开头将电源分配网络比作“物流公司”,它只负责将“包裹”按时送达各个器件,但它不负责“包裹”里货物是否满足要求,甚至送达的可能是“包裹炸弹”。

《信号完整性基础》专题全部结束了,但这并非是信号完整性学习的结束,而是刚刚开始哪,后续会有更多的专题内容是以信号完整性内容为基础的。我们只有对信号完整性有良好的感知,才能理解那些之前不能理解的一些东西。

本章部分相关内容和图片参考自:Eric Bogatin-《信号完整性分析》。下一专题《半导体基础:关于PN结的那些事》。

文章探讨了电源分配网络在电子设备中的重要性,特别是电容并联谐振现象及其对阻抗的影响,强调了选择适当电容容值和数量以降低谐振峰值的重要性。此外,还介绍了单板电源系统的设计准则和电感优化策略,包括减小回路电感和扩散电感的方法。文章最后指出电源分配网络是确保电源系统可靠性的一个关键环节,而信号完整性是理解电子设计的基础。

文章探讨了电源分配网络在电子设备中的重要性,特别是电容并联谐振现象及其对阻抗的影响,强调了选择适当电容容值和数量以降低谐振峰值的重要性。此外,还介绍了单板电源系统的设计准则和电感优化策略,包括减小回路电感和扩散电感的方法。文章最后指出电源分配网络是确保电源系统可靠性的一个关键环节,而信号完整性是理解电子设计的基础。

4155

4155

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?