目录

3.卡诺图(Karnaugh Map)判定Static Hazard是否存在

1.什么是Glitch?

A momentary unexpected output change ( short pulse ) when an input changes ;usually caused by gate propagation delays .

2.Static Hazard

Timing hazard和产开的那个hazard没有任何关系。它是指问题发生的过程(结果当然就是glitch)。分为两类:

Dynamic Hazard:a single input change,then output change more than once.

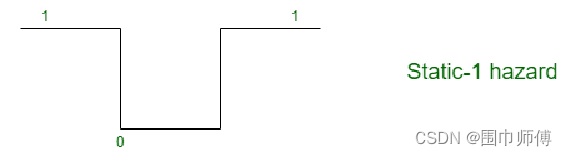

这里只关注第二种:Static Hazard,它也可以分为两种形式(也就是上面的两张图所示):

static-1 hazard: a pair of input combinations that:(i) differ in only one input variable;(ii) both give a 1 output;but momentary 0 output to occur during a transition in the differing input variable.由门OR、AND引起。即当电路输出处于1时,改变输入,但是这一前一后两种输入 只有一个变量发生了改变 (如0100变成0101),且理论上它们都只会使输出为:1。可是在两输入“交接”后,输出短暂地产生过:0。

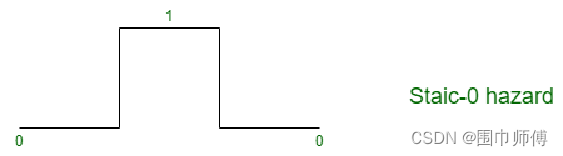

知道了static-1,也就知道了static-0:

static-0 hazard:a pair of input combinations that:

(i) differ in only one input variable;

(ii) both give a 0 output;

a momentary 1 output to occur during a transition in the differing input variable.由门NOR、NAND引起。

3.卡诺图(Karnaugh Map)判定Static Hazard是否存在

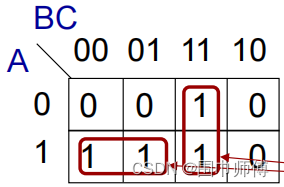

满足上述条件(i)(ii),只是说明static hazard有存在的可能,还并不能确定是否真的有。需要用卡诺图做最终的判断:

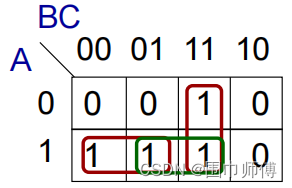

电路没有static-1 or 0的条件是:卡诺图F(or F’)中所有相邻的1(or 0,相邻指某一个的上下左右与其相接,斜对角不算)group 都共同圈在了至少同一个组里。

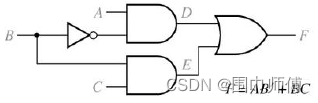

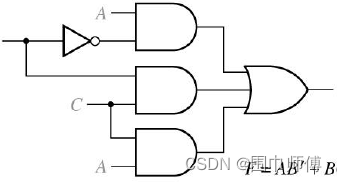

eg. 如下电路,逻辑式为F = AB’ + BC,显然它的卡诺图中两组1是分开的,所以它有static-1 hazard:

去除hazard的办法:加一组冗余组(redundant group),使三组间接相连;而逻辑式变为F = AB’ + BC + AC ,电路也相应做出变化:

所以对于一个电路,如果找不到两个输入组合同时符合条件(i)(ii),则一定没有static-1(or static-0)hazard。

反映到卡诺图(Karnaugh Map)上,就是F(or F’)所有的1(or 0)全不相邻,根本没法圈起来。

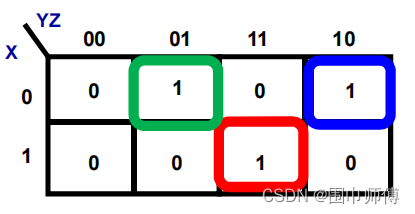

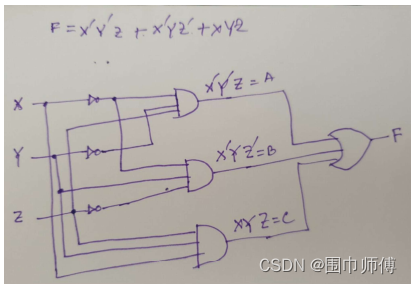

eg.对于逻辑式 F = X’Y’Z + X’YZ’ + XYZ = (X Y)’ Z + (X + Z)’ Y,卡诺图中的1’group全都不相邻,所以没有static-1 hazard,不符合条件(i)(ii)也证实了这一点。

但是0有很多是相邻的啊,有可能是static-0,那究竟是不是呢?

F = X’Y’Z + X’YZ’ + XYZ =((X’Y’Z + X’YZ’ + XYZ )’)’ = ((X+Y+Z’)(X+Y’+Z)(X'+Y'+Z' ))’,

F’ = (X+Y+Z')(X+Y'+Z)(Z'+Y'+Z'),画出F'的卡诺图(所以看的根本不是F中的0),根据电路逻辑图圈出所有的0,其实就是把F的卡诺图中,所有的0换成1,1换成0,很容易发现:请况和验证static-1的时候完全一样,static-0也是不存在的。

static-1和static-0 hazard必须同时存在或不存在于电路中,不可能在消除一个的同时保留另一个。

本文详细介绍了Glitch的概念,即在组合逻辑电路中由于输入变化和门延迟导致的短暂错误输出。接着阐述了Static Hazard,特别是Static-1和Static-0 Hazard,它们分别与OR/AND门和NOR/NAND门相关。通过卡诺图(Karnaugh Map)可以判断Static Hazard是否存在,消除这些潜在问题的方法是添加冗余组。文章最后通过实例展示了如何使用卡诺图分析并消除Static Hazard。

本文详细介绍了Glitch的概念,即在组合逻辑电路中由于输入变化和门延迟导致的短暂错误输出。接着阐述了Static Hazard,特别是Static-1和Static-0 Hazard,它们分别与OR/AND门和NOR/NAND门相关。通过卡诺图(Karnaugh Map)可以判断Static Hazard是否存在,消除这些潜在问题的方法是添加冗余组。文章最后通过实例展示了如何使用卡诺图分析并消除Static Hazard。

1056

1056

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?