文章目录

听歌

梦龙的Demons

【单曲循环】Demons- Imagine Dragons(梦龙)

前言

这些天在准备电赛,看到其它同学有在准备一些模拟滤波器,我想起来Vivado中似乎带有XADC以及FIR滤波器的ip核,只需要再准备一块DA模块来输出信号就可以组成一个数字FIR滤波器。查阅相关资料后感觉难度并不大,但实际开始调试时仍然遇到了许多问题折磨了我很久。网上很多资料都比较笼统,没有对各个信号的用法作说明,本文从一个第一次接触XADC和FIR核的小白视角来介绍一下它们的使用方法以及调试中的一些问题。

一、XADC核的配置以及使用方式

1.滤波的第一步我们需要把外界的模拟量转化为数字量,在这里我使用了Xillinx 7系列FPGA自带的XADC,当然如果你想外接其它AD模块也完全没有问题。在设置IP核时,主要关心以下几个配置。

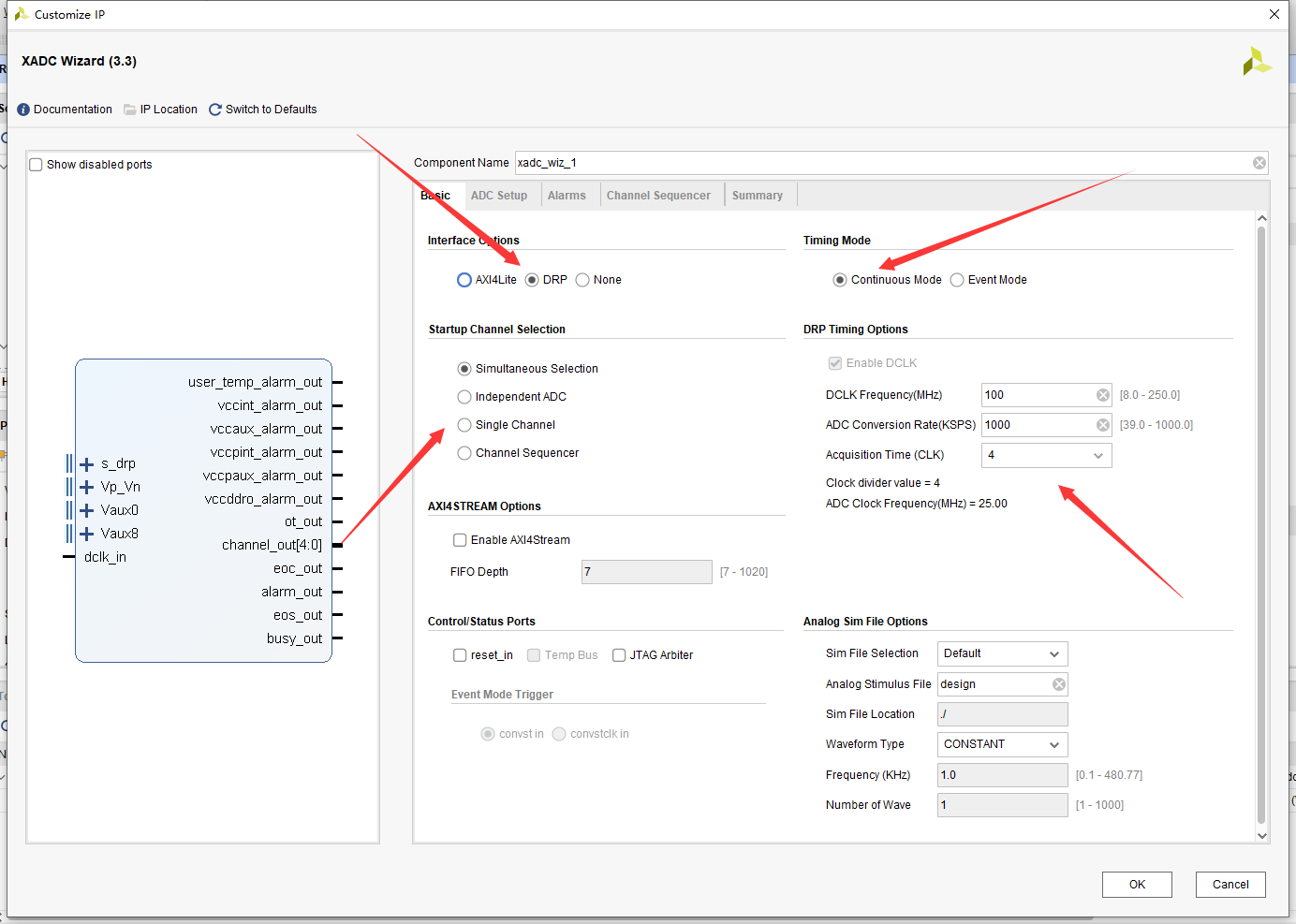

第一个标签页:

1.选择DRP模式,这个模式相对来说便于控制。

2.在Timing Mode中选择Continuous Mode,其意义是对信号持续进行采样。

3.选择Simultaneous Selection,这个选项可以使得XADC可以对多路信号进行采样,如果被采样的信号只有一路的话选择Single也没有问题。

4.然后设置系统的工作时钟以及采样率,XADC支持的最高采样率为1Mhz。

第二个标签页:

1.Channel Averaging指的是对输入的信号做平均运算,好处是使得输入的信号更加平滑没有毛刺,坏处是大大降低了采样率,会使高频信号失真。例如:输入信号为10KHz,不使用平均运算时每一个周期的信号会被采样1M/10K=100次,此时波形基本不失真,但如果对它做16位的平均那么该信号只相当于被采样了100/16次,显然波形会失真。在该数字滤波器的设计中我们选择None就可以了。

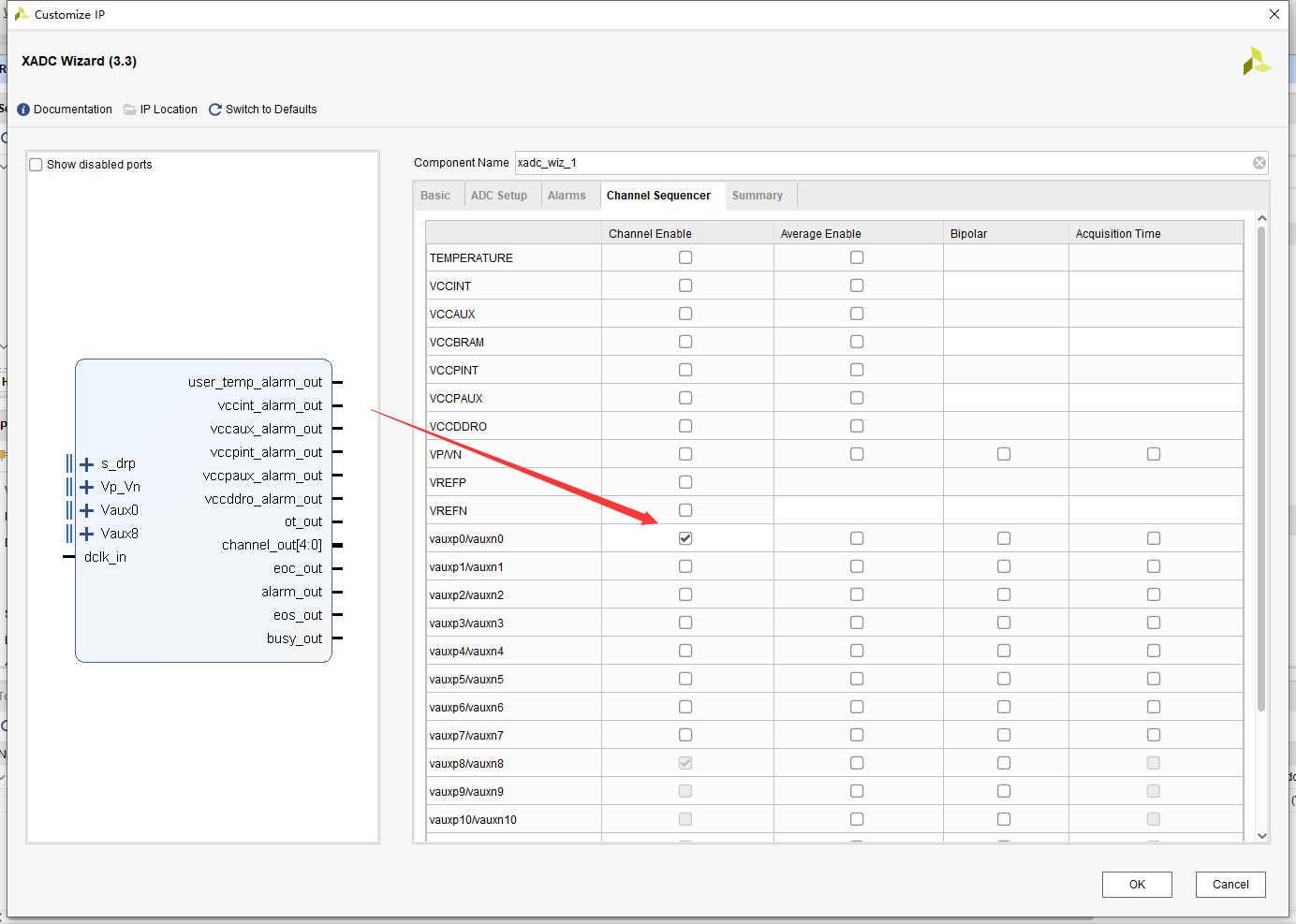

第三个标签页:

1.我只使用了一路信号输入,勾选va0通路即可。

编写XADC驱动:

XADC的驱动非常简单,只需要每隔一段时间拉高读使能端即可,代码放在文章的最后。到这里XADC的部分基本完成了。

例化IP核

XADC:

.di_in(di_in), // 写XADC的数据,不关心

.daddr_in(daddr_in), // 写XADC的地址,不关心

.den_in(den_in), // 写使能,不关心

.dwe_in(dwe_in), // 读使能,重要

.drdy_out(drdy_out), // XADC准备好数据候会拉高该信号,可用可不用

.do_out(do_out), // XADC输出数据,重要,输出的位宽是16位的,只需要关心高12位即可(官方数据手册宣称的12位ADC)

.dclk_in(dclk_in), // 系统工作时钟,重要,和配置IP时填写一致即可

.reset_in(reset_in), // 可用可不用

.vauxp0(vauxp0), //

.vauxn0(vauxn0), // XADC的通道,外部模拟信号就从这里输入

.user_temp_alarm_out(user_temp_alarm_out), // 以下信号不使用,但他们的功能其实很实用,感兴趣可以了解一下

.vccint_alarm_out(vccint_alarm_out),

.vccaux_alarm_out(vccaux_alarm_out),

.vccpint_alarm_out(vccpint_alarm_out),

.vccpaux_alarm_out(vccpaux_alarm_out),

.vccddro_alarm_out(vccddro_alarm_out),

.ot_out(ot_out),

.channel_out(channel_out),

.eoc_out(eoc_out),

.alarm_out(alarm_out),

.eos_out(eos_out),

.busy_out(busy_out)

二、FIR核的配置

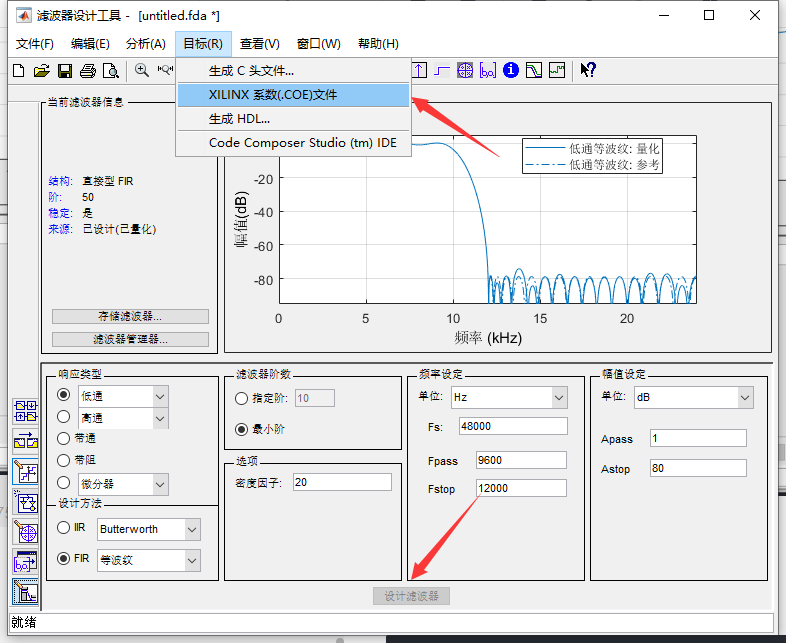

Vivado的FIR核不能够设计滤波器,但可以通过导入Matlab设计滤波器时生成的.coe文件来生成一个滤波器,步骤如下:

1.使用Matlab设计一个滤波器

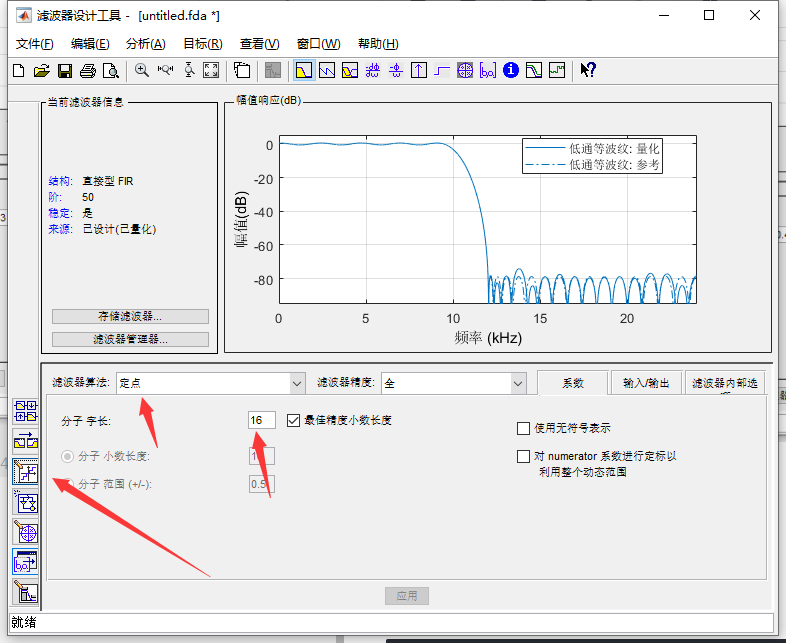

1.打开滤波器设计工具,设置好滤波器类型、通频带、截止频率等参数。

2.选择直接型FIR结构

3.设置量化方式

4.设计滤波器后生成.coe文件

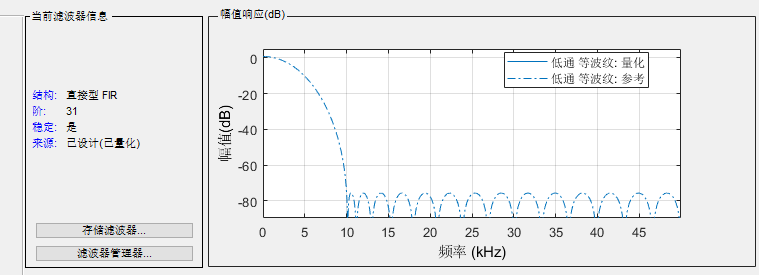

到这里滤波器已经设计完成了,有几个注意事项:一是设计方法并不一定要使用等波纹型,汉明窗等等也很好用。二是要按图中的的步骤将滤波器设计为定点、全精度、直接型FIR滤波器,否则无法生成.coe文件。第三是量化的分子字长和Fs这两个参数要记住,等会会用到。

2.配置FIR核

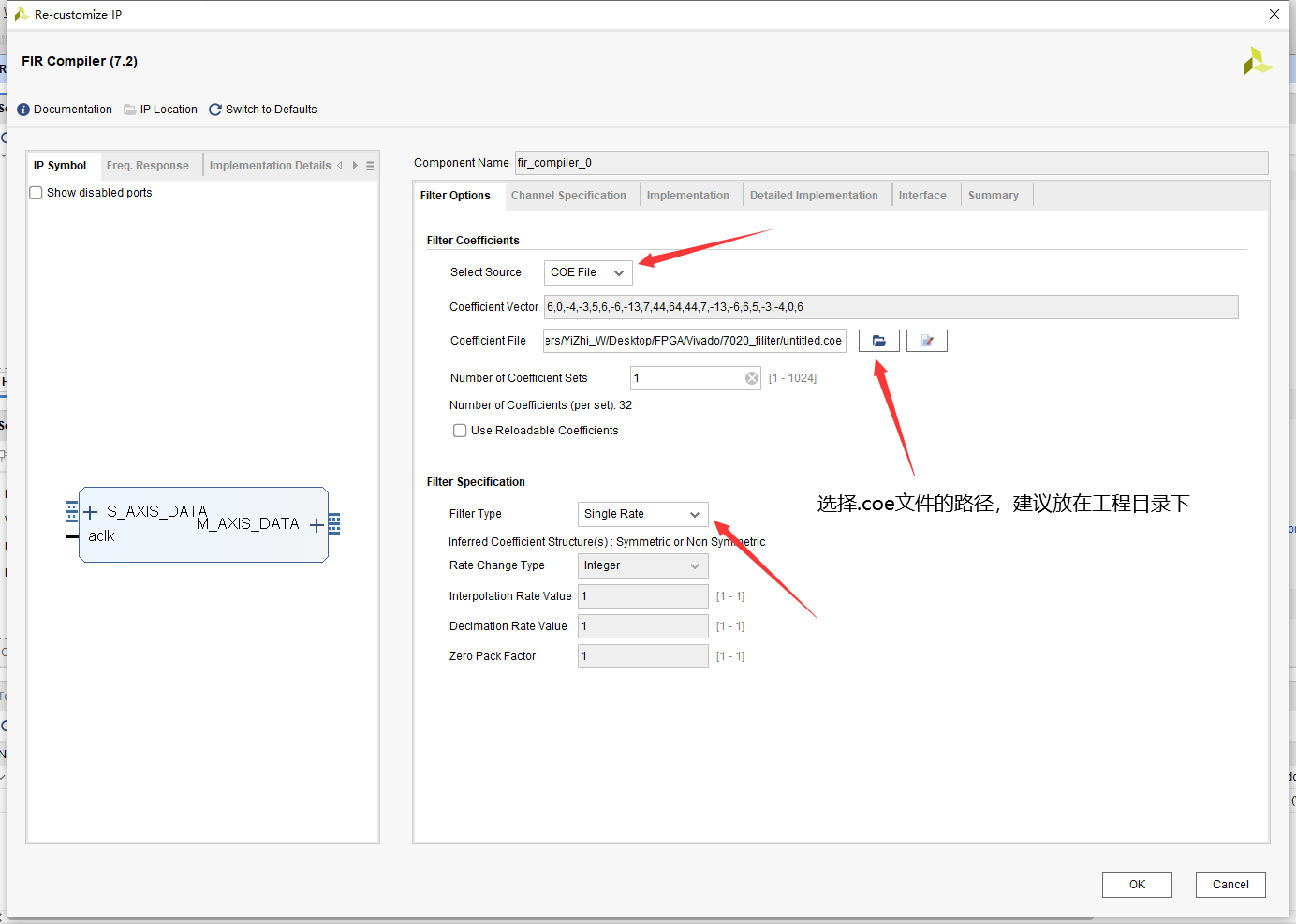

第一个标签页:

1.配置好.coe文件的目录,Single Rate是单速率。

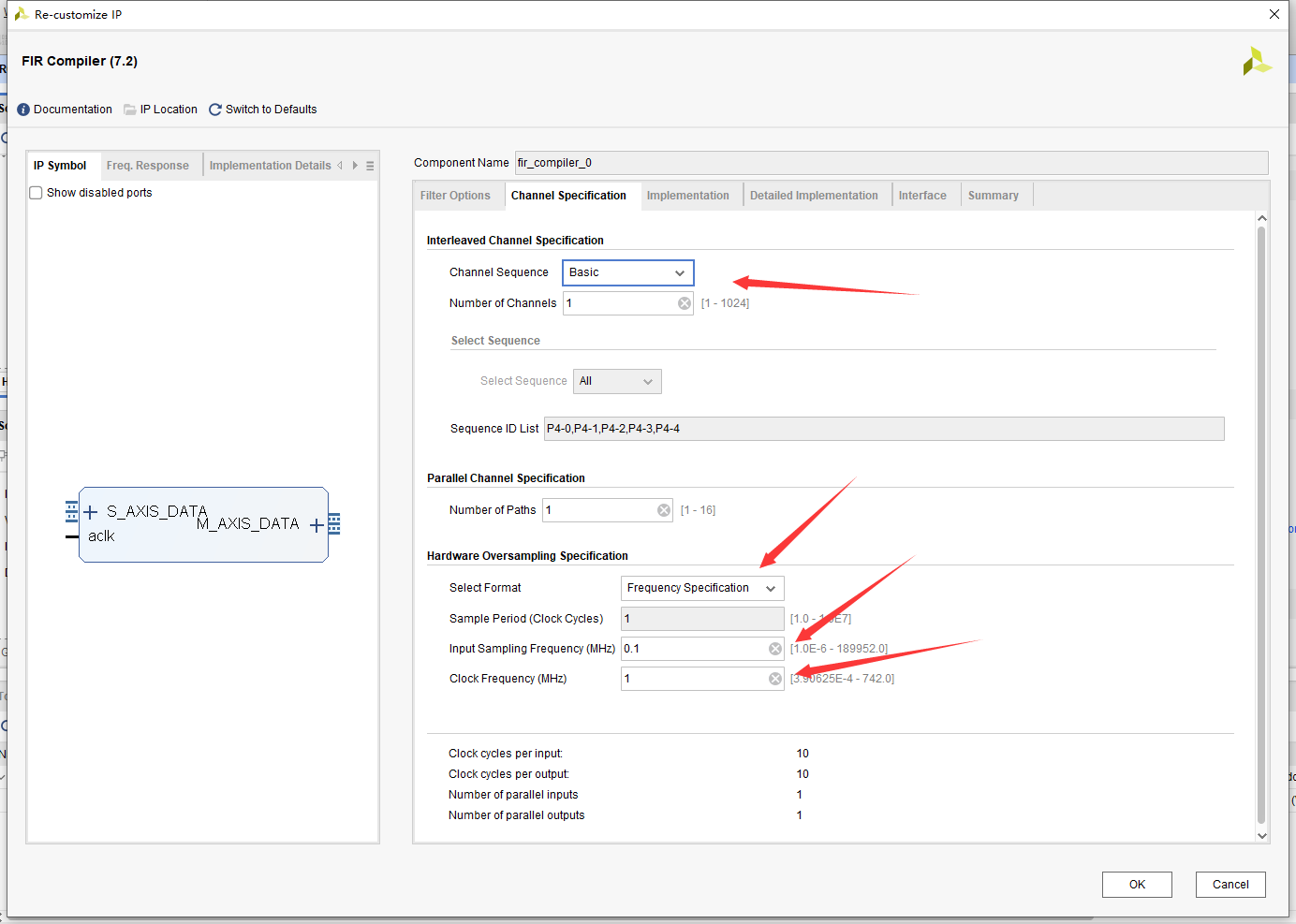

第二个标签页:

1.需要注意的是两个时钟频率,按实际情况填写。

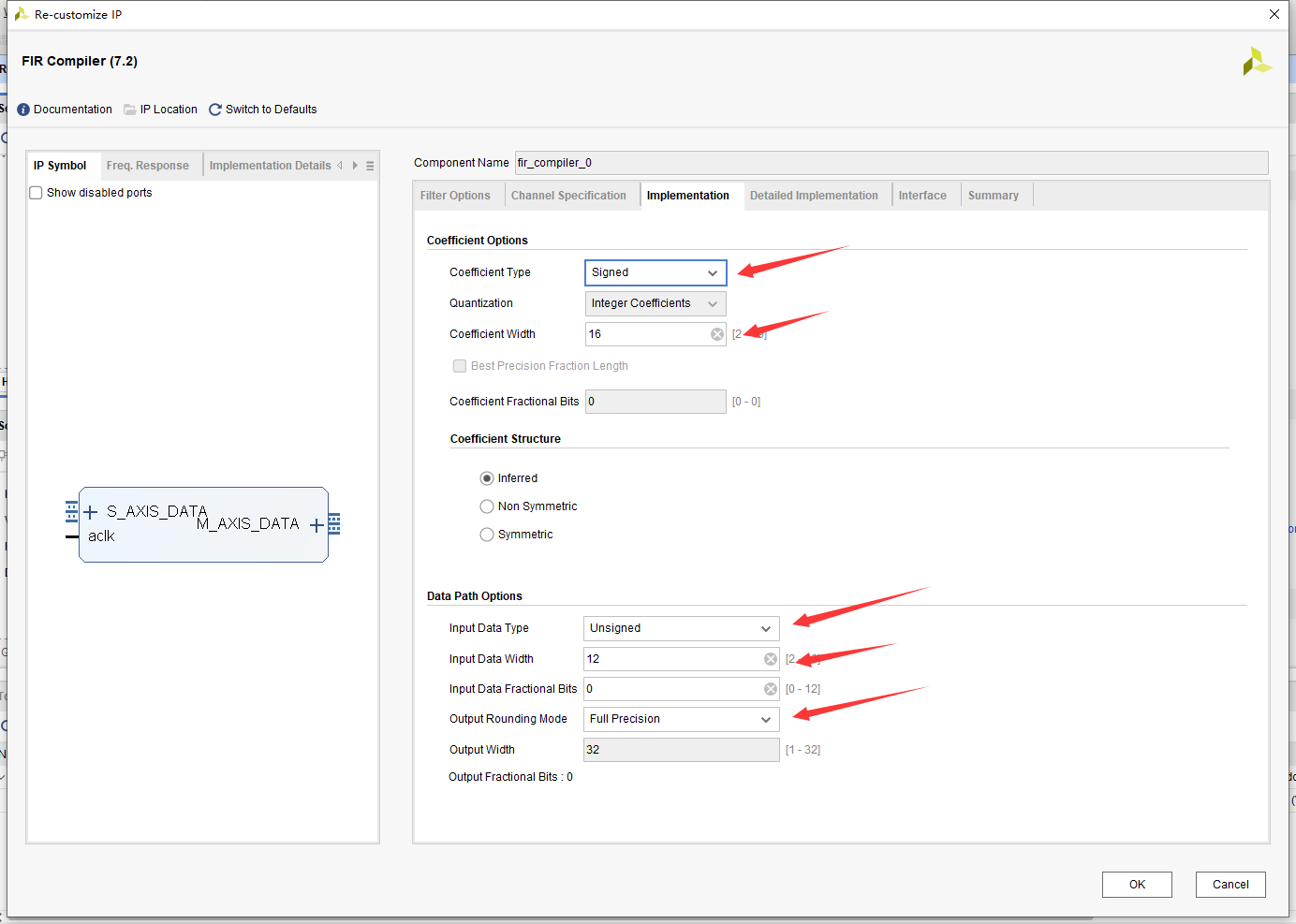

第三个标签页:

1.Coeffcient Type和Coeffcient Width要和量化滤波器时选择的相一致(很重要,错误的值可能会导致频率响应等错误)。

2.Input Data Width和你输入的数据一致。

3.例化IP核

FIR:

fir_compiler_0 your_instance_name (

.aclk(aclk), // 输入时钟频率

.s_axis_data_tvalid(s_axis_data_tvalid), // 输入信号有效,我们默认输入的信号一直有效所以拉高即可

.s_axis_data_tready(s_axis_data_tready), // 输出信号准备完成,可用可不用

.s_axis_data_tdata(s_axis_data_tdata), // 输入信号,这个接口的位宽和配置ip核时填写的位宽是不一致的,这个点需要注意,可以选择用输入的最高位把多出来的位宽补齐,例如这样 .s_axis_data_tdata({{4{fir_din[15]}},fir_din[15:4]}),

.m_axis_data_tvalid(m_axis_data_tvalid), // 输出数据有效,可用可不用

.m_axis_data_tdata(m_axis_data_tdata) // 输出信号,重要,虽然输入信号只有12位,但输出信号有足足32位,我们只需要关心高位。如果在配置IP时选择了带符号位,那么最高位会变成符号位。

);

结果

例外完成之后跑一遍工程然后下板调试,预期的结果为:频率在2Khz以下时幅值不变,高于2Khz后逐渐衰减,高于10Khz以后衰减到-40dB左右,如图所示:

实物测试结果(黄色信号为滤波后的信号,成功实现预期目标,低通滤波器没有问题了,但在调试高通滤波器时波形并不正确,目前正在调试寻找原因,有空继续更。):

数字滤波器

工程链接:https://download.csdn.net/download/YIZHI_W/20392285

1855

1855

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?