前几日刚入手一款ZYNQ-7000系列的板卡,之前我也没用过FPGA,直接跨越到ZYNQ的原因主要是某宝上这款板卡相较于其他片上仅有一块FPGA的板卡性价比更高。作为入门,在学习过程中,笔者选择先单独学习ZYNQ上的FPGA部分,也就是PL(Programmable Logic)部分,暂且先不管ARM核的部分。

本节概要

目录

1.ZYNQ简介

Zynq 的本质特征,是它组合了一个双核 ARM Cortex-A9 处理器和一个传统的现场可编程门阵列 (Field Programmable Gate Array,FPGA)逻辑部件。尽管之前也有过捆绑了 FPGA 的专用处理器,但是还没有出现过完全相同的方案。在 Zynq 上,ARM Cortex-A9 是一个应用级的处理器,能运行完整的像Linux这样的操作系统,而可编程逻辑(PL)是基于Xilinx 7 系列的 FPGA 架构。这个架构实现了工业标准的 AXI 接口,在芯片的两个部分之间实现了高带宽、低延迟的连接。这意味着处理器和逻辑部分各自都可以发挥最佳的用途,而不会有在两个分立的芯片之间的那种接口开销。同时又能获得系统被简化为单一芯片所带来的好处,包括物理尺寸和整体成本的降低。(关于Xilinx 7 系列的 FPGA 架构,感兴趣的读者可以做进一步深入的了解。)

2.背景:SoC与ASIC

我们常把ZYNQ描述成一个片上系统SoC(System on Chip),所谓的Soc又是什么呢?简单来说,就是使用单个硅芯片代替几个不同的物理芯片,来实现整个系统的功能。

过去,SoC通常指的是ASIC(Application Specific Integrated Circuit),即专用集成电路。它上面可以有数字的、模拟的和射频的元件,和混合信号模块组 合起来来实现模拟 - 数字转换和数字 - 模拟转换 (ADC 和 DAC)。单就数字部分而 言,一块 SoC 可以组合上数字系统所有的功能:处理、高速逻辑、接口、存储器等等。所有这些功能也可以用物理上分立的器件来实现,然后在印刷电路板 (PCB) 的层面上组合起来。SoC 的解决方案成本更低,能在不同的系统单元之间实现更快 更安全的数据传输,具有更高的整体系统速度、更低的功耗、更小的物理尺寸和更 好的可靠性。

目前,随着用户需求更加趋于灵活,可编程片上系统(System-on-Progammable-Chip)的出现,SoC的范围变得更加广。

基于ASIC的SoC(也就是过去人们常说的“SoC”)这种 SoC 类型只 适合于大批量而且将来不需要升级的市场领域。基于 ASIC 的 SoC 的代表性例子包括 在 PC、平板和智能手机上用的集成处理器。这些处理器典型地是由至少两个处理器 核、存储器、图形处理器、接口和其他功能模块组合起来的,而且大批量生产 出来用于寿命有限的产品中。相较于像FPGA、ZYNQ这一类可编程片上系统在灵活性、快速适应市场应用需求方面有着相当大的局限性。

因此,可编程片上系统这种更加灵活的SoC平台应运而生。笔者目前学习的ZYNQ就是一款Xilinx的全可编程 SoC (All-Programmable SoC,APSoC)。

3.ZYNQ-7000系列芯片架构

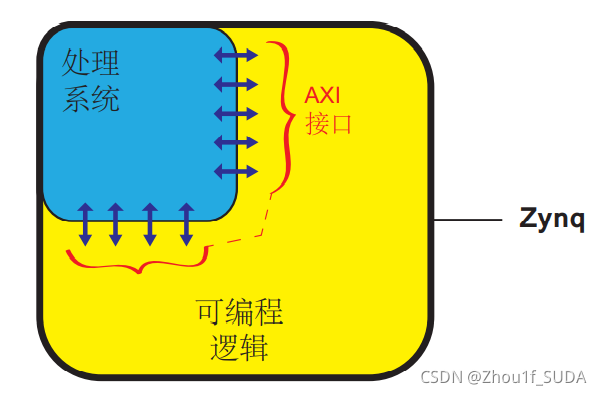

首先我们来了解一下芯片的高层模型。

从中可以注意到 Zynq 是由两个主要部分组成的:一个由双核 ARM Cortex-A9 构成的处理系统 (PS),和一个等价于一片 FPGA 的可编程逻辑 (PL)部分。它还具有集成的存储器、各种外设和高速通信接口。PL 部分用来实现高速逻辑、算术和数据流子系统是很理想的,而 PS 支持软件 程序和 / 或操作系统,这就意味着任何被设计的系统的整个功能可以恰当地在硬件和软件之间做出划分。PL 和 PS 之间的链接采用了工业标准的高级可扩展接口(Advanced eXtensible Interface,AXI)连接方式。

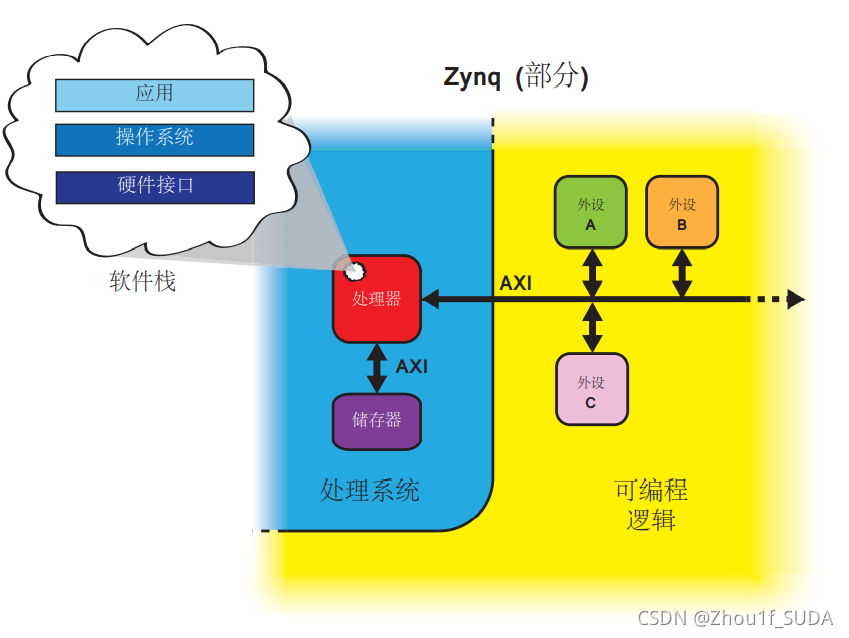

进一步细化模型如下图。

可以看到,蓝色PS部分(Processing System)具有固定的架构,承载了处理器和系统存储区, 而黄色PL 部分(Programmable Logic)完全是灵活的,给了设计者巨大的自由空间来创建定制的外设,或重用标准外设。

这里的外设我们可以理解成知识产权(Intellectual Property,IP)功能模块,也就是我们常说的IP——这些IP可以从Xilinx的库获得(随着设计工具提供)来源,也可以从之前的项目中重用,或是从第三方或是从开源仓库获得,然后再集成起来形成系统的设计。

Zynq 是一块 SoC,具有大量的标准 IP,这表明这些部件就不再需要重新设计了。这也加快了设计者的开发速度。我们需要考虑 IP 的各种来源,包括 Xilinx 库、产生自己的 IP 的机制,和第三方 IP 来源。当然,仅仅只提及这些模块是不够的 —— 它们还得被集成进系统去,建立起恰当的连接和交互。

而互联是通过连接了 PS 和 PL 的 AXI 接口总线来实现的。值得注意的是,这里处理器与外设链接的是单一总线,但其实一个处理器也可以连接多个外设总线。另外,可以看到软件是放在处理器那里的,也就是这里位 于 Zynq 的 PS 里的 ARM Cortex-A9。软件系统由一连串的软件单元组成的。

以上所述简单来说,就是我们可以在PL部分自己设计一个IP模块,再把它与PS部分进行连接交互,集成到整个嵌入式系统中去。而这个IP模块你可以引用一些已经设计好的IP进行重新的组合、拼装,也就是所谓的设计重用。(目前笔者的理解是这样的,欢迎大家指正讨论呀!)

1768

1768

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?