一、 MIG 控制器概述

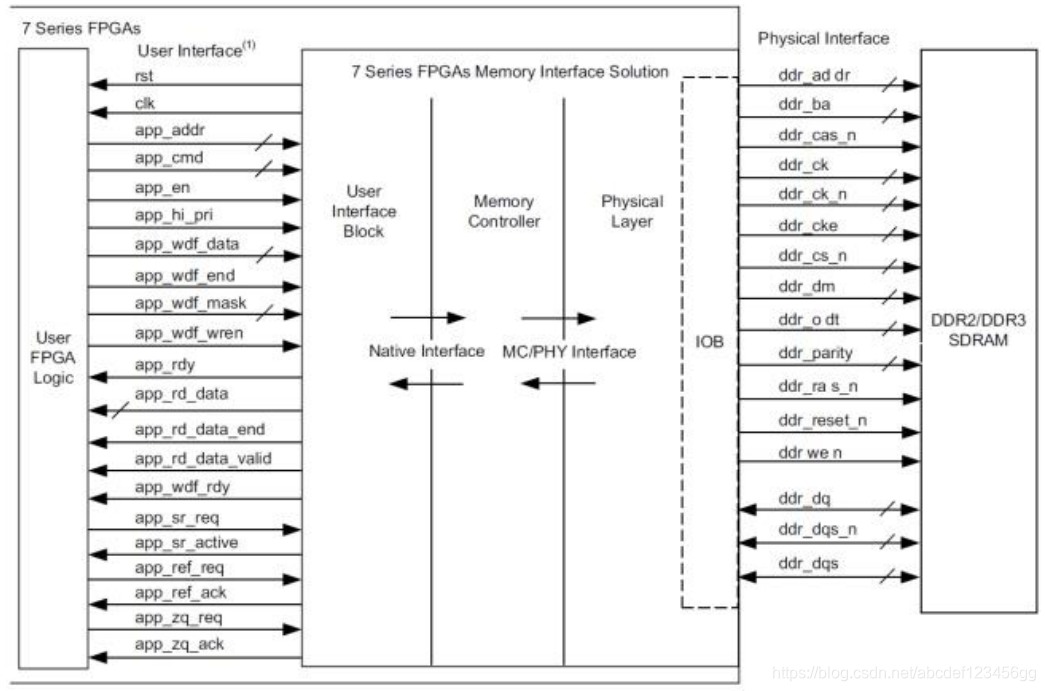

7 系列 FPGA 存储器接口解决方案核心如图所示。

二、 用户 FPGA 逻辑接口

上图所示的用户 FPGA 逻辑模块可以连接到外部 DDR2 或 DDR3 SDRAM 的任何 FPGA 设计。用户 FPGA 逻辑通过用户界面连接到内存控制器。IPCORE 提供了一个用户 FPGA 逻辑示例。

AXI4 从接口块

AXI4 从站接口将 AXI4 事务映射到 UI,以向内存控制器提供行业标准总线协议接口。

用户界面块和用户界面

UI 块向用户提供 FPGA 逻辑块。它通过呈现平面地址空间和缓冲读写数据来提供对本机接口的简单替代。

内存控制器和本机接口

内存控制器(MC)的前端显示 UI 块的本机接口。本地接口允许用户设计提交存储器读写请求,并提供将数据从用户设计移动到外部存储器件的机制,反之亦然。内存控制器的后端连接到物理接口,并处理该模块的所有接口要求。 内存控制器还提供了重新排序选项,重新排序接收的请求以优化数据吞吐量和延迟。

PHY 和物理接口 PHY 的前端连接到存储控制器。PHY 的后端连接到外部存储设备。 PHY 处理所有存储器件信号顺序和定时。IDELAYCTRL 任何使用 IDELAYs 的 bank 都需 IDELAYCTRL。 IDELAY 与数据组(DQ)相关联。 任何使用这些信号的 BANK/时钟区域都需 IDELAYCTRL.MIG 工具实例化一个IDELAYCTRL,然后使用 IODELAY_GROUP 属性(参见 iodelay_ctrl.v 模块)。基于此属性,Vivado Design Suite 可根据需要在设计中正确复制 IDELAYCTRL IDELAYCTRL 参考频率由 MIG 工具设置为 200 MHz,300 MHz 或 400 MHz,具体取决于 FPGA 的存储器接口频率和速度等级。 根据设置的 IODELAY_GROUP 属性,Vivado Design Suite 会复制 IDELAY 块所在区域的 IDELAYCTRL。

当用户自己创建一个多控制器设计时,每个 MIG 输出都具有用原语实例化的组件。 这违反了IDELAYCTRLs 的规则和 IODELAY_GRP 属性的使用。IDELAYCTRL 需要只有一个组件的实例化才能正确设置属性,并允许工具根据需要进行复制。

用户接口

UI 连接到 FPGA 用户设计,以允

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2294

2294

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?