VHDL程序一般由于三个部分组成:library、entity 和 architecture。

1.library

library即“库”,是为了提高设计的效率和一致性将一些有用的信息汇聚到一起,共开发者使用。类似C语言中的 .h 文件。在VHDL中使用库,首先要声明,语法如下:

library <library_name>

一般一个library中会包含多个程序包,若要使用程序包中具体的库、程序包或子程序,可使用如下语法:

use <library_name>.<package_name>.<function_name>;

使用一个程序包中的全部函数,语法如下:

use <library_name>.<package_name>.all;

库分为两类:设计库,即项目中设定的目录所对应的work库;资源库,即常规元件和标准模块存放的库。

VHDL程序代码的开头的一般形式。

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

标准库的简单介绍

首先,这里有一个隐含的 std.standard 程序包的声明,这个程序包是所有编译器必须包含的,所以不需要显示的声明和引用。在 std.standard 程序包中主要定义了一些典型的、基本的数据结构,例如:bit bit_vector integer boolean。

其次,std.textio 主要定义了用户的输入,输出。下面简单介绍 IEEE 标准库中程序包的意义。

IEEE.std_logic_1164 : 定义了一些增强型的数据结构,例如std_logic,std_logic_vector;

IEEE.std_logic_textio : 针对1164程序包定义了用户的输入、输出;

IEEE.std_logic_arith : 提供了数的计算操作,基于有符号数、无符号数以及逻辑矢量等;

IEEE.numeric_bit : 提供了数的计算操作,基于bit数组类型的有符号和无符号数;

IEEE.numeric_std : 提供了数的计算操作,基于std_logic数组类型的有符号和无符号数;

IEEE.std_logic_signed : 提供了基于std_logic_vector的有符号数计算操作;

IEEE.std_logic_unsigned : 提供了基于std_logic_.vector的无符号数计算操作;

IEEE.math_real : 提供了基于real类型的数的计算操作;

IEEE.math_complex : 提供了基于复数类型的数的计算操作;

IEEE.std_logic_misc : 为1164程序包定义了补充的类型、子类型、常数、函数等。

2,entity

entity即实体的意思,在VHDL设计中,它主要描述对象的外貌,即对象的输入和输出的端口信息,而器件的具体功能由 architecture 来描述。entity 和 architecture之间的关系就像芯片,entity描述芯片的管脚信息,architecture 负责实现芯片具体的功能。总结来说,entity 和 architecture就是接口和内容的关系。

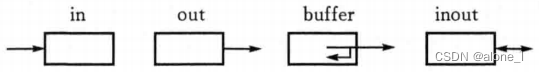

VHDL中有四种端口类型:输入、输出、缓冲及双向端口。定义时的语法如下:

<port_name>:in<type>;

<port_name>:out<type>;

<port_name>:buffer<type>;

<port_name>:inout<type>;

//当多个端口具有同样的方向和类型时,也可以写成如下形式

<port_name_list>:<mode><type>

buffer端口也是输出端口的一种,由于VHDL语言比较严谨,所以在entity中定义为 out 的端口,在architecture 中只能够被赋值。buffer类型短端口的数据,architecture 里面的语言可以直接引用。inout 端口主要在处理总线数据时使用,一般使用三态门实现。四种端口的图示如下:

generic语法结构,专门用来定义一些参数信息,方便代码的复用,以提高可重用性,是可选的。

3,architecture

architecture 即构造体,主要负责描述entity的具体实现,所以 architecture 必须依附于 entity而存在。一般建议一个entity对应一个architecture。其结构如下:

architecture <arch_name> of <entity_name> is

<part A>

begin

<part B>

end <arch_name>

其中part A 是说明部分,主要负责一些声明和定义工作,一是元件声明,即component语法,component也是依附于entity存在,只不过是另一个entity,不能是当前architecture对应的entity;二是指要使用的中间信号量的声明;除此之外也可以定义一些函数或过程(即function 或 procedure)。

part B是语句部分,主要负责具体的功能实现,并且位于其中的语句都是并发执行的。语句部分可以有三种实现形式:元件例化语句、进程语句和独立语句。元件例化语句即程序框架中的 instance语句。进程语句即程序框架中的process语句,在architecture中多个process是并行执行的,但是process中的语句是串行执行的,每个process中的由其对应的<sensitive_signals_list>中任何一个信号触发,触发后,process中的语句将会从begin开始执行到end process ,然后等待下一次触发。根据<sensitive_signals_list>的三种表现形式可以将process分为三种形式:纯组合逻辑process,纯同步时序逻辑process,具有异步复位的时序逻辑process。独立语句,即architecture语句部分的一些未包含在process中的语句(必须是支持并行执行的语句),

VHDL基本程序框架范例

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

//entity相当于verilog中的module;cellAnd相当于verilog中的模块名

entity cellAnd is

generic(

WIDTH:integer: =8

);

port (

a:in std_logic_vector(WIDTH-1 downto 0);

b:in std_logic_vector(WIDTH-1 downto 0);

c:out std_logic_vector(WIDTH-1 downto 0)

);

end cellAnd;

architecture Behavioral of cellAnd is

begin

c <= a and b;

end Behavioral

VHDL 中的注释使用 ”–“ ,即两个连续的短横杠,VHDL中只有一种注释。

3116

3116

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?