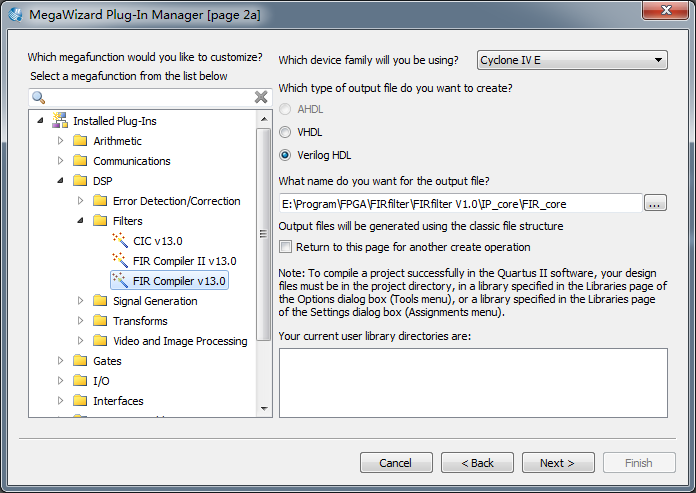

软件环境:Quartus II 13.0

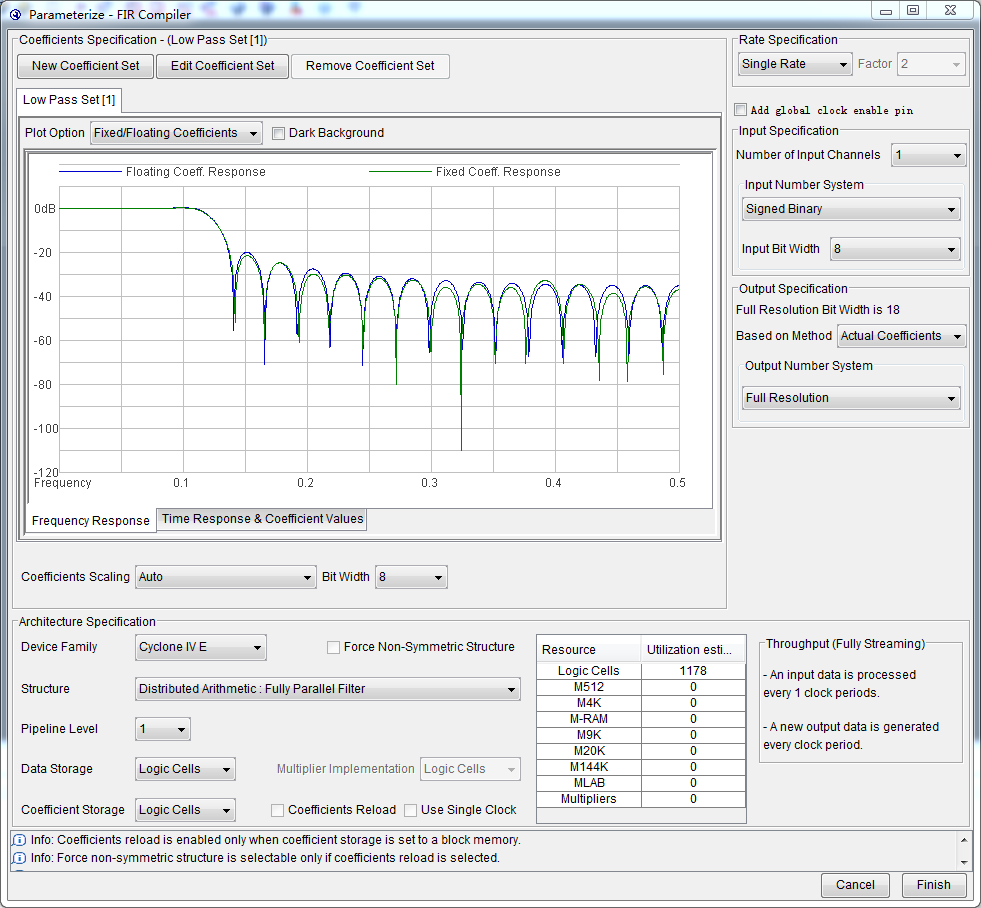

Coefficients Scaling:量化处理 Bit Width:量化位数

Input Bit Width:滤波器系数的位宽。

pipline Level:流水线级数

Structure:滤波器结构

Distributed Arithmetic:Fully Serial Filter(全串行分布式算法结构)

Distributed Arithmetic:Multi-Bit Filter(多比特分布式算法结构)

Distributed Arithmetic:Fully Parallel FIlter(全并行分布式算法结构)

Variable/Fixed Coefficient:Multi-Cycle(多时钟周期结构)

Clocks to compute:(选择多时钟周期结构) X个时钟周期处理一个数据即可。根据FPGA时钟频率和输入时钟频率。例如FPGA时钟频率为32MHz,输入频率为8MHz,则为4.

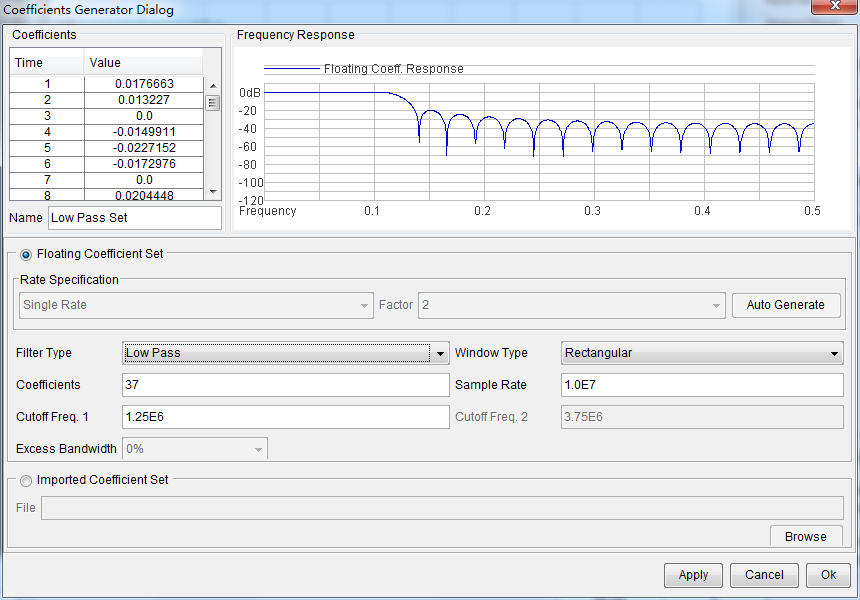

系数设置有两种方法,一种就是直接在IP核中根据通带、阻带等特性曲线设计滤波器。二是直接装载已经设计好的滤波器参数文件。

FIlter Type:滤波器类型

Low Pass 低通

Hgh Pass 高通

band Pass 带通

Band Reject 带阻

Window Type:窗类型

Rectangular:矩形窗

Hanmming:汉明窗

Hanning:汉宁窗

Blackman:

Coefficients:

Sample Rate:采样速度

CUtoff Freq 1:截止频率 如果是带通的话还有CUtoff Freq 2

7622

7622

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?