一、简介

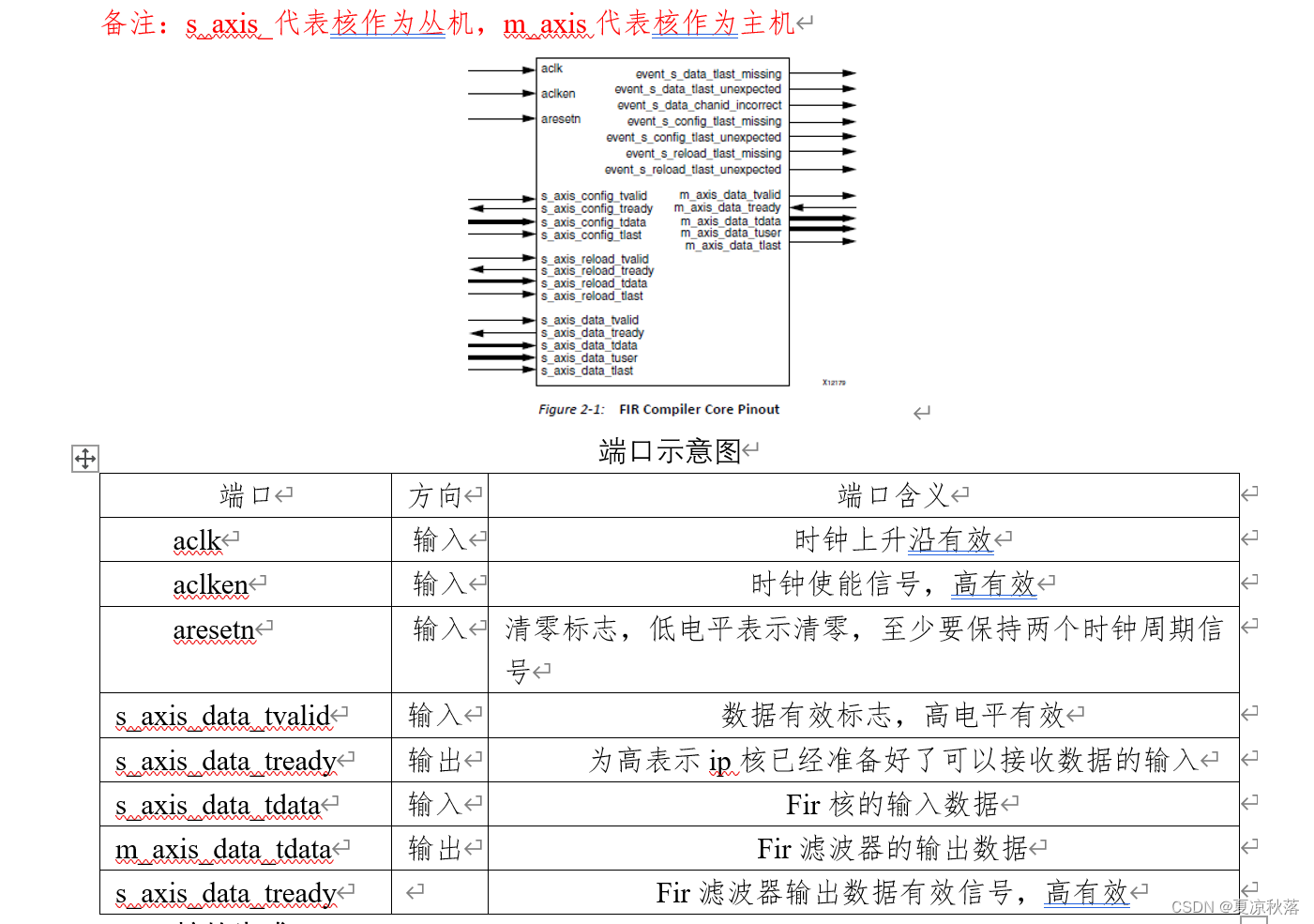

二、 ip核的端口说明

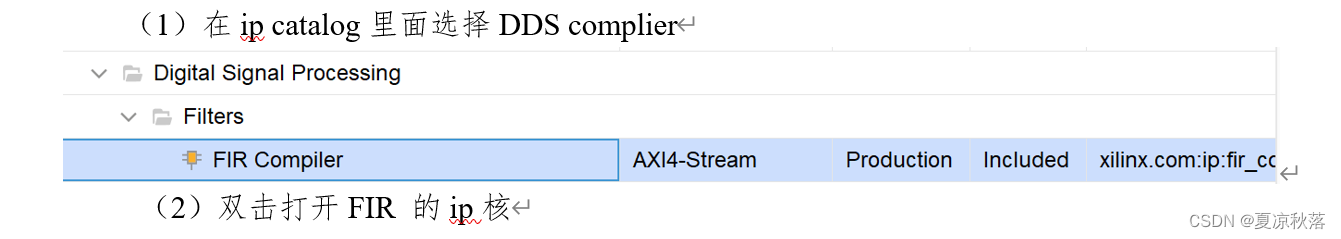

三、 ip核的生成

Sample Period:采样周期/滤波器驱动时钟周期,这里采样频率和时钟频率可以不一致,ip核内部做了处理,不会影响最终输出的结果和频率的值,具体例子可以参考文献【11】

四、 典型示例

设计一个滤波器阶数为19,采样频率为20Mhz,截止频率5Mhz,阻带衰减为60dB的一个fir滤波器;

-

matlab中fdatool工具的使用

12bit量化导出coe文件,如下图所示:

-

vivado中Fir ip核的使用

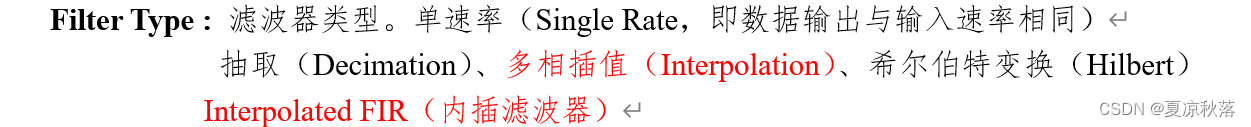

(1)Filter options的设置

(2)Channel Specification的设置

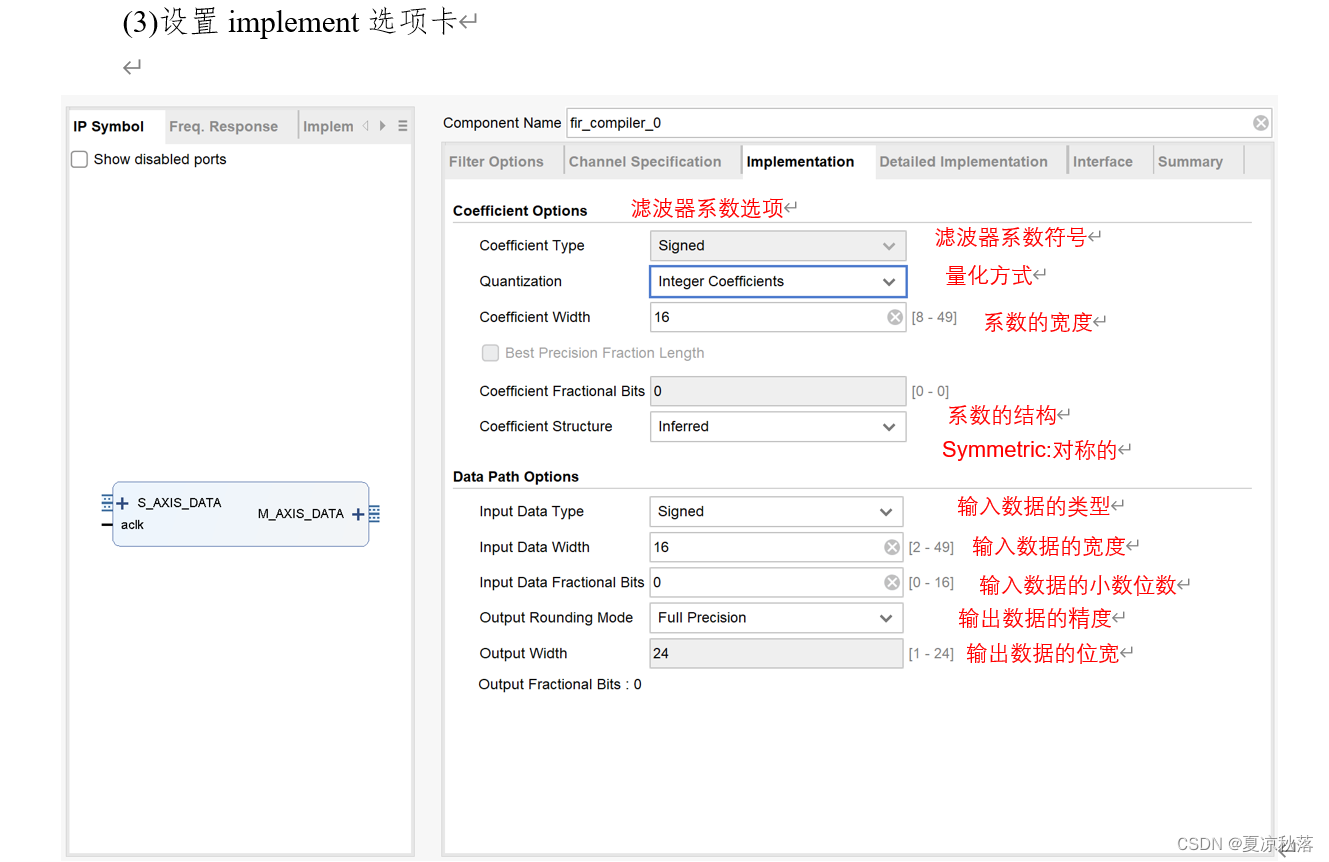

(3)Channel Specification的设置

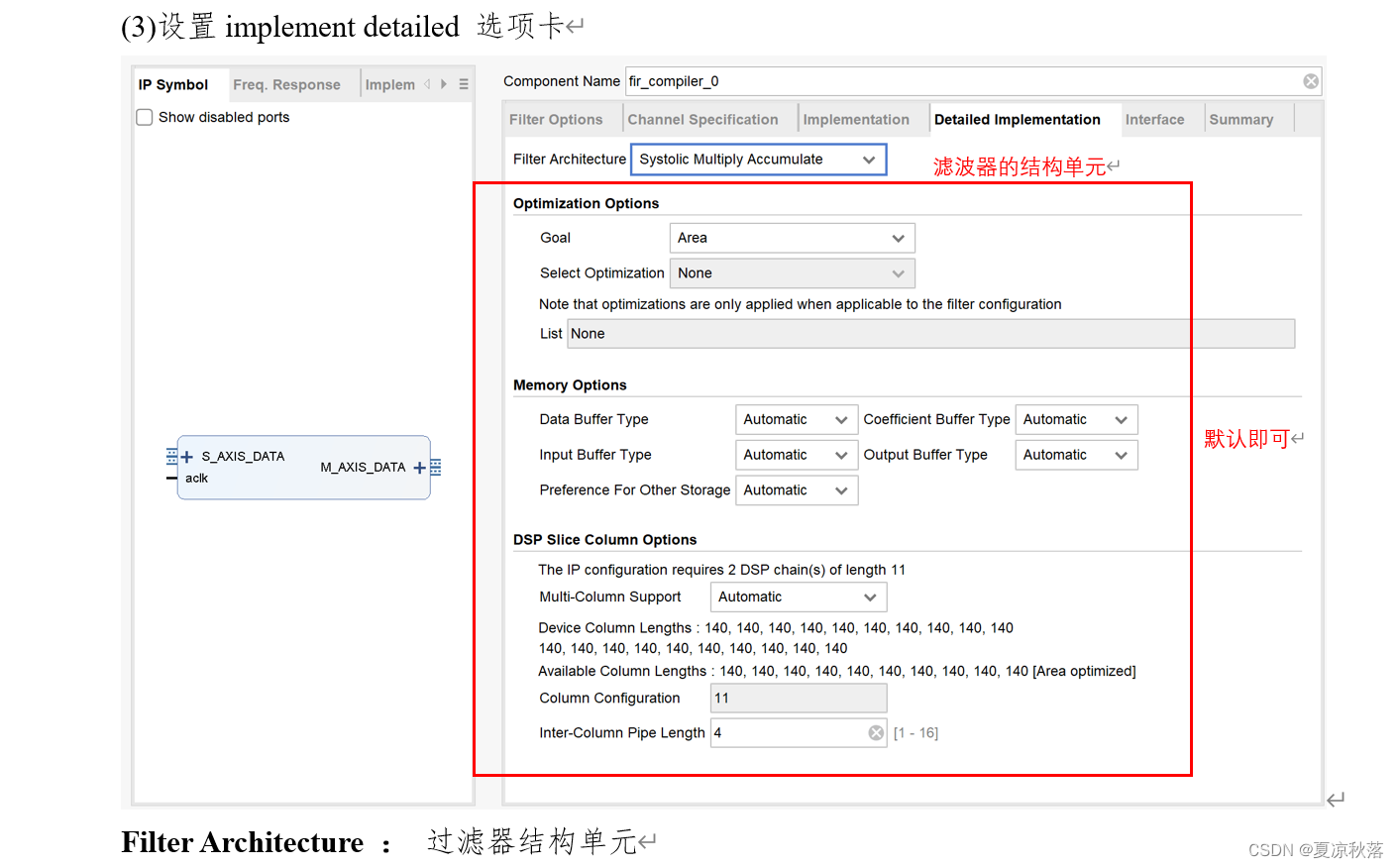

(4)其他ip核保持默认设置即可。

五、结果展示

**输入:**频率为2MHZ和8MHZ的正弦波

输出:频率为2MHZ的正弦波

六、 参考资料

- 使用vivado建立FIRip核使用

- Vivado FIR滤波器IP核实现

- FPGA数字信号处理(五)Vivado FIR IP核实现

- Vivado Fir Ip核动态更改滤波器系数

- MATLAB-Vivado FIR IP核低通滤波

- Verilog学习笔记 (三)vivado FIR IP核设置

- 基于vivado的fir ip核的重采样设计与实现

- matlab与FPGA无线通信、FPGA数字信号处理系列(2)——Vivado调用IP核设计FIR滤波器

- FIR设置过采样率 matlab,Xilinx FIR IP的介绍与仿真

- FPGA数字信号处理(二)并行FIR滤波器Verilog设计

- Vivado的FIR IP核实现低通滤波器(重点留意,包含matlab仿真程序的产生)

- 基于xilinx-IP的FIR滤波器多通道实现

7430

7430

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?