什么是CXL

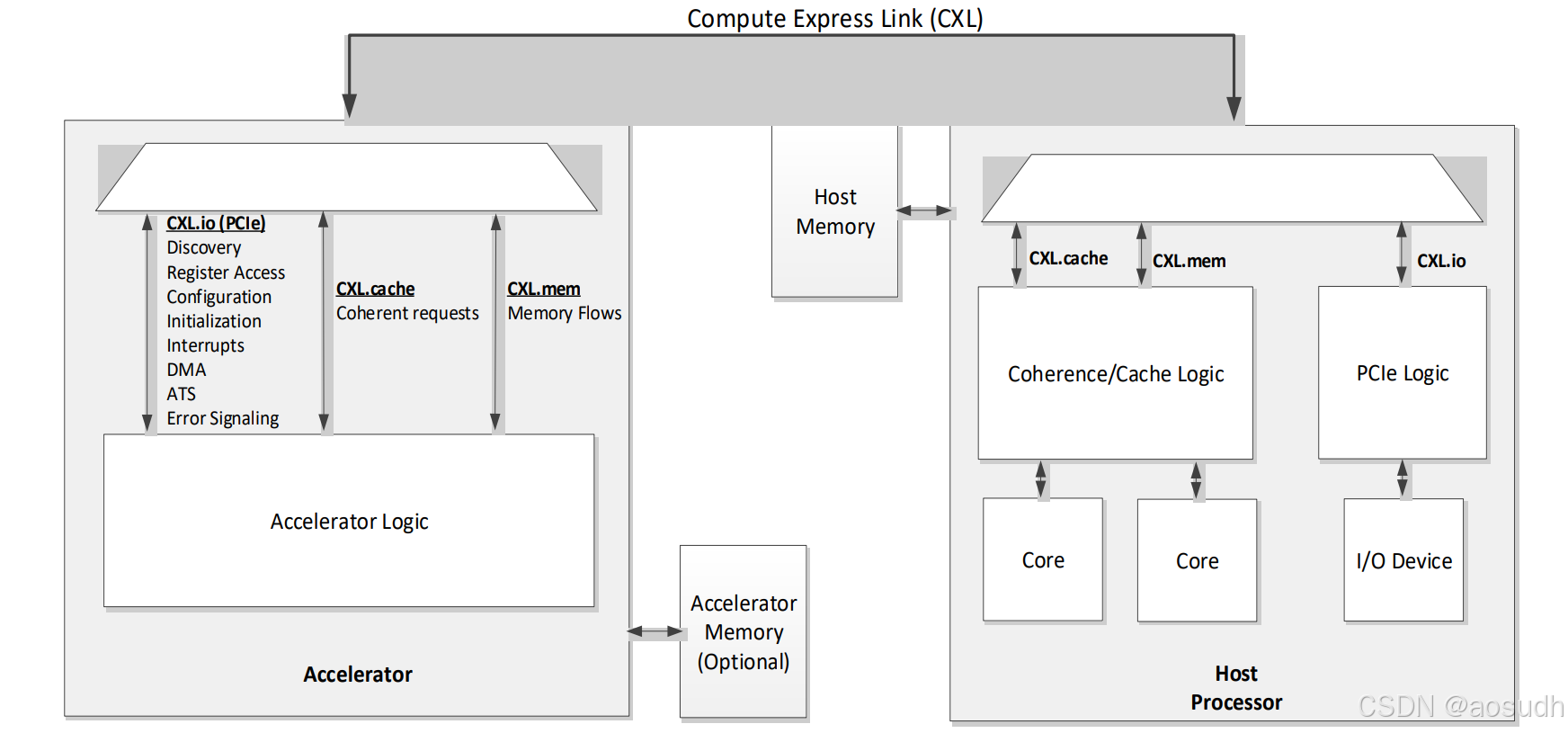

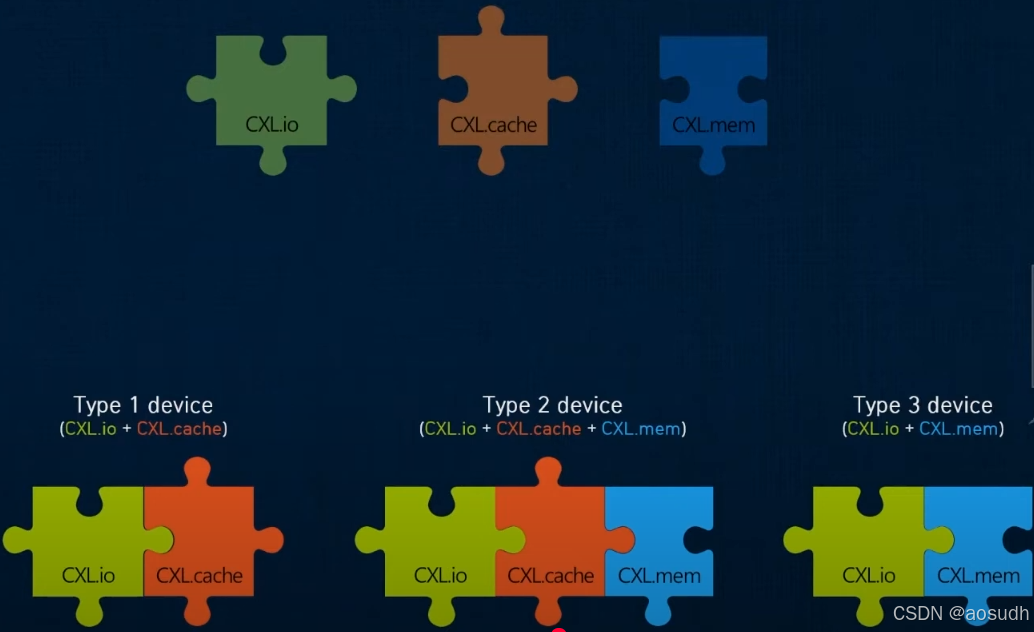

Compute Express Link(CXL)是一种动态的多协议技术,其设计初衷是为了给加速器和内存设备提供支持。它提供了一套完备而丰富的协议集,其中包含了多种不同的语义协议。例如,CXL.io 具有类似于 PCIe 的 I/O 语义,在整个系统中扮演着至关重要的角色,它是实现设备发现、枚举操作、错误报告以及主机物理地址(HPA)查找的必备协议。这意味着在系统启动或者设备接入时,CXL.io 协议能够帮助系统精确地找到并识别设备,同时还能处理设备在运行过程中可能出现的错误情况,并对主机物理地址进行查找,确保数据的正确传输和处理。

而 CXL.cache 和 CXL.mem 这两种协议则与系统的缓存和内存访问密切相关。它们的实现具有一定的灵活性,可根据特定的加速器或内存设备的使用模式来选择是否实施。对于一些对性能要求不高的设备,可能会选择不实施这些协议;而对于那些需要高速缓存和高效内存访问的设备,它们则可以充分发挥其作用。

CXL 技术的一个显著优势在于它能够提供低延迟、高带宽的传输路径。当加速器需要访问系统中的其他组件时,或者系统需要访问连接在 CXL 设备上的内存时,这种低延迟和高带宽的特性就会展现出巨大的优势。这对于当今对性能要求极高的数据密集型应用场景来说,如大规模数据处理、深度学习计算、高性能服务器等,是非常重要的,因为它可以大大缩短数据传输时间,提高系统的整体运行效率。

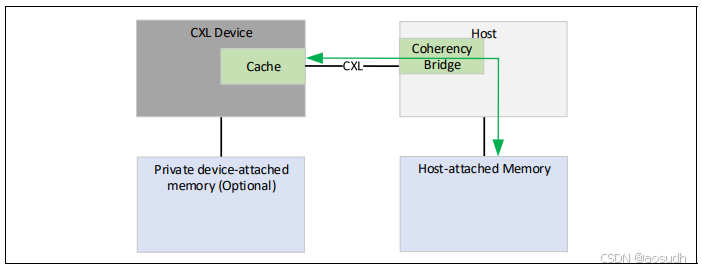

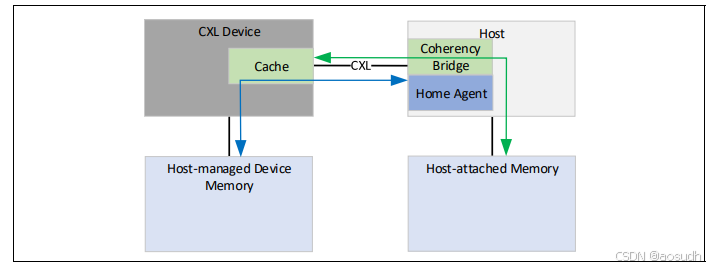

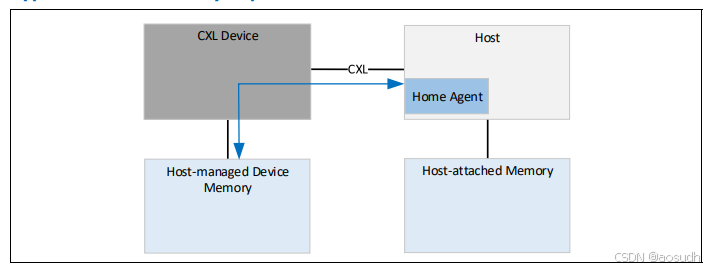

另外,如下图所示,清晰地展示了一个设备通过 CXL 技术连接到主机处理器的架构,让我们可以直观地理解 CXL 技术在硬件连接中的具体应用和布局,为我们更好地理解 CXL 技术在整个系统中的作用提供了可视化的帮助。

CXL 2.0 规范在完全向后兼容 CXL 1.1(以及 CXL 1.0)的基础上,开创了比 CXL 1.1 更多的应用模式。它支持热插拔管理,这意味着在设备运行过程中,可以安全地插入或移除相关组件,而无需关闭整个系统,大大提高了设备维护和升级的便捷性。在安全方面,CXL 2.0 进行了强化,能更好地抵御各类安全威胁,保障数据的安全性和系统的稳定性。同时,它还提供了对持久内存的支持,即使在系统断电后,内存中的数据依然能够得以保存,这对于需要长期保存重要数据的场景,如数据中心、企业关键业务系统等,具有重要意义。此外,CXL 2.0 具备内存错误报告功能,能够及时发现并报告内存运行过程中出现的错误,便于及时采取措施进行修复,减少因内存错误导致的系统故障。在数据监测方面,CXL 2.0 支持遥测技术,可以实时收集和传输设备的运行状态、性能指标等数据,帮助运维人员更好地了解设备的运行情况,进行有效的性能优化和故障预测。

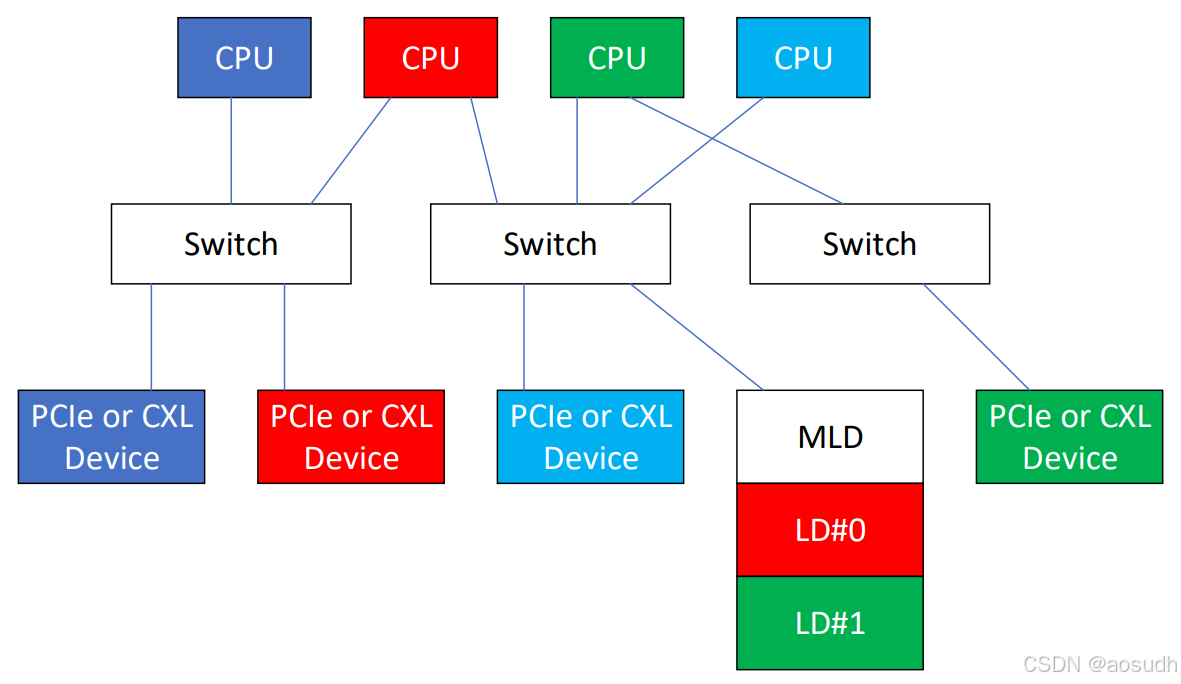

在架构支持上,CXL 2.0 为扩展提供了单级交换支持,具备跨多个虚拟层级汇聚设备的能力,还包括对内存设备的多域支持。如下图所示,通过单级交换实现了内存和加速器的解耦,同时实现了跨多个虚拟层级的扩展,每个虚拟层级用不同颜色区分,形象地展示了其工作模式。并且,CXL 2.0 允许这些资源(内存或加速器)从一个域下线,然后再上线到另一个域,这样就能根据不同虚拟层级的资源需求,对资源进行分时复用,极大地提高了资源的利用效率,降低了成本。

三种CXL设备

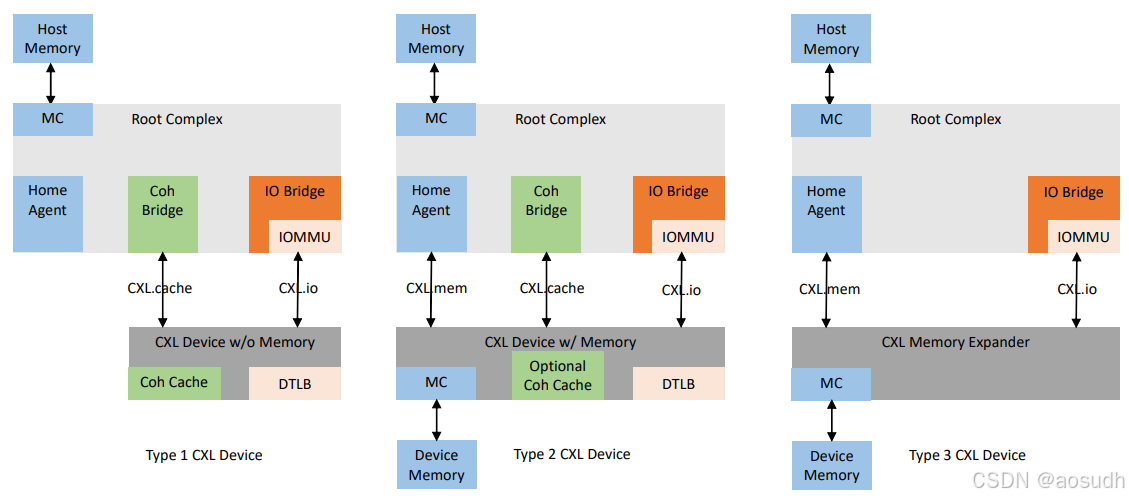

CXL Type 1 设备

CXL Type 1 设备专注于复杂计算任务,其内部的完全相干缓存是关键。它突破了传统排序模型的限制,可执行如特殊原子操作等高级功能。借助 CXL.cache 协议,在与主机交互时能有效管理缓存相干性,尽管缓存大小受主机限制,但在特定计算场景中能发挥重要作用,为需要高性能缓存支持的应用提供了有力保障。

CXL Type 2 设备

CXL Type 2 设备集成了缓存和内存,在数据处理中具有独特优势。除完全相干缓存外,还有如 DDR、HBM 等附加内存。通过 Host - managed Device Memory (HDM) 与主机交互,有主机偏差和设备偏差两种模式。在主机偏差时,设备访问内存需经主机;设备偏差时,设备可直接访问内存。可采用 CXL.cache 或 CXL.mem 协议的 Back - Invalidation Snoop (BISnp) 来管理 HDM 一致性,且支持 Bias - based coherency 模型,通过 Bias Table 和 Transition Agent 维护偏差模式。

CXL Type 3 设备

CXL Type 3 设备作为主机内存扩展的重要手段,专注于提供高效的内存服务。支持 CXL.io 和 CXL.mem 协议,主要用于扩展主机内存。CXL.io 协议用于设备发现、枚举、错误报告和管理等,不涉及 CXL.cache 协议。内存技术和组织形式多样,可根据主机支持情况灵活配置,且在 CXL 2.0 及后续版本中引入了一些新特性,如在 CXL 3.0 中支持共享内存功能。

为什么选择CXL,其与传统PCIE设备与RDMA访存协议相比的优势

与PCIE相比

参考文章CXL 为什么比 PCIe 延迟低带宽高_cxl 内存延迟-CSDN博客

与RDMA相比

如何安装CXL设备

前提条件

所有硬件必须支持CXL 1.1或2.0规范

AMD EPYC :至少采用EPYC Genoa 及更新型号的CPU

Intel XEON:至少采用XEON 4 Sapphire Rapids 及更新型号的CPU

BIOS和固件升级到最新版本

CXL支持通常在最新固件中提供,或通过开启隐藏bios选项,开启CXL Type3 Legacy 设备支持(具体BIOS选项视厂商BIOS选项而定)。

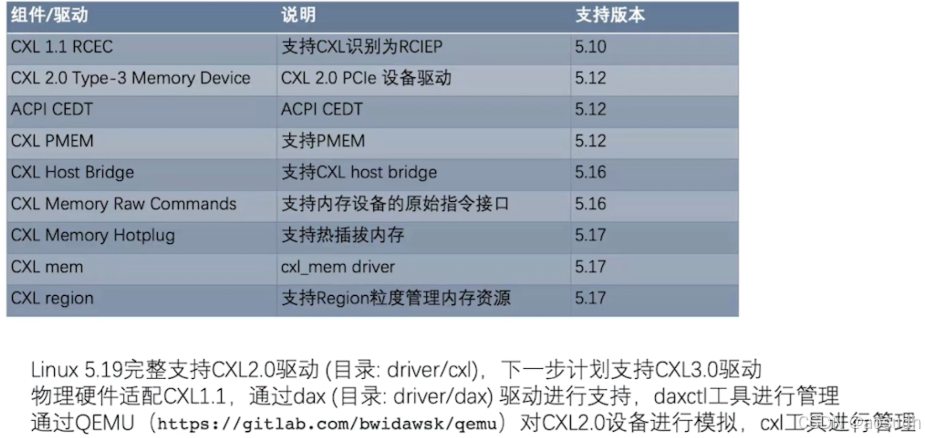

操作系统支持

以linux为例,确保当前系统的内核版本在5.19版本以上,但是最新的内核对更多其他功能的兼容性更好CXL 为什么比 PCIe 延迟低带宽高_cxl 内存延迟-CSDN博客

最新内核支持

Compute Express Link — The Linux Kernel documentation

本次环境配置

CPU:AMD genoa 9334 QS *2

平台:H3C R5300G6

平台内存:1*16G 4800 DDR5 pre CPU

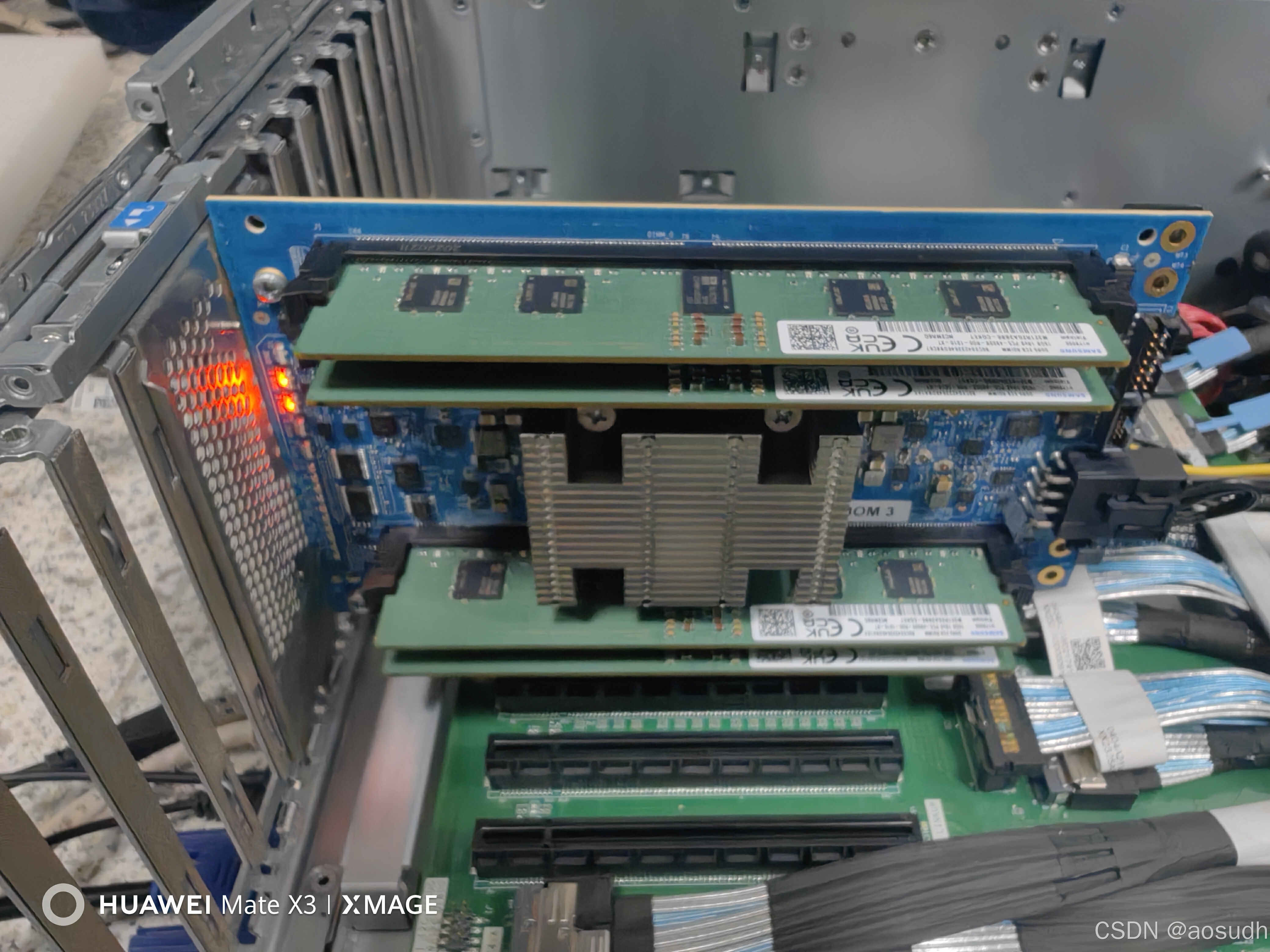

拓展卡型号1:AsteraLabs Leo System Validation Board

拓展卡型号2:基于澜起M88MX5891芯片的Type 3 CXL®内存扩展控制器

拓展卡内存:1*16G 4800 DDR5 pre Device

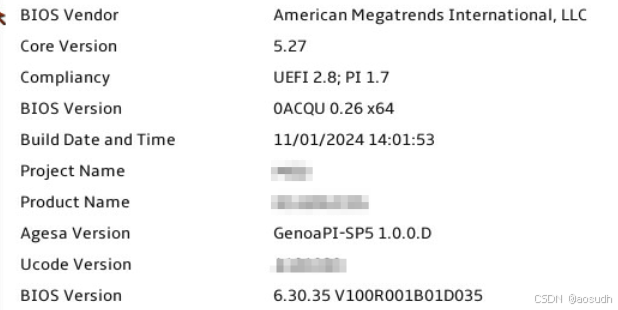

BIOS:AMI 5.27

系统:Ubuntu24.10 内核 6.8.0-50-generic

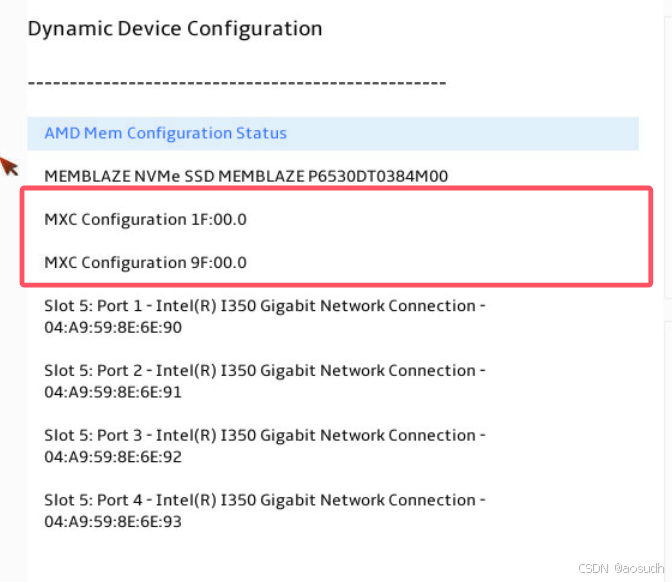

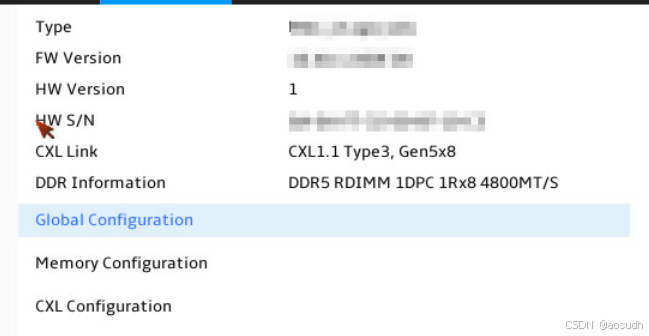

BIOS视图

一般来说,在BIOS中的dynamic device选项中即可看见CXL设备

点击进入后可以看到链路状态正确被识别为CXL1.1 Type3 设备,并且DDR5 RDIMM 4800内存也以识别正常

系统视图

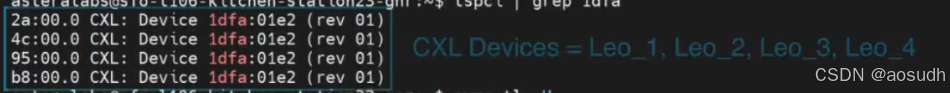

进入系统后,输入

lspci | grep CXL若设备正常使用,则可出现下图

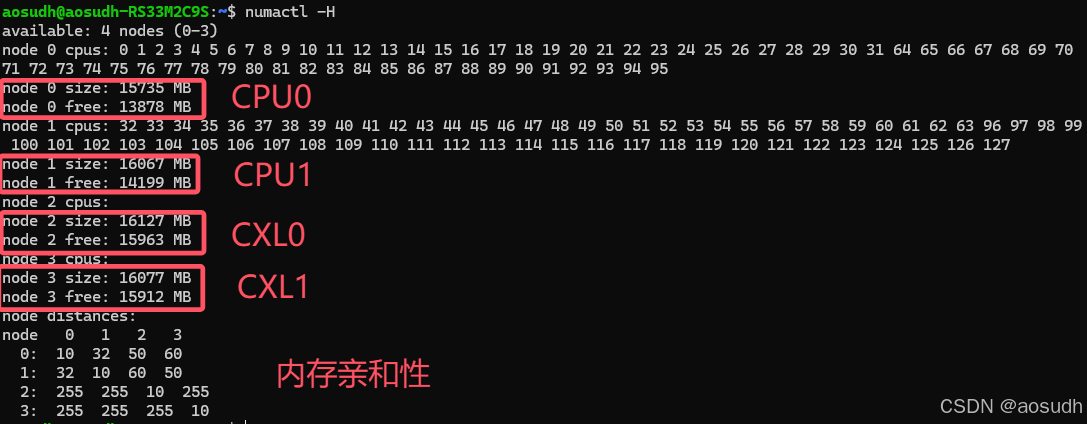

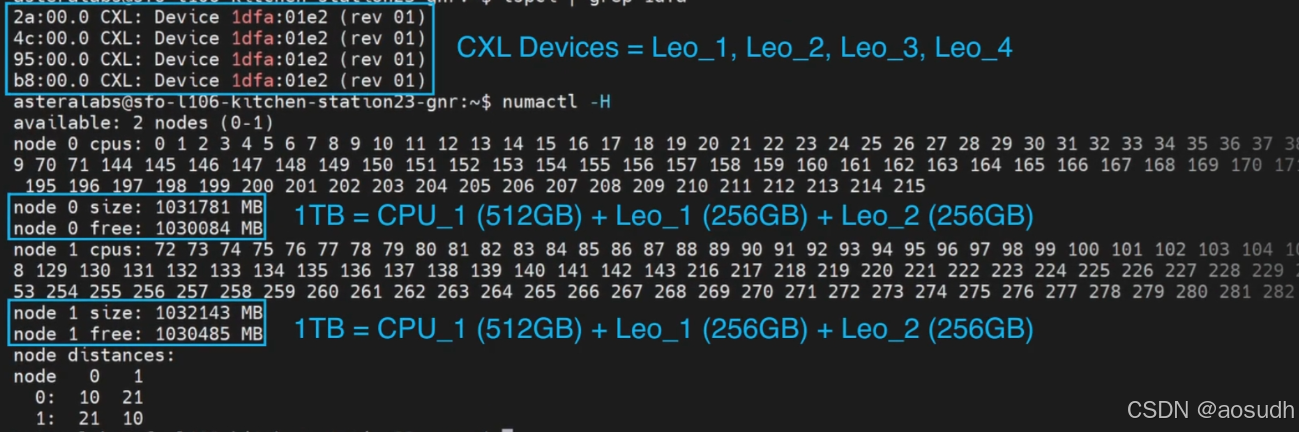

然后输入

numactl -H就可以看到如下图所示的输出

最后可以通过外部的cxl包对于cxl设备进行管理

以Ubuntu系统为例,输入如下代码

sudo apt install daxctl安装完成后,输入

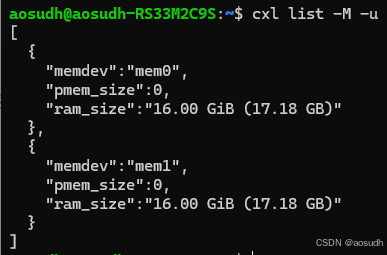

cxl list -M -u即可展示当前主机环境下的全部CXL设备及其容量

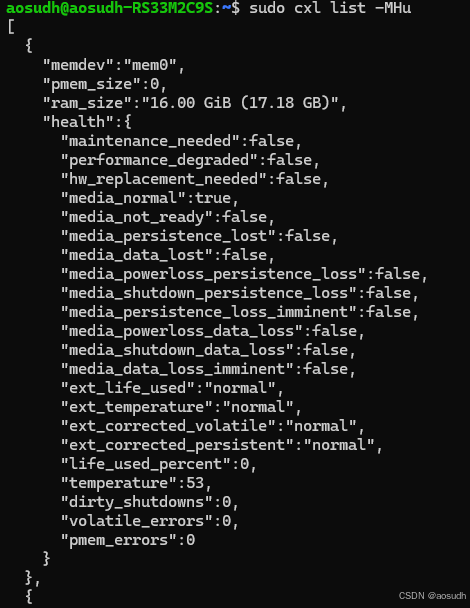

额外的,输入如下指令,也可以查看当前设备的健康状态信息

sudo cxl list -MHu

如何检测延迟与吞吐

延迟测试

https://github.com/torvalds/test-tlb

下载,gcc编译过后,输入

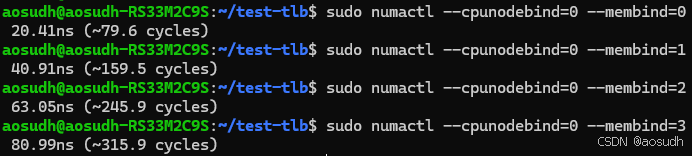

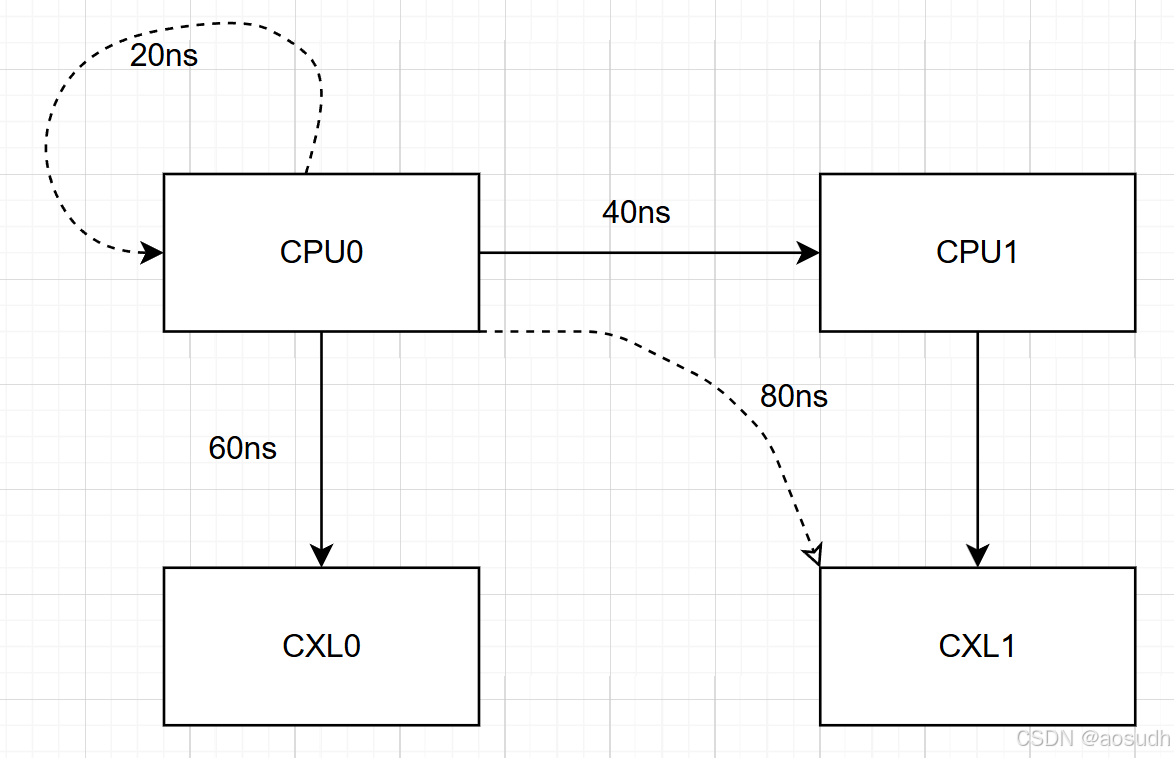

numactl --cpunodebind=<cpu id> --membind=<numa node id> ./test-tlb 1000000000 4096可以得到以下结果(具体延迟可能因为内存通道配比问题而不太正常,但是大致的延迟数量级与比例可以因此得出)

吞吐测试

下载,make编译过后,输入

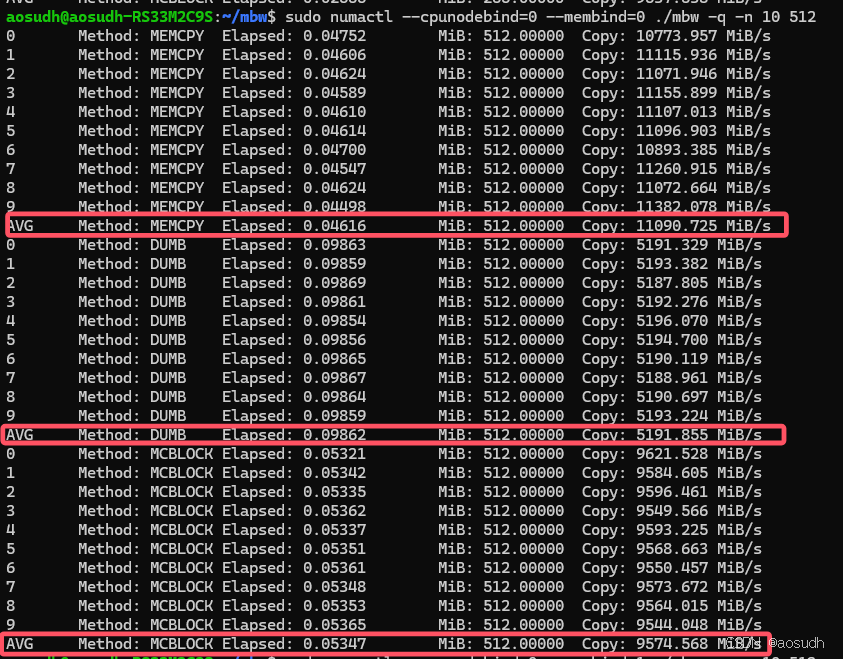

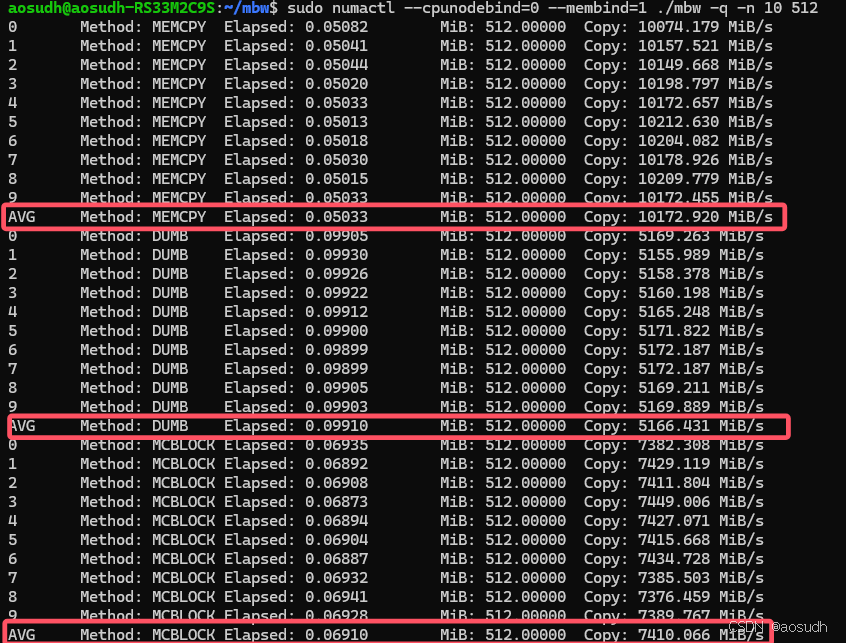

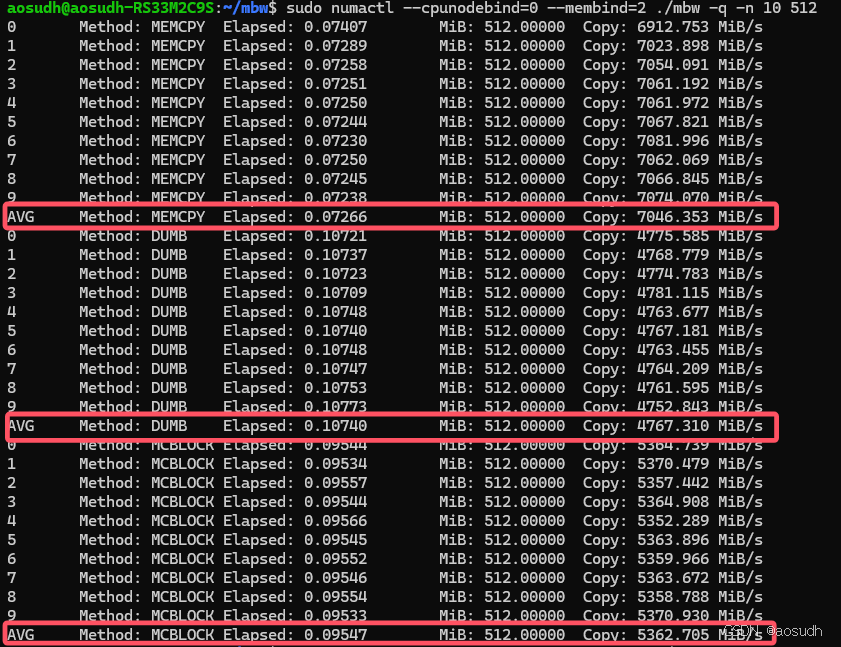

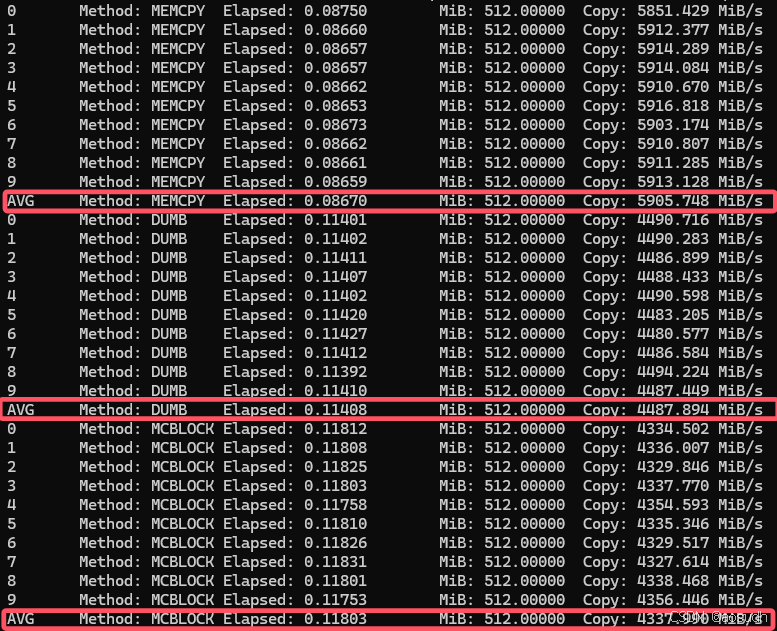

sudo numactl --cpunodebind=<cpu id> --membind=<numa node id> ./mbw -q -n 10 512可以得到

额外测试

该论文结果正在复现中

https://github.com/lingfenghsiang/Nomad

相关链接

https://www.youtube.com/watch?v=6a5NSMH-7hY

3155

3155

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?